ATXMEGA192D3-MH Atmel, ATXMEGA192D3-MH Datasheet

ATXMEGA192D3-MH

Specifications of ATXMEGA192D3-MH

Available stocks

Related parts for ATXMEGA192D3-MH

ATXMEGA192D3-MH Summary of contents

Page 1

... Board control Networking • • White Goods Optical ® ® TM AVR XMEGA Microcontroller 2 C and SMBus compatible) • Hand-held battery applications • Power tools • HVAC • Metering • Medical Applications 8/16-bit XMEGA D3 Microcontroller ATxmega256D3 ATxmega192D3 ATxmega128D3 ATxmega64D3 8134I–AVR–12/10 ...

Page 2

... ATxmega256D3-AU 256K + 8K ATxmega192D3-AU 192K + 8K ATxmega128D3-AU 128K + 8K ATxmega64D3-AU 64K + 4K ATxmega256D3-MH 256K + 8K ATxmega192D3-MH 192K + 8K ATxmega128D3-MH 128K + 8K ATxmega64D3-MH 64K + 4K Notes: 1. This device can also be supplied in wafer form. Please contact your local Atmel sales office for detailed ordering information. 2. Pb-free packaging, complies to the European Directive for Restriction of Hazardous Substances (RoHS directive). Also Halide free and fully Green. ...

Page 3

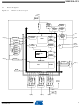

Pinout/ Block Diagram Figure 2-1. Block diagram and pinout INDEX CORNER PA3 PA4 PA5 PA6 PA7 PB0 PB1 PB2 PB3 PB4 PB5 PB6 PB7 GND VCC PC0 Notes: 1. For full details on pinout and alternate pin functions refer ...

Page 4

... Bootloader software in the Boot Flash section will continue to run while the Application Flash section is updated, providing true Read-While-Write operation. By combining an 8/16-bit RISC CPU with In-System Self-Programmable Flash, the Atmel XMEGA powerful microcon- troller family that provides a highly flexible and cost effective solution for many embedded applications ...

Page 5

Block Diagram Figure 3-1. XMEGA D3 Block Diagram PA[0..7] PORT A (8) ACA ADCA AREFA VCC/10 Int. Refs. Tempref AREFB PB[0..7] PORT B (8) IRCOM 8134I–AVR–12/10 PR[0..1] XTAL1 XTAL2 Oscillator Circuits/ Clock Generation DATA BUS Event System Oscillator Controller ...

Page 6

... The XMEGA application notes contain example code and show applied use of the modules and peripherals. The XMEGA Manual and Application Notes are available from http://www.atmel.com/avr. 5. Disclaimer For devices that are not available yet, typical values contained in this datasheet are based on simulations and characterization of other AVR XMEGA microcontrollers manufactured on the same process technology ...

Page 7

... Support for 8-, 16- and 32-bit Arithmetic • Configuration Change Protection of system critical features 6.2 Overview The Atmel is to ensure correct program execution. The CPU must therefore be able to access memories, perform calculations and control peripherals. Interrupt handling is described in a separate sec- tion. Figure 6-1 on page 7 Figure 6-1 ...

Page 8

This concept enables instructions to be executed in every clock cycle. The program memory is In-System Re-programmable Flash memory. 6.3 Register File The fast-access Register File contains 32 x 8-bit general purpose working registers with a single clock cycle access ...

Page 9

Memories 7.1 Features • Flash Program Memory – One linear address space – In-System Programmable – Self-Programming and Bootloader support – Application Section for application code – Application Table Section for application code or data storage – Boot Section ...

Page 10

Memory (SPM) instruction must reside in the Boot Section when used to write to the Flash memory. A third section inside the Application section is referred to as the Application Table section which has separate Lock bits for storage ...

Page 11

... The Data Memory consist of the I/O Memory, EEPROM and SRAM memories, all within one lin- ear address space, see devices in the family is identical and with empty, reserved memory space for smaller devices. Figure 7-2. Data Memory Map (Hexadecimal address) Byte Address ATxmega192D3 0 I/O Registers (4KB) FFF 1000 ...

Page 12

I/O Memory All peripherals and modules are addressable through I/O memory locations in the data memory space. All I/O memory locations can be accessed by the Load (LD/LDS/LDD) and Store (ST/STS/STD) instructions, transferring data between the 32 general purpose ...

Page 13

... Chip Erase commands that erase the Flash, and requires a dedicated erase command. This ensures parameter storage during multiple program/erase session and on-chip debug sessions. 8134I–AVR–12/10 Table 7-1 on page Device ID bytes for XMEGA D3 devices. Device Byte 2 ATxmega64D3 ATxmega128D3 ATxmega192D3 ATxmega256D3 XMEGA D3 13. The serial number consist of Device ID bytes Byte ...

Page 14

... Table 7-3. Devices EEPROM Size (Bytes) ATxmega64D3 2K ATxmega128D3 2K ATxmega192D3 2K ATxmega256D3 4K 8134I–AVR–12/10 shows the Flash Program Memory organization. Flash write and erase Number of words and Pages in the Flash. FWORD FPAGE (words) ...

Page 15

Event System 8.1 Features • Inter-peripheral communication and signalling with minimum latency • CPU independent operation • 4 Event Channels allows for signals to be routed at the same time • Events can be generated by ...

Page 16

Figure 8-1. The Event Routing Network can directly connect together ADCs, Analog Comparators (AC), I/O ports (PORTx), the Real-time Counter (RTC), Timer/Counters (T/C) and the IR Communica- tion Module (IRCOM). Events can also be generated from software (CPU). All events ...

Page 17

System Clock and Clock options 9.1 Features • Fast start-up time • Safe run-time clock switching • Internal Oscillators: – 32 MHz run-time calibrated RC oscillator – 2 MHz run-time calibrated RC oscillator – 32.768 kHz calibrated RC oscillator ...

Page 18

Figure 9-1. Internal Oscillator Calibrated Internal Run-Time Calibrated Internal Oscillator Run-time Calibrated Internal Oscillator Each clock source is briefly described in the following sub-sections. 9.3 Clock Options 9.3.1 32 kHz Ultra Low Power Internal Oscillator The 32 kHz Ultra Low ...

Page 19

Crystal Oscillator The 32.768 kHz Crystal Oscillator is a low power driver for an external watch crystal. It can be used as system clock source or as asynchronous clock source for the Real Time Counter. 9.3.4 0.4 ...

Page 20

Power Management and Sleep Modes 10.1 Features • 5 sleep modes – Idle – Power-down – Power-save – Standby – Extended standby • Power Reduction registers to disable clocks to unused peripherals 10.2 Overview The XMEGA D3 provides various ...

Page 21

Extended Standby Mode Extended Standby mode is identical to Power-save mode with the exception that all enabled system clock sources are kept running while the CPU and Peripheral clocks are stopped. This reduces the wake-up time when external crystals ...

Page 22

System Control and Reset 11.1 Features • Multiple reset sources for safe operation and device reset – Power-On Reset – External Reset – Watchdog Reset – Brown-Out Reset – PDI reset – Software reset • Asynchronous reset – No ...

Page 23

Software reset The MCU can be reset by the CPU writing to a special I/O register through a timed sequence. 12. WDT - Watchdog Timer 12.1 Features • 11 selectable timeout periods, from 8s. • Two ...

Page 24

PMIC - Programmable Multi-level Interrupt Controller 13.1 Features • Separate interrupt vector for each interrupt • Short, predictable interrupt response time • Programmable Multi-level Interrupt Controller – 3 programmable interrupt levels – Selectable priority scheme within low level interrupts ...

Page 25

Table 13-1. Reset and Interrupt Vectors (Continued) Program Address (Base Address) Source 0x05A TWIE_INT_base 0x05E TCE0_INT_base 0x074 USARTE0_INT_base 0x080 PORTD_INT_base 0x084 PORTA_INT_base 0x088 ACA_INT_base 0x08E ADCA_INT_base 0x09A TCD0_INT_base 0x0AE SPID_INT_vector 0x0B0 USARTD0_INT_base 0x0D0 PORTF_INT_base 0x0D8 TCF0_INT_base 8134I–AVR–12/10 Interrupt Description Two-Wire ...

Page 26

I/O Ports 14.1 Features • Selectable input and output configuration for each pin individually • Flexible pin configuration through dedicated Pin Configuration Register • Synchronous and/or asynchronous input sensing with port interrupts and events – Sense both edges – ...

Page 27

Push-pull Figure 14-1. I/O configuration - Totem-pole 14.3.2 Pull-down Figure 14-2. I/O configuration - Totem-pole with pull-down (on input) 14.3.3 Pull-up Figure 14-3. I/O configuration - Totem-pole with pull-up (on input) 14.3.4 Bus-keeper The bus-keeper’s weak output produces the ...

Page 28

Figure 14-4. I/O configuration - Totem-pole with bus-keeper 14.3.5 Others Figure 14-5. Output configuration - Wired-OR with optional pull-down Figure 14-6. I/O configuration - Wired-AND with optional pull-up 8134I–AVR–12/10 DIRn OUTn INn OUTn INn INn OUTn XMEGA ...

Page 29

Input sensing • Sense both edges • Sense rising edges • Sense falling edges • Sense low level Input sensing is synchronous or asynchronous depending on the enabled clock for the ports, and the configuration is shown in Figure ...

Page 30

T/C - 16-bits Timer/Counter with PWM 15.1 Features • Five 16-bit Timer/Counters – Four Timer/Counters of type 0 – One Timer/Counters of type 1 • Four Compare or Capture (CC) Channels in Timer/Counter 0 • Two Compare or Capture ...

Page 31

Figure 15-1. Overview of a Timer/Counter and closely related peripherals Timer/Counter Base Counter Timer Period Compare/Capture Channel B Compare/Capture Channel A Comparator The Hi-Resolution Extension can be enabled to increase the waveform generation resolution by 2 bits (4x). This is ...

Page 32

AWEX - Advanced Waveform Extension 16.1 Features • Output with complementary output from each Capture channel • Four Dead Time Insertion (DTI) Units, one for each Capture channel • 8-bit DTI Resolution • Separate High and Low Side Dead-Time ...

Page 33

Hi-Res - High Resolution Extension 17.1 Features • Increases Waveform Generator resolution by 2-bits (4x) • Supports Frequency, single- and dual-slope PWM operation • Supports the AWEX when this is enabled and used for the same Timer/Counter 17.2 Overview ...

Page 34

RTC - Real-Time Counter 18.1 Features • 16-bit Timer • Flexible Tick resolution ranging from 32.768 kHz • One Compare register • One Period register • Clear timer on Overflow or Compare Match • Overflow or ...

Page 35

TWI - Two Wire Interface 19.1 Features • Two Identical TWI peripherals • Simple yet Powerful and Flexible Communication Interface • Both Master and Slave Operation Supported • Device can Operate as Transmitter or Receiver • 7-bit Address Space ...

Page 36

SPI - Serial Peripheral Interface 20.1 Features • Two Identical SPI peripherals • Full-duplex, Three-wire Synchronous Data Transfer • Master or Slave Operation • LSB First or MSB First Data Transfer • Seven Programmable Bit Rates • End of ...

Page 37

USART 21.1 Features • Three Identical USART peripherals • Full Duplex Operation (Independent Serial Receive and Transmit Registers) • Asynchronous or Synchronous Operation • Master or Slave Clocked Synchronous Operation • High-resolution Arithmetic Baud Rate Generator • Supports Serial ...

Page 38

IRCOM - IR Communication Module 22.1 Features • Pulse modulation/demodulation for infrared communication • Compatible to IrDA 1.4 physical for baud rates up to 115.2 kbps • Selectable pulse modulation scheme – 3/16 of baud rate period – Fixed ...

Page 39

ADC - 12-bit Analog to Digital Converter 23.1 Features • One ADC with 12-bit resolution • 200 ksps sample rate • Signed and Unsigned conversions • 16 single ended inputs • 8x4 differential inputs • 3 internal inputs: – ...

Page 40

Figure 23-1. ADC overview The ADC may be configured for 8- or 12-bit result, reducing the minimum conversion time (prop- agation delay) from 0.5 µs for 12-bit to 3.7 µs for 8-bit result. ADC conversion results are provided left- or ...

Page 41

AC - Analog Comparator 24.1 Features • Two Analog Comparators • Selectable hysteresis – No, Small or Large • Analog Comparator output available on pin • Flexible Input Selection – All pins on the port – Bandgap reference voltage. ...

Page 42

Figure 24-1. Analog comparator overview Pin inputs Internal inputs Pin inputs Internal inputs VCC scaled Pin inputs Internal inputs Pin inputs Internal inputs VCC scaled 8134I–AVR–12/10 XMEGA D3 + Pin 0 output AC0 - Interrupts Interrupt sensitivity control + AC1 ...

Page 43

Input Selection The Analog comparators have a very flexible input selection and the two comparators grouped in a pair may be used to realize a window function. One pair of analog comparators is shown in Figure 24-1 on page ...

Page 44

... No limitation on debug/programming clock frequency versus system clock frequency 25.2 Overview The XMEGA D3 has a powerful On-Chip Debug (OCD) system that - in combination with Atmel’s development tools - provides all the necessary functions to debug an application. It has support for program and data breakpoints, and can debug an application from C and high level language source code level, as well as assembler and disassembler level ...

Page 45

... The programming and debug facilities are accessed through the PDI interface. The PDI physical interface uses one dedicated pin together with the Reset pin, and no general purpose pins are used. The PDI is an Atmel proprietary protocol for communication between the microcontroller and Atmel’s or third party development tools. 8134I–AVR–12/10 ...

Page 46

Pinout and Pin Functions The pinout of XMEGA D3 is shown in pin may have several function. This will depend on which peripheral is enabled and connected to the actual pin. Only one of the alternate pin functions can ...

Page 47

Communication functions SCL SDA SCLIN SCLOUT SDAIN SDAOUT XCKn RXDn TXDn SS MOSI MISO SCK 27.1.6 Oscillators, Clock and Event TOSCn XTALn CLKOUT EVOUT 27.1.7 Debug/System functions RESET PDI_CLK PDI_DATA 8134I–AVR–12/10 Serial Clock for TWI Serial Data for TWI ...

Page 48

Alternate Pin Functions The tables below show the main and alternate pin functions for all pins on each port. They also show which peripheral that makes use of or enables the alternate pin function. Table 27-1. Port A - ...

Page 49

Table 27-3. Port C - Alternate functions PORT C PIN # INTERRUPT TCC0 PC0 16 SYNC OC0A PC1 17 SYNC OC0B PC2 18 SYNC/ASYNC OC0C PC3 19 SYNC OC0D PC4 20 SYNC PC5 21 SYNC PC6 22 SYNC PC7 23 ...

Page 50

Table 27-6. Port F - Alternate functions PORT F PIN # INTERRUPT PF0 46 SYNC PF1 47 SYNC PF2 48 SYNC/ASYNC PF3 49 SYNC PF4 50 SYNC PF5 51 SYNC PF6 54 SYNC PF7 55 SYNC GND 52 VCC 53 ...

Page 51

Peripheral Module Address Map The address maps show the base address for each peripheral and module in XMEGA D3. For complete register description and summary for each peripheral module, refer to the XMEGA A Manual. Table 28-1. Base Address ...

Page 52

Instruction Set Summary Mnemonics Operands Description ADD Rd, Rr Add without Carry ADC Rd, Rr Add with Carry ADIW Rd, K Add Immediate to Word SUB Rd, Rr Subtract without Carry SUBI Rd, K Subtract Immediate SBC Rd, Rr ...

Page 53

Mnemonics Operands Description RET Subroutine Return RETI Interrupt Return CPSE Rd,Rr Compare, Skip if Equal CP Rd,Rr Compare CPC Rd,Rr Compare with Carry CPI Rd,K Compare with Immediate SBRC Rr, b Skip if Bit in Register Cleared SBRS Rr, b ...

Page 54

Mnemonics Operands Description LD Rd, -Y Load Indirect and Pre-Decrement LDD Rd, Y+q Load Indirect with Displacement LD Rd, Z Load Indirect LD Rd, Z+ Load Indirect and Post-Increment LD Rd, -Z Load Indirect and Pre-Decrement LDD Rd, Z+q Load ...

Page 55

Mnemonics Operands Description ROL Rd Rotate Left Through Carry ROR Rd Rotate Right Through Carry ASR Rd Arithmetic Shift Right SWAP Rd Swap Nibbles BSET s Flag Set BCLR s Flag Clear SBI A, b Set Bit in I/O Register ...

Page 56

Electrical Characteristics All typical values are measured 25°C unless other temperature condition is given. All min- imum and maximum values are valid across operating temperature and voltage unless other conditions are given. 30.1 Absolute Maximum Ratings* ...

Page 57

Table 30-1. Current Consumption Symbol Parameter Power-save mode I CC Reset Current Consumption (2) Module current consumption RC32M RC32M w/DFLL RC2M RC2M w/DFLL RC32K PLL Watchdog normal mode BOD Continuous mode BOD Sampled mode I Internal 1.00 V ref CC ...

Page 58

Operating Voltage and Frequency Table 30-2. Symbol Clk The maximum CPU clock frequency of the XMEGA D3 devices is depending Figure 30-1 on page 58 Figure 30-1. Maximum Frequency vs. Vcc 8134I–AVR–12/10 Operating voltage and frequency ...

Page 59

Flash and EEPROM Memory Characteristics Table 30-3. Endurance and Data Retention Symbol Parameter Flash EEPROM Table 30-4. Programming time Symbol Parameter Chip Erase Flash EEPROM Notes: 1. Programming is timed from the internal 2 MHz oscillator. 2. EEPROM is ...

Page 60

ADC Characteristics Table 30-5. ADC Characteristics Symbol Parameter RES Resolution INL Integral Non-Linearity DNL Differential Non-Linearity Gain Error Offset Error ADC ADC Clock frequency clk Conversion rate Conversion time (propagation delay) Sampling Time Conversion range AVCC Analog Supply Voltage ...

Page 61

Analog Comparator Characteristics Table 30-7. Analog Comparator Characteristics Symbol Parameter V Input Offset Voltage off I Input Leakage Current lk V Hysteresis, No hys1 V Hysteresis, Small hys2 V Hysteresis, Large hys3 t Propagation delay delay 30.7 Bandgap Characteristics ...

Page 62

PAD Characteristics Table 30-10. PAD Characteristics Symbol Parameter V Input High Voltage IH V Input Low Voltage IL V Output Low Voltage GPIO OL V Output High Voltage GPIO OH I Input Leakage Current I/O pin IL I Input ...

Page 63

Oscillator Characteristics Table 30-13. Internal 32.768kHz Oscillator Characteristics Symbol Parameter Accuracy Table 30-14. Internal 2MHz Oscillator Characteristics Symbol Parameter Accuracy DFLL Calibration step size Table 30-15. Internal 32MHz Oscillator Characteristics Symbol Parameter Accuracy DFLL Calibration stepsize Table 30-16. Internal ...

Page 64

Figure 30-2. TOSC input capacitance The input capacitance between the TOSC pins is CL1 + CL2 in series as seen from the crystal when oscillating without external capacitors. Table 30-18. Device wake-up time from sleep Symbol Parameter Idle Sleep, Standby ...

Page 65

Typical Characteristics 31.1 Active Supply Current Figure 31-1. Active Supply Current vs. Frequency Figure 31-2. Active Supply Current vs. Frequency 8134I–AVR–12/ 1.0 MHz External clock 25°C SYS 900 800 700 600 500 400 ...

Page 66

Figure 31-3. Active Supply Current vs. Vcc Figure 31-4. Active Supply Current vs. VCC 8134I–AVR–12/ 1.0 MHz External Clock SYS 1000 900 800 700 600 500 400 300 200 100 0 1.6 1.8 2 2.2 2 ...

Page 67

Figure 31-5. Active Supply Current vs. Vcc Figure 31-6. Active Supply Current vs. Vcc 8134I–AVR–12/ 2.0 MHz internal RC SYS 2000 1800 1600 1400 1200 1000 800 600 400 200 0 1.6 1.8 2 2.2 2 ...

Page 68

Figure 31-7. Active Supply Current vs. Vcc 31.2 Idle Supply Current Figure 31-8. Idle Supply Current vs. Frequency 8134I–AVR–12/ MHz internal RC SYS 2.7 2.8 2 ...

Page 69

Figure 31-9. Idle Supply Current vs. Frequency Figure 31-10. Idle Supply Current vs. Vcc 8134I–AVR–12/ MHz 25°C SYS Frequency [MHz] ...

Page 70

Figure 31-11. Idle Supply Current vs. Vcc Figure 31-12. Idle Supply Current vs. Vcc 8134I–AVR–12/ 32.768 kHz internal RC SYS 1.6 1.8 2 2.2 2 2.0 MHz ...

Page 71

Figure 31-13. Idle Supply Current vs. Vcc Figure 31-14. Idle Supply Current vs. Vcc 8134I–AVR–12/ MHz internal RC prescaled to 8 MHz SYS 3.5 3.0 2.5 2.0 1.5 1.0 0.5 0 1.6 1.8 2 2.2 2.4 f ...

Page 72

Power-down Supply Current Figure 31-15. Power-down Supply Current vs. Temperature Figure 31-16. Power-down Supply Current vs. Temperature 8134I–AVR–12/10 2 1.8 1.6 1.4 1.2 1 0.8 0.6 0.4 0.2 0 -40 -30 -20 - Temperature [°C] With WDT ...

Page 73

Power-save Supply Current Figure 31-17. Power-save Supply Current vs. Temperature 31.5 Pin Pull-up Figure 31-18. Reset Pull-up Resistor Current vs. Reset Pin Voltage 8134I–AVR–12/10 With WDT, sampled BOD and RTC from ULP enabled 3 2.5 2 1.5 1 0.5 ...

Page 74

Figure 31-19. Reset Pull-up Resistor Current vs. Reset Pin Voltage Figure 31-20. Reset Pull-up Resistor Current vs. Reset Pin Voltage 8134I–AVR–12/ 3.0V CC 160 140 120 100 0 3.3V ...

Page 75

Pin Output Voltage vs. Sink/Source Current Figure 31-21. I/O Pin Output Voltage vs. Source Current Figure 31-22. I/O Pin Output Voltage vs. Source Current 8134I–AVR–12/10 Vcc = 1.8V 2 1.8 1.6 1.4 1.2 1 0.8 0.6 0.4 0.2 0 ...

Page 76

Figure 31-23. I/O Pin Output Voltage vs. Source Current Figure 31-24. I/O Pin Output Voltage vs. Sink Current 8134I–AVR–12/10 Vcc = 3.3V 3.5 3 2.5 2 1.5 1 0 Vcc = 1.8V 1.8 1.6 ...

Page 77

Figure 31-25. I/O Pin Output Voltage vs. Sink Current Figure 31-26. I/O Pin Output Voltage vs. Sink Current 8134I–AVR–12/10 Vcc = 3.0V 0.7 0.6 0.5 0.4 0.3 0.2 0 Vcc = 3.3V 0.7 0.6 ...

Page 78

Pin Thresholds and Hysteresis Figure 31-27. I/O Pin Input Threshold Voltage vs. V Figure 31-28. I/O Pin Input Threshold Voltage vs. V 8134I–AVR–12/ I/O Pin Read as “1” IH 2.5 2 1.5 1 0.5 0 1.6 1.8 ...

Page 79

Figure 31-29. I/O Pin Input Hysteresis vs. V Figure 31-30. Reset Input Threshold Voltage vs. V 8134I–AVR–12/10 0.7 0.6 0.5 0.4 0.3 0.2 0.1 0 1.6 1.8 2 2.2 2 I/O Pin Read as “1” IH 1.8 1.6 ...

Page 80

Figure 31-31. Reset Input Threshold Voltage vs. V 31.8 Bod Thresholds Figure 31-32. BOD Thresholds vs. Temperature 8134I–AVR–12/ I/O Pin Read as “0” IL 1.8 1.6 1.4 1.2 1 0.8 0.6 0.4 0.2 0 1.6 1.8 2 2.2 ...

Page 81

Figure 31-33. BOD Thresholds vs. Temperature 31.9 Oscillators and Wake-up Time 31.9.1 Internal 32.768 kHz Oscillator Figure 31-34. Internal 32.768 kHz Oscillator Calibration Step Size 8134I–AVR–12/10 BOD Level = 2.9V 3.06 3.04 3.02 3 2.98 2.96 2.94 2.92 2.9 -40 ...

Page 82

Internal 2 MHz Oscillator Figure 31-35. Internal 2 MHz Oscillator CALA Calibration Step Size -0.10 % -0.20 % -0.30 % Figure 31-36. Internal 2 MHz Oscillator CALB Calibration Step Size 8134I–AVR–12/10 ° - ...

Page 83

Internal 32 MHZ Oscillator Figure 31-37. Internal 32 MHz Oscillator CALA Calibration Step Size Figure 31-38. Internal 32 MHz Oscillator CALB Calibration Step Size 8134I–AVR–12/10 ° - 0.60 % 0.50 ...

Page 84

Module current consumption Figure 31-39. AC current consumption vs. Vcc Figure 31-40. Power-up current consumption vs. Vcc 8134I–AVR–12/10 Low-power Mode 120 100 1.6 1.8 2 2.2 2.4 700 600 500 400 300 200 100 ...

Page 85

Reset Pulsewidth Figure 31-41. Minimum Reset Pulse Width vs. Vcc 31.12 PDI Speed Figure 31-42. PDI Speed vs. Vcc 8134I–AVR–12/10 120 100 1.6 1.8 2 2.2 2 ...

Page 86

Packaging information 32.1 64A PIN 0°~7° Notes: 1.This package conforms to JEDEC reference MS-026, Variation AEB. 2. Dimensions D1 and E1 do not include mold protrusion. Allowable protrusion is 0.25 mm per side. Dimensions D1 and ...

Page 87

D Marked Pin TOP VIEW BOTTOM VIEW Notes: 1. JEDEC Standard MO-220, (SAW Singulation) Fig. 1, VMMD. 2. Dimension and tolerance conform to ASMEY14.5M-1994. 2325 Orchard Parkway San Jose, CA ...

Page 88

... Errata 33.1 ATxmega256D3, ATxmega192D3, ATxmega128D3, ATxmega64D3 33.1.1 rev. E • Bandgap voltage input for the ACs can not be changed when used for both ACs simultaneously • VCC voltage scaler for AC is non-linear • ADC gain stage cannot be used for single conversion • ...

Page 89

Figure 33-1. Analog Comparator Voltage Scaler vs. Scalefac Problem fix/Workaround Use external voltage input for the analog comparator if accurate voltage levels are needed 3. ADC gain stage cannot be used for single conversion The ADC gain stage will not ...

Page 90

Problem fix/Workaround Keep the amplified voltage output from the ADC gain stage below 2 order to get a cor- rect result, or keep ADC voltage reference below 2 ADC ...

Page 91

Problem fix/Workaround Table 33-1. PGM 11. PWM is not restarted properly after a fault in cycle-by-cycle mode When the AWeX fault restore mode is set to cycle-by-cycle, the waveform output will not return to normal operation ...

Page 92

NMI Flag for Crystal Oscillator Failure automatically cleared NMI flag for Crystal Oscillator Failure (XOSCFDIF) will be automatically cleared when exe- cuting the NMI interrupt handler. Problem fix/Workaround This device revision has only one NMI interrupt source, so checking ...

Page 93

Check for an pending address match interrupt */ if ( !(COMMS_TWI.SLAVE.STATUS & TWI_SLAVE_CLKHOLD_bm 22. TWI START condition at bus timeout will cause transaction to be dropped If Bus Timeout is enabled and a timeout ...

Page 94

B • Bandgap voltage input for the ACs can not be changed when used for both ACs simultaneously • VCC voltage scaler for AC is non-linear • ADC gain stage cannot be used for single conversion • ADC ...

Page 95

Figure 33-2. Analog Comparator Voltage Scaler vs. Scalefac Problem fix/Workaround Use external voltage input for the analog comparator if accurate voltage levels are needed 3. ADC gain stage cannot be used for single conversion The ADC gain stage will not ...

Page 96

Problem fix/Workaround Keep the amplified voltage output from the ADC gain stage below 2 order to get a cor- rect result, or keep ADC voltage reference below 2 ADC ...

Page 97

Problem fix/Workaround Table 33-2. PGM 11. PWM is not restarted properly after a fault in cycle-by-cycle mode When the AWeX fault restore mode is set to cycle-by-cycle, the waveform output will not return to normal operation ...

Page 98

NMI Flag for Crystal Oscillator Failure automatically cleared NMI flag for Crystal Oscillator Failure (XOSCFDIF) will be automatically cleared when exe- cuting the NMI interrupt handler. Problem fix/Workaround This device revision has only one NMI interrupt source, so checking ...

Page 99

Clearing TWI Stop Interrupt Flag may lock the bus If software clears the STOP Interrupt Flag (APIF) on the same Peripheral Clock cycle as the hardware sets this flag due to a new address received, CLKHOLD is not cleared ...

Page 100

TWIE is not available The TWI module on PORTE, TWIE is not available Problem fix/Workaround Use the identical TWI module on PORTC, TWIC instead. 33.1.3 All rev. A Not sampled. 8134I–AVR–12/10 XMEGA D3 100 ...

Page 101

... E” on page 88. Updated ERRATA for ADC (ADC has increased INL error for some operating conditions). Updated ERRATA ”rev. B” on page 94 Updated the last page by Atmel new Brand Style Guide. Updated ”Errata” on page 88. Updated the Footnote 3 of ”Ordering Information” on page All references to CRC removed ...

Page 102

34.5 8134E – 01/ 10. 34.6 8134D – 11/ 34.7 8134C – 10/ 34.8 8134B – 08/ ...

Page 103

Initial revision. XMEGA D3 103 ...

Page 104

Table of Contents Features ..................................................................................................... 1 Typical Applications ................................................................................ 1 1 Ordering Information ............................................................................... 2 2 Pinout/ Block Diagram ............................................................................. 3 3 Overview ................................................................................................... 4 4 Resources ................................................................................................. 6 5 Disclaimer ................................................................................................. 6 6 AVR CPU ................................................................................................... 7 7 Memories ...

Page 105

System Control and Reset .................................................................... 22 12 WDT - Watchdog Timer ......................................................................... 23 13 PMIC - Programmable Multi-level Interrupt Controller ....................... 24 14 I/O Ports .................................................................................................. 26 15 T/C - 16-bits Timer/Counter with PWM ................................................. 30 16 AWEX - ...

Page 106

TWI - Two Wire Interface ....................................................................... 35 20 SPI - Serial Peripheral Interface ............................................................ 36 21 USART ..................................................................................................... 37 22 IRCOM - IR Communication Module .................................................... 38 23 ADC - 12-bit Analog to Digital Converter ............................................. ...

Page 107

... Thresholds and Hysteresis ..............................................................................78 31.8Bod Thresholds .....................................................................................................80 31.9Oscillators and Wake-up Time ..............................................................................81 31.10Module current consumption ...............................................................................84 31.11Reset Pulsewidth .................................................................................................85 31.12PDI Speed ...........................................................................................................85 32.164A ........................................................................................................................86 32.264M2 .....................................................................................................................87 33.1ATxmega256D3, ATxmega192D3, ATxmega128D3, ATxmega64D3 ...................88 34.18134I – 12/10 ......................................................................................................101 34.28134H – 09/10 .....................................................................................................101 34.38134G – 08/10 .....................................................................................................101 34.48134F – 02/10 .....................................................................................................101 8134I–AVR–12/10 ...

Page 108

Table of Contents....................................................................................... i ...

Page 109

... Disclaimer: The information in this document is provided in connection with Atmel products. No license, express or implied, by estoppel or otherwise, to any intellectual property right is granted by this document or in connection with the sale of Atmel products. EXCEPT AS SET FORTH IN THE ATMEL TERMS AND CONDITIONS OF SALES LOCATED ON THE ATMEL WEBSITE, ATMEL ASSUMES NO LIABILITY WHATSOEVER AND DISCLAIMS ANY EXPRESS, IMPLIED OR STATUTORY WARRANTY RELATING TO ITS PRODUCTS INCLUDING, BUT NOT LIMITED TO, THE IMPLIED WARRANTY OF MERCHANTABILITY, FITNESS FOR A PARTICULAR PURPOSE, OR NON-INFRINGEMENT ...