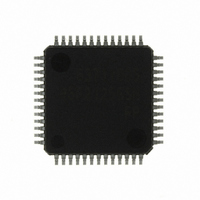

R5F21256SNFP#U0 Renesas Electronics America, R5F21256SNFP#U0 Datasheet - Page 283

R5F21256SNFP#U0

Manufacturer Part Number

R5F21256SNFP#U0

Description

IC R8C MCU FLASH 32K 52LQFP

Manufacturer

Renesas Electronics America

Series

R8C/2x/25r

Datasheets

1.R5F211A2SPU0.pdf

(300 pages)

2.R5F21246SDFPU0.pdf

(61 pages)

3.R5F21246SDFPU0.pdf

(527 pages)

Specifications of R5F21256SNFP#U0

Core Processor

R8C

Core Size

16/32-Bit

Speed

20MHz

Connectivity

I²C, LIN, SIO, SSU, UART/USART

Peripherals

POR, Voltage Detect, WDT

Number Of I /o

41

Program Memory Size

32KB (32K x 8)

Program Memory Type

FLASH

Ram Size

2K x 8

Voltage - Supply (vcc/vdd)

2.2 V ~ 5.5 V

Data Converters

A/D 12x10b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 85°C

Package / Case

52-LQFP

For Use With

R0K521256S000BE - KIT EVAL STARTER FOR R8C/25

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

R5F21256SNFP#U0R5F21256SNFP#ES

Manufacturer:

Renesas Electronics America

Quantity:

10 000

- Current page: 283 of 300

- Download datasheet (2Mb)

Rev.2.00 Oct 17, 2005

REJ09B0001-0200

Chapter 6

Figure 6.1.1 Starting a Read Instruction (without Software Wait States)

I n s t r u c t i o n s

u n d e r e x e c u t i o n

F e t c h c o d e

I n s t r u c t i o n

q u e u e b u f f e r

A d d r e s s b u s

D a t a b u s

D W : I n d i c a t e s a d a t a w r i t e .

D R : I n d i c a t e s a d a t a r e a d .

B C L K

P : I n d i c a t e s a p r e f e t c h ( r e a d i n g f r o m m e m o r y i n t o t h e i n s t r u c t i o n q u e u e b u f f e r ) .

C o n t e n t a t j u m p a d d r e s s i s

p r e f e t c h e d a t t h e s a m e t i m e

t h e i n s t r u c t i o n q u e u e b u f f e r

i s c l e a r e d .

R D

: I n d i c a t e s t h e l o c a t i o n s o f t h e i n s t r u c t i o n q u e u e b u f f e r t h a t a r e c l e a r .

WR

6 4

0 4

0 4

0 4

J u m p a d d r e s s

Calculating the Number of Cycles

0 C 0 6 5

04

04

04

JMP TEST_11

0 4

0 4

0 4

page 263 of 263

0 C 0 6 8

7 3

P

7 3

0 C 0 6 9

73

F 1

P

F 1

Fetch

0 C 0 6 A

7 3

F 1

0 0

0 0

P

0 C 0 6 B

Low-order address from

which to read data

7 3 F 1

0 0

40

P

4 0

C o n t e n t a t a d d r e s s 4 0 0 0

0 C 0 6 C

0 0

64

4 0

64

P

F e t c h

0 C 0 6 D

0 0

64

4 0

0 4

MOV.W

0 4

P

04000

0040

64

0 4

DR

AA

1 6

04001

6 4

04

AA

D R

F e t c h

H i g h - o r d e r a d d r e s s f r o m

w h i c h t o r e a d d a t a

0 C 0 6 E

Content at address 4001

64

0 4

0 4

0 4

P

0 4

6 4

0 4

0 4

Content at jump address is prefetched

at the same time the instruction queue

buffer is cleared.

04

P

0C06F

04

04

0 4

JMP TEST_12

16

04

04

04

0C072

73

73

P

0 C 0 7 3

7 3

F F

F F

P

0 C 0 7 4

FF

73

0 0

6.1 Instruction Queue Buffer

0 0

P

S a m p l e p r o g r a m s

A d d r e s s

0 C 0 6 2

0 C 0 6 3

0 C 0 6 4

0 C 0 6 5

0 C 0 6 6

0 C 0 6 7

0 C 0 6 8

0 C 0 6 8

0 C 0 6 C

0 C 0 6 D

0 C 0 6 E

0 C 0 6 F

0 C 0 7 0

0 C 0 7 1

0 C 0 7 2

C o d e

6 4

0 4

0 4

0 4

0 4

0 4

7 3 F 1 0 0 4 0

6 4

0 4

0 4

0 4

0 4

0 4

T E S T _ 1 1 :

T E S T _ 1 2 :

I n s t r u c t i o n

N O P

J M P

N O P

N O P

N O P

N O P

M O V . W 0 4 0 0 0 h , R 1

J M P

N O P

N O P

N O P

N O P

N O P

T E S T _ 1 1

T E S T _ 1 2

Related parts for R5F21256SNFP#U0

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

KIT STARTER FOR M16C/29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/2D

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

R0K33062P STARTER KIT

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/23 E8A

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C/25

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER H8S2456 SHARPE DSPLY

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C38C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8C35C

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R8CL3AC+LCD APPS

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR RX610

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR R32C/118

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV RSK-R8C/26-29

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR SH7124

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT STARTER FOR H8SX/1622

Manufacturer:

Renesas Electronics America

Datasheet:

Part Number:

Description:

KIT DEV FOR SH7203

Manufacturer:

Renesas Electronics America

Datasheet: