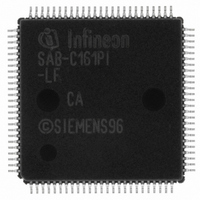

SAB-C161PI-LF CA Infineon Technologies, SAB-C161PI-LF CA Datasheet - Page 23

SAB-C161PI-LF CA

Manufacturer Part Number

SAB-C161PI-LF CA

Description

IC MICROCONTROLLER 16BIT 100TQFP

Manufacturer

Infineon Technologies

Series

C16xxr

Datasheet

1.SAF-C161PI-LM_CA.pdf

(82 pages)

Specifications of SAB-C161PI-LF CA

Core Processor

C166

Core Size

16-Bit

Speed

20MHz

Connectivity

EBI/EMI, I²C, SPI, UART/USART

Peripherals

POR, PWM, WDT

Number Of I /o

76

Program Memory Type

ROMless

Ram Size

3K x 8

Voltage - Supply (vcc/vdd)

4.5 V ~ 5.5 V

Data Converters

A/D 4x10b

Oscillator Type

Internal

Operating Temperature

0°C ~ 70°C

Package / Case

100-LFQFP

Packages

PG-TQFP-100

Max Clock Frequency

20.0 MHz

Sram (incl. Cache)

3.0 KByte

A / D Input Lines (incl. Fadc)

4

Program Memory

0.0 KByte

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Program Memory Size

-

Other names

B161PILFCAXT

SAB-C161PI-LF CA

SAB-C161PI-LFCAINTR

SABC161PILFCAXT

SP000014344

SAB-C161PI-LF CA

SAB-C161PI-LFCAINTR

SABC161PILFCAXT

SP000014344

&3,

General Purpose Timer (GPT) Unit

The GPT unit represents a very flexible multifunctional timer/counter structure which

may be used for many different time related tasks such as event timing and counting,

pulse width and duty cycle measurements, pulse generation, or pulse multiplication.

The GPT unit incorporates five 16-bit timers which are organized in two separate

modules, GPT1 and GPT2. Each timer in each module may operate independently in a

number of different modes, or may be concatenated with another timer of the same

module.

Each of the three timers T2, T3, T4 of module GPT1 can be configured individually for

one of four basic modes of operation, which are Timer, Gated Timer, Counter, and

Incremental Interface Mode. In Timer Mode, the input clock for a timer is derived from

the CPU clock, divided by a programmable prescaler, while Counter Mode allows a timer

to be clocked in reference to external events.

Pulse width or duty cycle measurement is supported in Gated Timer Mode, where the

operation of a timer is controlled by the ‘gate’ level on an external input pin. For these

purposes, each timer has one associated port pin (TxIN) which serves as gate or clock

input. The maximum resolution of the timers in module GPT1 is 16 TCL.

The count direction (up/down) for each timer is programmable by software or may

additionally be altered dynamically by an external signal on a port pin (TxEUD) to

facilitate eg. position tracking.

In Incremental Interface Mode the GPT1 timers (T2, T3, T4) can be directly connected

to the incremental position sensor signals A and B via their respective inputs TxIN and

TxEUD. Direction and count signals are internally derived from these two input signals,

so the contents of the respective timer Tx corresponds to the sensor position. The third

position sensor signal TOP0 can be connected to an interrupt input.

Timer T3 has an output toggle latch (T3OTL) which changes its state on each timer over-

flow/underflow. The state of this latch may be output on a port pin (T3OUT) eg. for time

out monitoring of external hardware components, or may be used internally to clock

timers T2 and T4 for measuring long time periods with high resolution.

In addition to their basic operating modes, timers T2 and T4 may be configured as reload

or capture registers for timer T3. When used as capture or reload registers, timers T2

and T4 are stopped. The contents of timer T3 are captured into T2 or T4 in response to

a signal at their associated input pins (TxIN). Timer T3 is reloaded with the contents of

T2 or T4 triggered either by an external signal or by a selectable state transition of its

toggle latch T3OTL. When both T2 and T4 are configured to alternately reload T3 on

opposite state transitions of T3OTL with the low and high times of a PWM signal, this

signal can be constantly generated without software intervention.

Data Sheet

21

1999-07