ST62T65CB6 STMicroelectronics, ST62T65CB6 Datasheet - Page 16

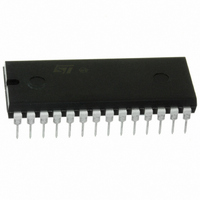

ST62T65CB6

Manufacturer Part Number

ST62T65CB6

Description

IC MCU 8BIT W/ADC 28-PDIP

Manufacturer

STMicroelectronics

Series

ST6r

Datasheet

1.ST62T55CB6.pdf

(84 pages)

Specifications of ST62T65CB6

Core Processor

ST6

Core Size

8-Bit

Speed

8MHz

Connectivity

SPI

Peripherals

LED, LVD, POR, WDT

Number Of I /o

21

Program Memory Size

3.8KB (3.8K x 8)

Program Memory Type

OTP

Eeprom Size

128 x 8

Ram Size

128 x 8

Voltage - Supply (vcc/vdd)

3 V ~ 6 V

Data Converters

A/D 13x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

28-DIP (0.600", 15.24mm)

Processor Series

ST62T6x

Core

ST6

Data Bus Width

8 bit

Data Ram Size

128 B

Interface Type

SCI

Maximum Clock Frequency

8 MHz

Number Of Programmable I/os

21

Number Of Timers

1

Operating Supply Voltage

3 V to 6 V

Maximum Operating Temperature

+ 125 C

Mounting Style

Through Hole

Development Tools By Supplier

ST62GP-EMU2, ST62E2XC-EPB/110, ST62E6XC-EPB/US, STREALIZER-II

Minimum Operating Temperature

- 40 C

On-chip Adc

8 bit

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ST62T65CB6

Manufacturer:

BOURNS

Quantity:

12 000

ST6255C ST6265C ST6265B

CPU REGISTERS (Cont’d)

However, if the program space contains more than

4096 bytes, the additional memory in program

space can be addressed by using the Program

Bank Switch register.

The PC value is incremented after reading the ad-

dress of the current instruction. To execute relative

jumps, the PC and the offset are shifted through

the ALU, where they are added; the result is then

shifted back into the PC. The program counter can

be changed in the following ways:

Flags (C, Z). The ST6 CPU includes three pairs of

flags (Carry and Zero), each pair being associated

with one of the three normal modes of operation:

Normal mode, Interrupt mode and Non Maskable

Interrupt mode. Each pair consists of a CARRY

flag and a ZERO flag. One pair (CN, ZN) is used

during Normal operation, another pair is used dur-

ing Interrupt mode (CI, ZI), and a third pair is used

in the Non Maskable Interrupt mode (CNMI, ZN-

MI).

The ST6 CPU uses the pair of flags associated

with the current mode: as soon as an interrupt (or

a Non Maskable Interrupt) is generated, the ST6

CPU uses the Interrupt flags (resp. the NMI flags)

instead of the Normal flags. When the RETI in-

struction is executed, the previously used set of

flags is restored. It should be noted that each flag

set can only be addressed in its own context (Non

Maskable Interrupt, Normal Interrupt or Main rou-

tine). The flags are not cleared during context

switching and thus retain their status.

The Carry flag is set when a carry or a borrow oc-

curs during arithmetic operations; otherwise it is

cleared. The Carry flag is also set to the value of

the bit tested in a bit test instruction; it also partici-

pates in the rotate left instruction.

The Zero flag is set if the result of the last arithme-

tic or logical operation was equal to zero; other-

wise it is cleared.

Switching between the three sets of flags is per-

formed automatically when an NMI, an interrupt or

a RETI instructions occurs. As the NMI mode is

16/84

- JP (Jump) instruction

- CALL instruction

- Relative Branch Instruction.PC= PC +/- offset

- Interrupt

- Reset

- RET & RETI instructions PC= Pop (stack)

- Normal instruction

PC=Interrupt vector

PC= Reset vector

PC= PC + 1

PC=Jump address

PC= Call address

automatically selected after the reset of the MCU,

the ST6 core uses at first the NMI flags.

Stack. The ST6 CPU includes a true LIFO hard-

ware stack which eliminates the need for a stack

pointer. The stack consists of six separate 12-bit

RAM locations that do not belong to the data

space RAM area. When a subroutine call (or inter-

rupt request) occurs, the contents of each level are

shifted into the next higher level, while the content

of the PC is shifted into the first level (the original

contents of the sixth stack level are lost). When a

subroutine or interrupt return occurs (RET or RETI

instructions), the first level register is shifted back

into the PC and the value of each level is popped

back into the previous level. Since the accumula-

tor, in common with all other data space registers,

is not stored in this stack, management of these

registers should be performed within the subrou-

tine. The stack will remain in its “deepest” position

if more than 6 nested calls or interrupts are execut-

ed, and consequently the last return address will

be lost. It will also remain in its highest position if

the stack is empty and a RET or RETI is executed.

In this case the next instruction will be executed.

Figure 7. ST6 CPU Programming Mode

l

REGISTER

NORMAL FLAGS

INTERRUPT FLAGS

NMI FLAGS

INDEX

b11

STACK REGISTER

PROGRAM COUNTER

b 7

b 7

b 7

b 7

b 7

SIX LEVELS

ACCUMULATOR

Y REG. POINTER

X REG. POINTER

W REGISTER

V REGISTER

C

C

C

b0

b0

b0

b0

b0

b0

Z

Z

Z

ADDRESSING

VA000423

DIRECT

SHORT

MODE