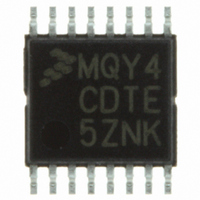

MC68HC908QY4CDTE Freescale Semiconductor, MC68HC908QY4CDTE Datasheet - Page 144

MC68HC908QY4CDTE

Manufacturer Part Number

MC68HC908QY4CDTE

Description

IC MCU 4K FLASH W/ADC 16-TSSOP

Manufacturer

Freescale Semiconductor

Series

HC08r

Datasheet

1.MC908QY4MDWER.pdf

(184 pages)

Specifications of MC68HC908QY4CDTE

Core Processor

HC08

Core Size

8-Bit

Speed

8MHz

Peripherals

LVD, POR, PWM

Number Of I /o

13

Program Memory Size

4KB (4K x 8)

Program Memory Type

FLASH

Ram Size

128 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Data Converters

A/D 4x8b

Oscillator Type

Internal

Operating Temperature

-40°C ~ 85°C

Package / Case

16-TSSOP

Processor Series

HC08Q

Core

HC08

Data Bus Width

8 bit

Data Ram Size

128 B

Maximum Clock Frequency

8 MHz

Number Of Programmable I/os

14

Number Of Timers

2

Maximum Operating Temperature

+ 85 C

Mounting Style

SMD/SMT

Development Tools By Supplier

FSICEBASE, M68CBL05AE, DEMO908QB8, DEMO908QC16

Minimum Operating Temperature

- 40 C

On-chip Adc

8 bit, 4 Channel

Controller Family/series

HC08

No. Of I/o's

14

Ram Memory Size

128Byte

Cpu Speed

8MHz

No. Of Timers

1

Rohs Compliant

Yes

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Connectivity

-

Lead Free Status / Rohs Status

Details

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC68HC908QY4CDTE

Manufacturer:

Freescale Semiconductor

Quantity:

135

Development Support

15.3.1.4 Data Format

Communication with the monitor ROM is in standard non-return-to-zero (NRZ) mark/space data format.

Transmit and receive baud rates must be identical.

15.3.1.5 Break Signal

A start bit (logic 0) followed by nine logic 0 bits is a break signal. When the monitor receives a break signal,

it drives the PTA0 pin high for the duration of two bits and then echoes back the break signal.

15.3.1.6 Baud Rate

The monitor communication baud rate is controlled by the frequency of the external or internal oscillator

and the state of the appropriate pins as shown in

Table 15-1

bus frequency divided by 256 when using an external oscillator. When using the internal oscillator in

forced monitor mode, the effective baud rate is the bus frequency divided by 335.

15.3.1.7 Commands

The monitor ROM firmware uses these commands:

144

•

•

•

•

•

•

READ (read memory)

WRITE (write memory)

IREAD (indexed read)

IWRITE (indexed write)

READSP (read stack pointer)

RUN (run user program)

also lists the bus frequencies to achieve standard baud rates. The effective baud rate is the

User

Monitor

Modes

START

BIT

Vector High

0

$FFFE

$FEFE

Reset

BIT 0

1

2

BIT 1

MISSING STOP BIT

3

MC68HC908QY/QT Family Data Sheet, Rev. 6

Vector Low

Figure 15-13. Monitor Data Format

Figure 15-14. Break Transaction

$FFFF

$FEFF

4

Reset

BIT 2

Table 15-2. Mode Difference

5

6

BIT 3

Vector High

7

$FEFC

$FFFC

Break

BIT 4

Table

Functions

BIT 5

15-1.

Vector Low

2-STOP BIT DELAY BEFORE ZERO ECHO

$FFFD

$FEFD

Break

BIT 6

0

1

BIT 7

2

Vector High

$FEFC

$FFFC

3

STOP

SWI

BIT

4

START

NEXT

5

BIT

6

Vector Low

Freescale Semiconductor

$FFFD

$FEFD

SWI

7