R5F212BASNFA#U0 Renesas Electronics America, R5F212BASNFA#U0 Datasheet - Page 20

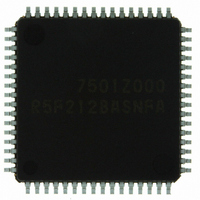

R5F212BASNFA#U0

Manufacturer Part Number

R5F212BASNFA#U0

Description

IC R8C/2B MCU FLASH 96+2K 64LQFP

Manufacturer

Renesas Electronics America

Series

R8C/2x/2Br

Datasheet

1.R5F212B7SNFPU0.pdf

(66 pages)

Specifications of R5F212BASNFA#U0

Core Processor

R8C

Core Size

16/32-Bit

Speed

20MHz

Connectivity

I²C, LIN, SIO, SSU, UART/USART

Peripherals

POR, PWM, Voltage Detect, WDT

Number Of I /o

55

Program Memory Size

96KB (96K x 8)

Program Memory Type

FLASH

Ram Size

7K x 8

Voltage - Supply (vcc/vdd)

2.2 V ~ 5.5 V

Data Converters

A/D 12x10b; D/A 2x8b

Oscillator Type

Internal

Operating Temperature

-20°C ~ 85°C

Package / Case

64-LQFP

For Use With

R0K5212D8S001BE - KIT STARTER FOR R8C/2DR0K5212D8S000BE - KIT DEV FOR R8C/2D

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Eeprom Size

-

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

R5F212BASNFA#U0R5F212BASNFA#V2

Manufacturer:

Renesas Electronics America

Quantity:

10 000

R8C/2A Group, R8C/2B Group

Rev.2.10

REJ03B0182-0210

2.1

2.2

2.3

2.4

2.5

2.6

2.7

2.8

2.8.1

2.8.2

2.8.3

2.8.4

2.8.5

2.8.6

R0 is a 16-bit register for transfer, arithmetic, and logic operations. The same applies to R1 to R3. R0 can be split

into high-order bits (R0H) and low-order bits (R0L) to be used separately as 8-bit data registers. R1H and R1L are

analogous to R0H and R0L. R2 can be combined with R0 and used as a 32-bit data register (R2R0). R3R1 is

analogous to R2R0.

A0 is a 16-bit register for address register indirect addressing and address register relative addressing. It is also

used for transfer, arithmetic, and logic operations. A1 is analogous to A0. A1 can be combined with A0 and as a 32-

bit address register (A1A0).

FB is a 16-bit register for FB relative addressing.

INTB is a 20-bit register that indicates the start address of an interrupt vector table.

PC is 20 bits wide and indicates the address of the next instruction to be executed.

The stack pointers (SP), USP, and ISP, are each 16 bits wide. The U flag of FLG is used to switch between

USP and ISP.

SB is a 16-bit register for SB relative addressing.

FLG is an 11-bit register indicating the CPU state.

The C flag retains carry, borrow, or shift-out bits that have been generated by the arithmetic and logic unit.

The D flag is for debugging only. Set it to 0.

The Z flag is set to 1 when an arithmetic operation results in 0; otherwise to 0.

The S flag is set to 1 when an arithmetic operation results in a negative value; otherwise to 0.

Register bank 0 is selected when the B flag is 0. Register bank 1 is selected when this flag is set to 1.

The O flag is set to 1 when an operation results in an overflow; otherwise to 0.

Data Registers (R0, R1, R2, and R3)

Address Registers (A0 and A1)

Frame Base Register (FB)

Interrupt Table Register (INTB)

Program Counter (PC)

User Stack Pointer (USP) and Interrupt Stack Pointer (ISP)

Static Base Register (SB)

Flag Register (FLG)

Nov 26, 2007

Carry Flag (C)

Debug Flag (D)

Zero Flag (Z)

Sign Flag (S)

Register Bank Select Flag (B)

Overflow Flag (O)

Page 18 of 60

2. Central Processing Unit (CPU)