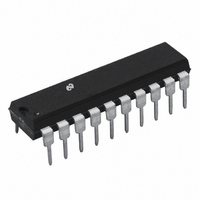

COP8SAA720N9 National Semiconductor, COP8SAA720N9 Datasheet - Page 17

COP8SAA720N9

Manufacturer Part Number

COP8SAA720N9

Description

IC MCU OTP 8BIT 1K 20DIP

Manufacturer

National Semiconductor

Series

COP8™ 8SAr

Datasheet

1.COP8-PGMA-28CSP.pdf

(60 pages)

Specifications of COP8SAA720N9

Core Processor

COP8

Core Size

8-Bit

Speed

10MHz

Connectivity

Microwire/Plus (SPI)

Peripherals

POR, PWM, WDT

Number Of I /o

16

Program Memory Size

1KB (1K x 8)

Program Memory Type

OTP

Ram Size

64 x 8

Voltage - Supply (vcc/vdd)

2.7 V ~ 5.5 V

Oscillator Type

Internal

Operating Temperature

0°C ~ 70°C

Package / Case

20-DIP (0.300", 7.62mm)

Lead Free Status / RoHS Status

Contains lead / RoHS non-compliant

Eeprom Size

-

Data Converters

-

Other names

*COP8SAA720N9

COP8SAA720N9B

COP8SAA720NB

COP8SAA720N9B

COP8SAA720NB

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

6.0 Functional Description

6.7 RESET

The device is initialized when the RESET pin is pulled low or

the On-chip Power-On Reset is enabled.

The following occurs upon initialization:

The device comes out of reset with both the WATCHDOG

logic and the Clock Monitor detector armed, with the

WATCHDOG service window bits set and the Clock Monitor

bit set. The WATCHDOG and Clock Monitor circuits are

inhibited during reset. The WATCHDOG service window bits

being initialized high default to the maximum WATCHDOG

service window of 64k t

being initialized high will cause a Clock Monitor error follow-

ing reset if the clock has not reached the minimum specified

Port L: TRISTATE

Port C: TRISTATE

Port G: TRISTATE

Port F: TRISTATE

Port D: HIGH

PC: CLEARED to 0000

PSW, CNTRL and ICNTRL registers: CLEARED

SIOR: UNAFFECTED after RESET with power already

T1CNTRL: CLEARED

Accumulator, Timer 1:

WKEN, WKEDG: CLEARED

WKPND: RANDOM

SP (Stack Pointer):

B and X Pointers:

RAM:

WATCHDOG (if enabled):

applied

RANDOM after RESET at power-on

RANDOM after RESET with crystal clock option

(power already applied)

UNAFFECTED after RESET with R/C clock option

(power already applied)

RANDOM after RESET at power-on

Initialized to RAM address 02F Hex (devices with

64 bytes of RAM), or initialized to

RAM address 06F Hex (devices with

128 bytes of RAM).

UNAFFECTED after RESET with power

already applied

RANDOM after RESET at power-on

UNAFFECTED after RESET with power already

applied

RANDOM after RESET at power-on

FIGURE 8. Reset Logic

C

clock cycles. The Clock Monitor bit

DS012838-13

(Continued)

17

frequency at the termination of reset. A Clock Monitor error

will cause an active low error output on pin G1. This error

output will continue until 16 t

the clock frequency reaching the minimum specified value,

at which time the G1 output will go high.

6.7.1 External Reset

The RESET input when pulled low initializes the device. The

RESET pin must be held low for a minimum of one instruc-

tion cycle to guarantee a valid reset. During Power-Up ini-

tialization, the user must ensure that the RESET pin is held

low until the device is within the specified V

R/C circuit on the RESET pin with a delay 5 times (5x)

greater than the power supply rise time or 15 µs whichever is

greater, is recommended. Reset should also be wide enough

to ensure crystal start-up upon Power-Up.

RESET may also be used to cause an exit from the HALT

mode.

A recommended reset circuit for this deviced is shown in

Figure 9 .

RC

6.7.2 On-Chip Power-On Reset

The on-chip reset circuit is selected by a bit in the ECON

register. When enabled, the device generates an internal

reset as V

reset circuitry is able to detect both fast and slow rise times

on V

Under no circumstances should the RESET pin be allowed

to float. If the on-chip Power-On Reset feature is being used,

RESET pin should be connected directly to V

of the power-on reset detector will always preset the Idle

timer to 0FFF(4096 t

generated.

If the Power-On Reset feature is enabled, the internal reset

will not be turned off until the Idle timer underflows. The

internal reset will perform the same functions as external

reset. The user is responsible for ensuring that V

minimum level for the operating frequency within the 4096

t

additional internal resets occur as long as V

above 2.0V.

Note: While the POR feature of the COP8SAx was never intended to function

C

. After the underflow, the logic is designed such that no

>

5x power supply rise time or 15 µs, whichever is greater.

CC

as a brownout detector, there are certain constraints of this block that

the system designer must address to properly recover from a brownout

condition. This is true regardless of whether the internal POR or the

external reset feature is used.

A brownout condition is reached when V

the minimum operating conditions of the device. The minimum guar-

anteed operating conditions are defined as V

V

is stopped) operation.

When using either the external reset or the POR feature to recover

from a brownout condition, V

external reset must be applied whenever it goes below the minimum

operating conditions as stated above.

FIGURE 9. Reset Circuit Using External Reset

CC

(V

= 2.7V

CC

CC

rises to a voltage level above 2.0V. The on-chip

rise time between 10 ns and 50 ms).

@

4 MHz, or V

C

). At this time, the internal reset will be

CC

= 2.0V during HALT mode (or when CKI

C

CC

–32 t

must be lowered to 0.25V or an

C

CC

clock cycles following

of the device goes below

CC

DS012838-14

= 4.5V

CC

CC

. The output

CC

@

voltage. An

www.national.com

CC

10 MHz CKI,

is at the

remains