ATA5771-PXQW Atmel, ATA5771-PXQW Datasheet

ATA5771-PXQW

Specifications of ATA5771-PXQW

Available stocks

Related parts for ATA5771-PXQW

ATA5771-PXQW Summary of contents

Page 1

... Pin Change Interrupt on 12 Pins – Enhanced Power-on Reset Circuit – Programmable Brown-out Detection Circuit – Internal Calibrated Oscillator – On-chip Temperature Sensor • 12 Programmable I/O Lines 5mm UHF ASK/FSK Transmitter with the Atmel AVR Microcontroller Atmel ATA5771/73/74 9137E–RKE–12/10 ...

Page 2

... ASK or FSK modula- tion. Its primary applications are in the application of Remote Keyless-Entry (RKE), Passive Entry Go (PEG) System and Remote Start. The ATA5771 is designed for 868MHz application, whereas ATA5773 for 315MHZ application and ATA5774 for 434MHz application. ...

Page 3

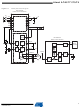

... Power up/down f/4 PLL CLK XTO VCO PA 9137E–RKE–12/10 VDD VS GND PXY PXY PXY PXY PXY ENABLE GND_RF VCC_RF VS Antenna PA_ENABLE ANT2 Loop Antenna ANT1 LNA VS Atmel ATA5771/73/74 UHF ASK/FSK Remote Control Receiver Demod Control PLL XTO VCO Micro- controller 3 ...

Page 4

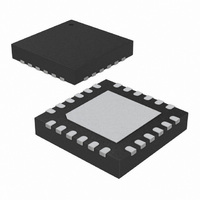

... Port 4-bit bi-directional I/O port with internal pull-up resistor 19 GND Microcontroller ground 20 XTAL Connection for crystal 21 VS_RF Transmitter supply voltage 22 GND_RF Transmitter ground 23 ENABLE Enable input 24 GND Ground GND Ground/backplane (exposed die pad) Atmel ATA5771/73/74 4 5mm VCC 1 18 PB0 2 17 PB1 3 16 PB3/RESET 4 15 ...

Page 5

... Switches on power amplifier. 9 PA_ENABLE Used for ASK modulation. 10 ANT2 Emitter of antenna output stage. 11 ANT1 Open collector antenna output. 20 XTAL Connection for crystal. 9137E–RKE–12/10 /4. XTAL Atmel ATA5771/73/74 Configuration VS 100 CLK 100 50 k PA_ENABLE U 20 µA ANT1 ANT2 VS VS 1.5 k 1.2 k XTAL 182 µ ...

Page 6

... Table 2-2. Pin Description (Continued) Pin Symbol Function 21 VS Supply voltage 22 GND Ground 23 ENABLE Enable input Atmel ATA5771/73/74 6 Configuration See ESD protection circuitry (see Figure 5-1 on page See ESD protection circuitry (see Figure 5-1 on page 200 k ENABLE 181). 181). 9137E–RKE–12/10 ...

Page 7

... ATA5773 after setting ENABLE to HIGH, before the clock output from the RF transmitter can be used. For ATA5771 and ATA5774 the MCU must wait longer than 1 ms until the clock output is stable. The clock output with the crystal tolerance is connected to the timer0 of the MCU ...

Page 8

... HIGH. Between the activation of the pin ENABLE and the pin PA_ENABLE minimum 3 ms time delay must be taken into account for the application with ATA5773, whereas a minimum 1 ms time delay for an application using ATA5771 or ATA5774. After the mentioned time delay the generated clock frequency by the RF transmitter can be used as reference for the data generation of the microcontroller block ...

Page 9

... Background: The current pulse of the power amplifier is 9mA and the maximum output power is delivered to a resistive load of 465 if the 1.0pF output capacitance of the power amplifier is compensated by the load impedance. And thus the load impedance of Z Load is achieved for the maximum output power of 7.5dBm. Atmel ATA5771/73/74 C Stray2 ...

Page 10

... Figure 3-2. Atmel ATA5771/73/ (166 + j226) for the Atmel ATA5771 with the power efficiency of 24% Load – Background: The current pulse of the power amplifier is 7.7mA and the maximum output power is delivered to a resistive load of 475 if the 0.53pF output capacitance of the power amplifier is compensated by the load impedance ...

Page 11

... Y DECODER Z CONTROL ALU LINES STATUS REGISTER PROGRAMMING ISP INTERFACE LOGIC DATA REGISTER DATA DIR. PORT A REG.PORT A PORT A DRIVERS PA7-PA0 Atmel ATA5771/73/74 INTERNAL INTERNAL CALIBRATED OSCILLATOR OSCILLATOR WATCHDOG TIMING AND TIMER CONTROL MCU CONTROL REGISTER MCU STATUS REGISTER TIMER/ COUNTER0 TIMER/ COUNTER1 ...

Page 12

... AEC-Q100. As indicated in the ordering information paragraph, the product is available in only one temper- ature grade. Table 4-1. Temperature -40 ; +125 Atmel ATA5771/73/74 12 ® core combines a rich instruction set with 32 general purpose working regis- Temperature Grade Identification for Automotive Products Temperature Identifier ...

Page 13

... I/O. Typically “LDS” and “STS” combined with “SBRS”, “SBRC”, “SBR”, and “CBR”. 9137E–RKE–12/10 46. Shorter pulses are not guaranteed to generate a reset. 66. Atmel ATA5771/73/74 66. Figure 4-13 on Section 4.14.3 “Alternate Port 13 ...

Page 14

... While one instruction is being executed, the next instruction is pre-fetched from the Program memory. This concept enables instructions to be executed in every clock cycle. The Program memory is In-System Reprogrammable Flash memory. Atmel ATA5771/73/74 14 ® core architecture in general. The main function of the ...

Page 15

... Instruction Set Reference. This will in many cases remove the need for using the dedicated compare instructions, resulting in faster and more compact code. The Status Register is not automatically stored when entering an interrupt routine and restored when returning from an interrupt. This must be handled by software. 9137E–RKE–12/10 Atmel ATA5771/73/74 ® instructions have a single 16-bit 15 ...

Page 16

... The Zero Flag Z indicates a zero result in an arithmetic or logic operation. See the “Instruction Set Description” for detailed information. • Bit 0 – C: Carry Flag The Carry Flag C indicates a carry in an arithmetic or logic operation. See the “Instruction Set Description” for detailed information. Atmel ATA5771/73/ ...

Page 17

... Working R16 Registers R17 … R26 R27 R28 R29 R30 R31 Figure 4-3, each register is also assigned a Data memory address, mapping them Atmel ATA5771/73/74 ® AVR Enhanced RISC instruction set. In order to 0 Addr. 0x00 0x01 0x02 0x0D 0x0E 0x0F 0x10 0x11 ...

Page 18

... AVR architecture is so small that only SPL is needed. In this case, the SPH Register will not be present. 4.7.6.1 SPH and SPL – Stack Pointer High and Low Bit 0x3E (0x5E) 0x3D (0x5D) Read/Write Initial Value Atmel ATA5771/73/74 18 The X-, Y-, and Z-registers R27 (0x1B ...

Page 19

... Instruction Fetch shows the internal timing concept for the Register File single clock cycle an Single Cycle ALU Operation T1 clk CPU Total Execution Time ALU Operation Execute Result Write Back Atmel ATA5771/73/74 , directly generated from the selected CPU Section 4.12 “Interrupts” on page ...

Page 20

... No interrupt will be executed after the CLI instruction, even if it occurs simultaneously with the CLI instruction. The following example shows how this can be used to avoid interrupts during the timed EEPROM write sequence. Assembly Code Example C Code Example Atmel ATA5771/73/74 20 ® exits from an interrupt, it will always return to the main program and in r16, SREG ...

Page 21

... Global Interrupt Enable */ _SLEEP(); /* enter sleep, waiting for interrupt */ /* note: will enter sleep before any pending interrupt(s) */ Atmel ATA5771/73/74 ® ® AVR interrupts is four clock 21 ...

Page 22

... The Indirect with Displacement mode reaches 63 address locations from the base address given by the Y- or Z-register. When using register indirect addressing modes with automatic pre-decrement and post-incre- ment, the address registers X, Y, and Z are decremented or incremented. Atmel ATA5771/73/74 22 Program Memory Map Program Memory shows how the ATtiny44V SRAM Memory is organized. ® ...

Page 23

... Data Memory 32 Registers 64 I/O Registers Internal SRAM (256 x 8) On-chip Data SRAM Access Cycles T1 clk CPU Address Compute Address Data WR Data RD Memory Access Instruction Atmel ATA5771/73/74 17. 0x0000 - 0x001F 0x0020 - 0x005F 0x0060 0x015F cycles as described in Figure CPU T2 T3 Address valid Next Instruction 4-9. 23 ...

Page 24

... EEPE (within four cycles after EEMPE is written) will trigger the erase operation only (pro- gramming time is given in Table 1). The EEPE bit remains set until the erase operation completes. While the device is busy programming not possible to do any other EEPROM operations. Atmel ATA5771/73/74 24 ® ATtiny44V contains 256 bytes of data EEPROM memory organized as a sep- Section 4.23.6 “ ...

Page 25

... The following code examples show one assembly and one C function for erase, write, or atomic write of the EEPROM. The examples assume that interrupts are controlled (e.g., by disabling interrupts globally) so that no interrupts will occur during execution of these functions. 9137E–RKE–12/10 Atmel ATA5771/73/74 Section 4.9.10.1 “Oscillator Calibration 39. 25 ...

Page 26

... Assembly Code Example C Code Example Note: Atmel ATA5771/73/74 26 EEPROM_write: ; Wait for completion of previous write sbic EECR,EEPE rjmp EEPROM_write ; Set Programming mode r16, (0<<EEPM1)|(0<<EEPM0) ldi EECR, r16 out ; Set up address (r17) in address register out EEARL, r17 ; Write data (r16) to data register out EEDR,r16 ...

Page 27

... EEDR; } The code examples are only valid for the Atmel ATtiny44V, using 8-bit addressing mode. , the EEPROM data can be corrupted because the supply voltage is CC ® ® AVR RESET active (low) during periods of insufficient power supply volt- Atmel ATA5771/73/74 CC reset 27 ...

Page 28

... General Purpose I/O Registers within the address range 0x00 - 0x1F are directly bit-accessible using the SBI, CBI, SBIS, and SBIC instructions. Atmel ATA5771/73/74 28 ® ATtiny44V is shown in 213. ® ...

Page 29

... EEAR7 EEAR6 EEAR5 EEAR4 R/W R/W R/W R EEDR7 EEDR6 EEDR5 EEDR4 R/W R/W R/W R – – EEPM1 EEPM0 R R R/W R Atmel ATA5771/73/ – – – EEAR8 R EEAR3 EEAR2 EEAR1 EEAR0 R/W R/W R/W R EEDR3 EEDR2 EEDR1 EEDR0 R/W R/W R/W R/W ...

Page 30

... EEPROM write takes place. When the write access time has elapsed, the EEPE bit is cleared by hardware. When EEPE has been set, the CPU is halted for two cycles before the next instruction is executed. Atmel ATA5771/73/74 30 ® devices, always write this bit to zero. After reading, mask out this ...

Page 31

... GPIOR0 – General Purpose I/O Register 0 Bit 0x13 (0x33) Read/Write Initial Value 9137E–RKE–12/ MSB R/W R/W R/W R MSB R/W R/W R/W R MSB R/W R/W R/W R Atmel ATA5771/73/ LSB R/W R/W R/W R LSB R/W R/W R/W R LSB R/W R/W R/W R GPIOR2 GPIOR1 GPIOR0 31 ...

Page 32

... The ADC is provided with a dedicated clock domain. This allows halting the CPU and I/O clocks in order to reduce noise generated by digital circuitry. This gives more accurate ADC conversion results. Atmel ATA5771/73/74 32 presents the principal clock systems in the Atmel Section 4.10 “Power Management and Sleep Modes” on page ...

Page 33

... Device Clocking Options Select 1. For all fuses “1” means unprogrammed while “0” means programmed. Table 4-4. Number of Watchdog Oscillator Cycles Typ Time-out Table 4-5 on page Atmel ATA5771/73/74 ® ® AVR clock generator, and (1) CKSEL3..0 0000 0010 0100 ...

Page 34

... The operating mode is selected by the fuses CKSEL3..1 as shown in Table 4-5. CKSEL3..1 100 Notes: The CKSEL0 Fuse together with the SUT1..0 Fuses select the start-up times as shown in Table 4-6 on page Atmel ATA5771/73/74 34 Crystal Oscillator Operating Modes Frequency Range (MHz) (1) 0.4 - 0.9 101 ...

Page 35

... Start-up Times for the Low Frequency Crystal Oscillator Clock Selection Start-up Time from Power Down and Power Save ( ( 32K CK 1. These options should only be used if frequency stability at start-up is not important for the application. Atmel ATA5771/73/74 Additional Delay from Reset (V = 5.0V) Recommended Usage CC Ceramic resonator, fast 14CK + 4.1 ms rising power ...

Page 36

... When this Oscillator is selected, start-up times are determined by the SUT Fuses as shown in Table Table 4-9. SUT1.. Note: Atmel ATA5771/73/74 36 and Section 8.3.8.9 “Internal Oscillator Speed” on page 207 for more details. 4-8. If selected, it will operate with no external components. During reset, hardware Table 8-1 on page 189. 39 possible to get a higher calibration accuracy than by using 189. Section 4.23.4 “ ...

Page 37

... EXTERNAL CLOCK SIGNAL 4-10. Start-up Times for the External Clock Selection Start-up Time from Power-down and Power-save for details. Atmel ATA5771/73/74 CLKI GND Additional Delay from Reset Recommended Usage 14CK BOD enabled 14CK + 4 ms Fast rising power 14CK + 64 ms Slowly rising power Reserved Section 4.9.9 “ ...

Page 38

... From the time the CLKPS values are written, it takes between and T1 + 2*T2 before the new clock frequency is active. In this interval, 2 active clock edges are produced. Here the previous clock period, and T2 is the period corresponding to the new prescaler setting. Atmel ATA5771/73/74 38 4-11. ...

Page 39

... Table 8-1 on page 189. The application software can write this register 189. Calibration outside that range is not guaranteed CLKPCE – – – R ® ATtiny44V and will always read as zero. 40. Atmel ATA5771/73/ CAL3 CAL2 CAL1 CAL0 R/W R/W R/W R CLKPS3 CLKPS2 CLKPS1 CLKPS0 R/W ...

Page 40

... CKDIV8 Fuse setting. The Application software must ensure that a sufficient division factor is chosen if the selcted clock source has a higher frequency than the maximum frequency of the device at the present operating conditions. The device is shipped with the CKDIV8 Fuse programmed. Table 4-12. CLKPS3 Atmel ATA5771/73/74 40 Clock Prescaler Select CLKPS2 CLKPS1 0 ...

Page 41

... Active Clock Domains and Wake-up Sources in the Different Sleep Modes Active Clock Domains X (2) 1. For INT0, only level interrupt. 2. Only recommended with external crystal or resonator selected as clock source Table 4-14 on page 44 , while allowing the other clocks to run. Atmel ATA5771/73/74 Table 4-13 Oscillators Wake-up Sources ...

Page 42

... All functions not needed should be disabled. In particular, the follow- ing modules may need special consideration when trying to achieve the lowest possible power consumption. Atmel ATA5771/73/ while allowing the other clocks to run. for details 44, provides a method to stop the clock to individualperipherals to reduce power Section 8.3.8.4 “ ...

Page 43

... I/O Section 4.14.2.5 “Digital Input Enable and Sleep Modes” on for details on which pins are enabled. If the input buffer is enabled and the input sig- Atmel ATA5771/73/74 Section 4.20 “Analog to Digital Converter” on Section 4.19 “Analog Comparator” on page 137 Section 4.11.1.4 “Brown-out Detection” on for details on the start-up time ...

Page 44

... These bits are reserved bits in the ATtiny44V and will always read as zero. • Bit 3- PRTIM1: Power Reduction Timer/Counter1 Writing a logic one to this bit shuts down the Timer/Counter1 module. When the Timer/Counter1 is enabled, operation will continue like before the shutdown. Atmel ATA5771/73/ input pin can cause significant current even in active mode. Digital CC ...

Page 45

... Figure 4-13 on page 46 defines the electrical parameters of the reset circuitry. ® ® AVR are immediately reset to their initial state when a reset 33. ). POT ) and the Brown-out Detector is enabled. BOT Atmel ATA5771/73/74 shows the reset logic. Table 4-15 on Section 4.9.2 “Clock is below the Brown-out CC 45 ...

Page 46

... A Power-on Reset (POR) circuit ensures that the device is reset from Power-on. Reaching the Power-on Reset threshold voltage invokes the delay counter, which determines how long the device is kept in RESET after V delay, when V Figure 4-14. MCU Start-up, RESET Tied TIME-OUT INTERNAL Atmel ATA5771/73/74 46 Power-on Reset Circuit Brown-out BODLEVEL [1..0] Reset Circuit Pull-up Resistor ...

Page 47

... Before rising, the supply has to be between 190) will generate a reset, even if the clock is not running. Shorter pulses are not – on its positive edge, the delay counter starts the MCU after the Time-out period – – has expired. Atmel ATA5771/73/74 V RST t ...

Page 48

... Brown-out Reset is immediately activated. When V trigger level (V t TOUT The BOD circuit will only detect a drop in V ger than t Figure 4-17. Brown-out Reset During Operation Atmel ATA5771/73/ ® ATtiny44V has an On-chip Brown-out Detection (BOD) circuit for monitoring the = and V ...

Page 49

... Power-down mode. 9137E–RKE–12/ ® ATtiny44V features an internal bandgap reference. This reference is used for Section 8.3.4 “System and Reset Characterizations” on page Atmel ATA5771/73/74 for details on operation of the Watchdog Timer. . See TOUT 190 ...

Page 50

... In this mode, the Watchdog Timer is initially disabled, but can be enabled by writing the WDE bit to one without any restriction. A timed sequence is needed when disabling an enabled Watchdog Timer. To disable an enabled Watchdog Timer, the following procedure must be followed: Atmel ATA5771/73/74 50 53. The WDR – Watchdog Reset – instruction resets the Watchdog Timer. for details. ...

Page 51

... MCUSR as early as possible in the program. If the register is cleared before another reset occurs, the source of the reset can be found by examining the Reset Flags. 9137E–RKE–12/ – – – – Atmel ATA5771/73/ WDRF BORF EXTRF PORF R/W R/W R/W R/W See Bit Description MCUSR 51 ...

Page 52

... WDE even though it is set to one before the disable operation starts. 2. Within the next four clock cycles, write a logic 0 to WDE. This disables the Watchdog. In safety level not possible to disable the Watchdog Timer, even with the algorithm described above. See Watchdog Timer” on page Atmel ATA5771/73/ ...

Page 53

... Number of WDT Oscillator WDP2 WDP1 WDP0 Atmel ATA5771/73/74 Section 4.11.5.1 “MCUSR – Typical Time-out at Cycles cycles cycles cycles 64 ms 16K cycles 0.125 s 32K cycles 0.25 s 64K cycles 0.5 s 128K cycles 1.0 s 256K cycles 2.0 s 512K cycles 4.0 s 1024K cycles 8.0 s Reserved = 5.0V 53 ...

Page 54

... The following code example shows one assembly and one C function for turning off the WDT. The example assumes that interrupts are controlled (e.g., by disabling interrupts globally) so that no interrupts will occur during execution of these functions. Assembly Code Example C Code Example Note: Atmel ATA5771/73/74 54 (1) WDT_off: WDR ; Clear WDRF in MCUSR ldi r16, (0< ...

Page 55

... ADC 15 0x000E EE_RDY 16 0x000F USI_START 17 0x0010 USI_OVF Atmel ATA5771/73/74 Section 4.7.8 “Reset Interrupt Definition External Pin, Power-on Reset, Brown-out Reset, Watchdog Reset External Interrupt Request 0 Pin Change Interrupt Request 0 Pin Change Interrupt Request 1 Watchdog Time-out Timer/Counter1 Capture Event Timer/Counter1 Compare Match A ...

Page 56

... Atmel ATA5771/73/74 56 rjmp RESET rjmp EXT_INT0 rjmp PCINT0 rjmp PCINT1 rjmp WATCHDOG rjmp TIM1_CAPT rjmp TIM1_COMPA rjmp TIM1_COMPB rjmp TIM1_OVF rjmp ...

Page 57

... Section 4.9.1 “Clock Systems and their Distribution” on page Section 4.9 “System Clock and Clock Options” on page pin_lat PCINT( pin_sync LE clk PCINT(0) in PCMSK(x) clk PCINT(0) pin_lat pin_sync pcint_in_(0) pcint_syn pcint_setflag PCIF Atmel ATA5771/73/74 32. Figure 4-20. pcint_in_(0) 0 pcint_syn pcint_setflag x clk PCIF 57 ...

Page 58

... When the PCIE1 bit is set (one) and the I-bit in the Status Register (SREG) is set (one), pin change interrupt 1 is enabled. Any change on any enabled PCINT11..8 pin will cause an inter- rupt. The corresponding interrupt of Pin Change Interrupt Request is executed from the PCI1 Interrupt Vector. PCINT11..8 pins are enabled individually by the PCMSK1 Register. Atmel ATA5771/73/ – ...

Page 59

... I/O pin. If PCINT11..8 is cleared, pin change interrupt on the corresponding I/O pin is disabled. 9137E–RKE–12/ – INTF0 PCIF1 PCIF0 R R/W R/W R – – – – PCINT11 R Atmel ATA5771/73/ – – – – PCINT10 PCINT9 PCINT8 R/W R/W R GIFR PCMSK1 59 ...

Page 60

... However, when using the register or bit defines in a program, the precise form must be used. For example, PORTB3 for bit no Port B, here documented generally as PORTxn. The physical I/O Registers and bit locations are listed in Atmel ATA5771/73/ ...

Page 61

... I/O CLOCK I/O 1. WRx, WPx, WDx, RRx, RPx, and RDx are common to all pins within the same port. clk SLEEP, and PUD are common to all ports. Atmel ATA5771/73/74 Section 4.14.2 “Ports as General Digi- 66. Refer to the individual module sections Figure 4-22 PUD ...

Page 62

... PORTxn} = 0b10 intermediate step. Table 4-21 Table 4-21. DDxn Atmel ATA5771/73/74 62 74, the DDxn bits are accessed at the DDRx I/O address, the PORTxn bits at the summarizes the control signals for the pin value. Port Pin Configurations PUD PORTxn (in MCUCR) I/O ...

Page 63

... Figure 4-22 on page SYSTEM CLK INSTRUCTIONS XXX SYNC LATCH PINxn r17 Figure 4-24 on page 64. The out instruction sets the “SYNC LATCH” signal at the Atmel ATA5771/73/74 61, the PINxn Register bit and the pre- and t pd,max pd,min XXX in r17, PINx 0x00 t pd, max ...

Page 64

... The resulting pin values are read back again, but as previously discussed, a nop instruction is included to be able to read back the value recently assigned to some of the pins. Assembly Code Example C Code Example Atmel ATA5771/73/74 64 SYSTEM CLK r16 out PORTx, r16 ...

Page 65

... Figure 4-22 on page 61, the digital input signal can be clamped to ground at the 66. or GND is not recommended, since this may cause excessive cur- CC Atmel ATA5771/73/74 Section 4.14.3 “Alternate Port Functions” ...

Page 66

... The overriding signals may not be present in all port pins, but the figure serves as a generic description applicable to all port pins in the AVR family. Figure 4-25. Alternate Port Functions Note: Table 4-22 on page 67 indexes from generated internally in the modules having the alternate function. Atmel ATA5771/73/74 66 PUOExn PUOVxn 1 0 DDOExn DDOVxn ...

Page 67

... Unless the Digital Input is used as a clock source, the module with the alternate function will use its own synchronizer. This is the Analog Input/Output to/from alternate functions. Analog The signal is connected directly to the pad, and can be used Input/Output bi-directionally. Atmel ATA5771/73/74 67 ...

Page 68

... AREF pin by setting (one) the bit REFS0 in the ADC Multiplexer Selection Register (ADMUX). PCINT0: Pin Change Interrupt source 0. The PA0 pin can serve as an external interrupt source for pin change interrupt 0. Atmel ATA5771/73/74 68 Port A Pins Alternate Functions Port Pin Alternate Function ADC0: ADC input channel 0 ...

Page 69

... Timer/Counter1 Compare Match B. The PA5 pin has to be configured as an output (DDA5 set (one)) to serve this function. The OC1B pin is also the output pin for the PWM mode timer function. PCINT5: Pin Change Interrupt source 5. The PA5 pin can serve as an external interrupt source for pin change interrupt 0. 9137E–RKE–12/10 Atmel ATA5771/73/ ...

Page 70

... Table 4-24. Signal Name PUOE PUOV DDOE DDOV PVOE PVOV PTOE DIEOE DIEOV DI AIO Atmel ATA5771/73/ Table 4-26 on page 71 relate the alternate functions of Port A to the overriding Table 4-25 on page 71. Overriding Signals for Alternate Functions in PA7..PA5 PA7/ADC7/OC0B/ICP1/ PA6/ADC6/DI/SDA/OC1A/ PCINT7 PCINT6 0 0 ...

Page 71

... ADC4 Input ADC3 Input Overriding Signals for Alternate Functions in PA1..PA0 PA1/ADC1/AIN0/PCINT1 PCINT1 • PCIE0 + ADC1D PCINT1 • PCIE0 PCINT1 Input ADC1/Analog Comparator Positive Input Atmel ATA5771/73/74 PA2/ADC2/AIN1/PCINT2 PCINT2 • PCIE + ADC2D PCINT3 • PCIE0 PCINT0 Input ADC2/Analog Comparator Negative Input PA0/ADC0/AREF/PCINT0 RESET • ...

Page 72

... CKOUT Fuse is programmed, regardless of the PORTB2 and DDB2 settings. It will also be output during reset. PCINT10: Pin Change Interrupt source 10. The PB2 pin can serve as an external interrupt source for pin change interrupt 1. Atmel ATA5771/73/74 72 Port B Pins Alternate Functions Port Pin Alternate Function XTAL1: Crystal Oscillator Input ...

Page 73

... RSTDISBL + DEBUGWIRE_ENABLE PCINT11 • PCIE1 (2) DEBUGWIRE_ENABLE + (RSTDISBL PCINT11 • PCIE1) dW/PCINT11 Input RSTDISBL is 1 when the Fuse is “0” (Programmed). DebugWIRE is enabled wheb DWEN Fuse is programmed and Lock bits are unprogrammed. Atmel ATA5771/73/74 PB2/INT0/OC0A/CKOUT/PCINT10 (2) CKOUT 0 (2) CKOUT 1'b1 (2 CKOUT + OC0A enable CKOUT • ...

Page 74

... PORTxn Registers are configured to enable the pull-ups ({DDxn, PORTxn} = 0b01). See tion 4.14.2.1 “Configuring the Pin” on page 62 4.14.4.2 PORTA – Port A Data Register Bit 0x1B (0x3B) Read/Write Initial Value Atmel ATA5771/73/74 74 Overriding Signals for Alternate Functions in PB1..PB0 PB1/XTAL2/PCINT9 (1) EXT_OSC 0 (1) ...

Page 75

... PINA5 PINA4 R/W R/W R/W R N/A N – – – – – – N/A N/A Atmel ATA5771/73/ DDA3 DDA2 DDA1 DDA0 R/W R/W R/W R PINA3 PINA2 PINA1 PINA0 R/W R/W R/W R/W N/A N/A N/A N PORTB3 PORTB2 PORTB1 PORTB0 R/W R/W R/W R ...

Page 76

... I/O pins. CPU accessible I/O Registers, including I/O bits and I/O pins, are shown in bold. The device-specific I/O Register and bit locations are listed in the 4.9.10 “Register Description” on page Figure 4-26. 8-bit Timer/Counter Block Diagram Atmel ATA5771/73/74 76 39. Count ...

Page 77

... The counter reaches the TOP when it becomes equal to the highest value in the count sequence. The TOP value can be assigned to be the fixed value 0xFF (MAX) or the value stored in the OCR0A Register. The assignment is dependent on the mode of operation. Section 4.17 “Timer/Counter Prescaler” on page Atmel ATA5771/73/74 for details. The 123. 77 ...

Page 78

... OC0A. For more details about advanced counting sequences and waveform generation, see Section 4.15.7 “Modes of Operation” on page The Timer/Counter Overflow Flag (TOV0) is set according to the mode of operation selected by the WGM01:0 bits. TOV0 can be used for generating a CPU interrupt. Atmel ATA5771/73/74 78 shows a block diagram of the counter and its surroundings. DATA BUS ...

Page 79

... CPU will access the OCR0x directly. 9137E–RKE–12/10 81. shows a block diagram of the Output Compare unit. DATA BUS OCRnx = (8-bit Comparator ) top bottom Waveform Generator FOCn WGMn1:0 Atmel ATA5771/73/74 Section 4.15.7 “Modes of Operation” TCNTn OCFnx (Int.Req.) OCnx COMnX1:0 79 ...

Page 80

... Control Registers (DDR and PORT) that are affected by the COM0x1:0 bits are shown. When referring to the OC0x state, the reference is for the internal OC0x Register, not the OC0x pin system reset occur, the OC0x Register is reset to “0”. Atmel ATA5771/73/74 80 Figure 4-29 on page 81 ...

Page 81

... Generator FOCn OCnx D PORT D DDR clk I/O Section 4.10.8 “Register Description” on page 44 Table 4-31 on page 88, and for phase correct PWM refer to Section 4.15.7 “Modes of Operation” on page Atmel ATA5771/73/ OCn Pin 88. For fast PWM mode, refer to Table 4-33 on page 89. 81). 81 ...

Page 82

... If the new value written to OCR0A is lower than the current value of TCNT0, the counter will miss the Compare Match. The counter will then have to count to its maximum value (0xFF) and wrap around starting at 0x00 before the Compare Match can occur. Atmel ATA5771/73/74 82 Figure 4-33 on page and ...

Page 83

... PWM outputs. The small horizontal line marks on the TCNT0 slopes represent Com- pare Matches between OCR0x and TCNT0. 9137E–RKE–12/10 /2 when OCR0A is set to zero (0x00). The waveform frequency is defined by the fol ------------------------------------------------------ - OCnx 2 Figure 4-31. The TCNT0 value is in the timing diagram shown as a Atmel ATA5771/73/74 f clk_I/O N OCRnx ...

Page 84

... OC0x to toggle its logical level on each Compare Match (COM0x1:0 = 1). The wave- form generated will have a maximum frequency of This feature is similar to the OC0A toggle in CTC mode, except the double buffer feature of the Output Compare unit is enabled in the fast PWM mode. Atmel ATA5771/73/ ...

Page 85

... Figure 4-32 on page 85. The TCNT0 value is in the timing diagram shown Table 4-33 on page Atmel ATA5771/73/74 OCnx Interrupt Flag Set OCRnx Update TOVn Interrupt Flag Set (COMnx1 (COMnx1 89) ...

Page 86

... Flags are set. shows the count sequence close to the MAX value in all modes other than phase correct PWM mode. Figure 4-33. Timer/Counter Timing Diagram, no Prescaling (clk TCNTn Atmel ATA5771/73/ OCnxPCPWM Figure 4-32 on page 85 Figure 4-33 contains timing data for basic Timer/Counter operation. The figure ...

Page 87

... I/O OCRnx - 1 OCFnx shows the setting of OCF0A and the clearing of TCNT0 in CTC mode and fast Prescaler (f /8) clk_I/O clk I/O clk Tn /8) I/O TOP - 1 OCFnx Atmel ATA5771/73/74 /8) clk_I/O MAX BOTTOM OCRnx OCRnx + 1 OCRnx Value TOP BOTTOM TOP BOTTOM + 1 /8) clk_I/O OCRnx + 2 ...

Page 88

... When OC0A is connected to the pin, the function of the COM0A1:0 bits depends on the WGM02:0 bit setting. bits are set to a normal or CTC mode (non-PWM). Table 4-31. COM01 Table 4-32 mode. Table 4-32. COM01 Note: Atmel ATA5771/73/ COM0A1 COM0A0 COM0B1 R/W R/W R/W ...

Page 89

... A special case occurs when OCR0B equals TOP and COM0B1 is set. In this case, the Com- pare Match is ignored, but the set or clear is done at BOTTOM. See PWM Mode” on page 83 for more details. Atmel ATA5771/73/74 (1) Section 4.15.7.4 “Phase for more details. (1) Section 4.15.7.3 “ ...

Page 90

... Table 4-37. Mode Note: Atmel ATA5771/73/74 90 shows the COM0B1:0 bit functionality when the WGM02:0 bits are set to phase Compare Output Mode, Phase Correct PWM Mode COM0A0 Description 0 0 Normal port operation, OC0B disconnected Reserved Clear OC0B on Compare Match when up-counting. Set OC0B on ...

Page 91

... Bits 2:0 – CS02:0: Clock Select The three Clock Select bits select the clock source to be used by the Timer/Counter. 9137E–RKE–12/ FOC0A FOC0B – Section 4.15.9.1 “TCCR0A – Timer/Counter Control Register A” on 88. Atmel ATA5771/73/ – WGM02 CS02 CS01 R R/W R/W R ...

Page 92

... Read/Write Initial Value The Output Compare Register B contains an 8-bit value that is continuously compared with the counter value (TCNT0). A match can be used to generate an Output Compare interrupt generate a waveform output on the OC0B pin. Atmel ATA5771/73/74 92 Clock Select Bit Description CS01 CS00 Description ...

Page 93

... When the I-bit in SREG, OCIE0A (Timer/Counter0 Compare Match Interrupt Enable), and OCF0A are set, the Timer/Counter0 Compare Match Interrupt is executed. 9137E–RKE–12/ – – – – – – – – Atmel ATA5771/73/ – OCIE0B OCIE0A TOIE0 R R/W R/W R – OCF0B OCF0A TOV0 R R/W R/W R TIMSK0 TIFR0 ...

Page 94

... I/O pins. CPU accessible I/O Registers, including I/O bits and I/O pins, are shown in bold. The device-specific I/O Register and bit locations are listed in the 4.8.5 “Register Description” on page Atmel ATA5771/73/74 94 Table 4-37 on page Figure 4-37 on page 29 ...

Page 95

... Count Clear Control Logic Direction TOP Timer/Counter TCNTn = = OCRnA = OCRnB ICRn TCCRnA 97. The Timer/Counter Control Registers (TCCR1A/B) are 8-bit reg Atmel ATA5771/73/74 TOVn (Int.Req.) Clock Select clk Tn Edge Detector BOTTOM ( From Prescaler ) = 0 OCnA (Int.Req.) Waveform Generation OCnB Fixed (Int.Req.) ...

Page 96

... TCCR1A. • WGM13 is added to TCCR1B. The 16-bit Timer/Counter has improvements that will affect the compatibility in some special cases. Atmel ATA5771/73/74 96 The counter reaches the BOTTOM when it becomes 0x0000. The counter reaches its MAXimum when it becomes 0xFFFF (decimal 65535). ...

Page 97

... Set TCNT1 to 0x01FF ldi r17,0x01 ldi r16,0xFF out TCNT1H,r17 out TCNT1L,r16 ; Read TCNT1 into r17:r16 in r16,TCNT1L in r17,TCNT1H ... (1) unsigned int i; ... /* Set TCNT1 to 0x01FF */ TCNT1 = 0x1FF; /* Read TCNT1 into TCNT1; ... 1. See Section 4.6 “About Code Examples” on page Atmel ATA5771/73/74 13. ® CPU 97 ...

Page 98

... The following code examples show how atomic read of the TCNT1 Register contents. Reading any of the OCR1A/B or ICR1 Registers can be done by using the same principle. Assembly Code Example C Code Example Note: The assembly code example returns the TCNT1 value in the r17:r16 register pair. Atmel ATA5771/73/74 98 (1) TIM16_ReadTCNT1: ; Save global interrupt flag in r18,SREG ...

Page 99

... TIM16_WriteTCNT1( unsigned int unsigned char sreg; unsigned int i; /* Save global interrupt flag */ sreg = SREG; /* Disable interrupts */ _CLI(); /* Set TCNT1 TCNT1 = i; /* Restore global interrupt flag */ SREG = sreg See Section 4.6 “About Code Examples” on page Section 4.17 “Timer/Counter Prescaler” on page Atmel ATA5771/73/74 13. 123. 99 ...

Page 100

... Output Compare outputs OC1x. For more details about advanced count- ing sequences and waveform generation, see 81. The Timer/Counter Overflow Flag (TOV1) is set according to the mode of operation selected by the WGM13:0 bits. TOV1 can be used for generating a CPU interrupt. Atmel ATA5771/73/74 100 Figure 4-38 shows a block diagram of the counter and its surroundings. ...

Page 101

... DATA BUS TEMP (8-bit) ICRnH (8-bit) ICRnL (8-bit) ICRn (16-bit Register) WRITE ACO* ACIC* Analog Comparator ICPn Atmel ATA5771/73/74 Figure 4-39. The elements (8-bit) TCNTnH (8-bit) TCNTnL (8-bit) TCNTn (16-bit Counter) ICNC ICES Noise Edge ICFn (Int.Req.) Canceler ...

Page 102

... Using the Input Capture unit in any mode of operation when the TOP value (resolution) is actively changed during operation, is not recommended. Atmel ATA5771/73/74 102 97. (Figure 4-50 on page Section 4.16.3 “ ...

Page 103

... DATA BUS TEMP (8-bit) OCRnxH Buf. (8-bit) OCRnxL Buf. (8-bit) OCRnx Buffer (16-bit Register) OCRnxH (8-bit) OCRnxL (8-bit) OCRnx (16-bit Register) TOP BOTTOM Atmel ATA5771/73/74 (8-bit) TCNTnH (8-bit) TCNTnL (8-bit) TCNTn (16-bit Counter) = (16-bit Comparator ) OCFnx (Int.Req.) Waveform Generator WGMn3:0 COMnx1:0 81) ...

Page 104

... The setup of the OC1x should be performed before setting the Data Direction Register for the port pin to output. The easiest way of setting the OC1x value is to use the Force Output Com- pare (1x) strobe bits in Normal mode. The OC1x Register keeps its value even when changing between Waveform Generation modes. Atmel ATA5771/73/74 104 97. Section 4.16.3 “Accessing ...

Page 105

... See The COM1x1:0 bits have no effect on the Input Capture unit. 9137E–RKE–12/10 COMnx1 Waveform COMnx0 Generator FOCnx clk I/O Table 4-41 on page 117 for details. Section 4.11.5 “Register Description” on page 51 Atmel ATA5771/73/74 Figure 4- OCnx PORT D Q DDR Table 4-39 on page ...

Page 106

... The OCR1A or ICR1 define the top value for the counter, hence also its res- olution. This mode allows greater control of the compare match output frequency. It also simplifies the operation of counting external events. Atmel ATA5771/73/74 106 116, and for phase correct and phase and frequency correct PWM refer to 117. (Section 4.15.6 “ ...

Page 107

... MAX to 0x0000. 9137E–RKE–12/ when OCR1A is set to zero (0x0000). The waveform frequency is A clk_I ------------------------------------------------------- OCnA N 2 Atmel ATA5771/73/74 Figure 4-42. The counter value (TCNT1) OCnA Interrupt Flag Set or ICFn Interrupt Flag Set (Interrupt on TOP) (COMnA1 clk_I/O OCRnA 1 + 107 ...

Page 108

... OC1A or ICF1 flag is set at the same timer clock cycle as TOV1 is set when either OCR1A or ICR1 is used for defining the TOP value. If one of the interrupts are enabled, the interrupt handler routine can be used for updating the TOP and compare values. Atmel ATA5771/73/74 108 TOP ...

Page 109

... OC1A to toggle its logical level on each compare match (COM1A1:0 = 1). The wave- form generated will have a maximum frequency of (0x0000). This feature is similar to the OC1A toggle in CTC mode, except the double buffer feature of the Output Compare unit is enabled in the fast PWM mode. 9137E–RKE–12/10 Atmel ATA5771/73/74 Table 4-40 on page f clk_I/O f ...

Page 110

... The diagram includes non-inverted and inverted PWM outputs. The small horizontal line marks on the TCNT1 slopes represent compare matches between OCR1x and TCNT1. The OC1x interrupt flag will be set when a compare match occurs. Figure 4-44. Phase Correct PWM Mode, Timing Diagram TCNTn OCnx OCnx Period Atmel ATA5771/73/74 110 TOP log + ...

Page 111

... PWM mode. For inverted PWM the output will have the opposite logic values. 9137E–RKE–12/10 117). The actual OC1x value will only be visible on the port pin if the data direction for f OCnxPCPWM Atmel ATA5771/73/74 Figure 4-44 on page 110 Table 4- clk_I/O ...

Page 112

... The diagram includes non-inverted and inverted PWM outputs. The small horizontal line marks on the TCNT1 slopes represent compare matches between OCR1x and TCNT1. The OC1x interrupt flag will be set when a compare match occurs. Atmel ATA5771/73/74 112 and Figure 4-45 on page 113) ...

Page 113

... The actual OC1x value will only be visible on the port pin if the data f = --------------------------------- OCnxPFCPWM 2 Atmel ATA5771/73/74 OCnA Interrupt Flag Set or ICFn Interrupt Flag Set (Interrupt on TOP) OCRnx/TOP Updateand TOVn Interrupt Flag Set (Interrupt on Bottom) ...

Page 114

... OCR1x Register is updated with the OCR1x buffer value (only for modes utilizing double buffering). OCF1x. Figure 4-46. Timer/Counter Timing Diagram, Setting of OCF1x, no Prescaling Figure 4-47 Figure 4-47. Timer/Counter Timing Diagram, Setting of OCF1x, with Prescaler (f Atmel ATA5771/73/74 114 Figure 4-46 clk I/O clk ...

Page 115

... TCNTn TOP - 1 (CTC and FPWM) TCNTn TOP - 1 (PC and PFC PWM) TOVn (FPWM) and ICF n (if used as TOP) OCRnx Old OCRnx Value (Update at TOP) Atmel ATA5771/73/74 TOP BOTTOM BOTTOM + 1 TOP TOP - 1 TOP - 2 New OCRnx Value /8) clk_I/O TOP BOTTOM BOTTOM + 1 TOP TOP - 1 ...

Page 116

... When the OC1A or OC1B is connected to the pin, the function of the COM1x1:0 bits is depen- dent of the WGM13:0 bits setting. WGM13:0 bits are set to a Normal or a CTC mode (non-PWM). Table 4-39. COM1A1/COM1B1 Table 4-40 PWM mode. Table 4-40. COM1A1/COM1B1 Note: Atmel ATA5771/73/74 116 COM1A1 COM1A0 COM1B1 R/W R/W ...

Page 117

... A special case occurs when OCR1A/OCR1B equals TOP and COM1A1/COM1B1 is set. Section 4.16.9.4 “Phase Correct PWM Mode” on page 110 Table 4-42 on page 106). Atmel ATA5771/73/74 Description Normal port operation, OC1A/OC1B disconnected. WGM13=0: Normal port operation, OC1A/OC1B disconnected. WGM13=1: Toggle OC1A on Compare Match, OC1B reserved ...

Page 118

... When a capture is triggered according to the ICES1 setting, the counter value is copied into the Input Capture Register (ICR1). The event will also set the Input Capture Flag (ICF1), and this can be used to cause an Input Capture Interrupt, if this interrupt is enabled. Atmel ATA5771/73/74 118 (1) ...

Page 119

... I clk /256 (From prescaler) I clk /1024 (From prescaler) I External clock source on T1 pin. Clock on falling edge External clock source on T1 pin. Clock on rising edge FOC1A FOC1B – – Atmel ATA5771/73/74 87 – – – – Fig- TCCR1C 119 ...

Page 120

... The Output Compare Registers are 16-bit in size. To ensure that both the high and low bytes are written simultaneously when the CPU writes to these registers, the access is performed using an 8-bit temporary high byte register (TEMP). This temporary register is shared by all the other 16-bit registers. See Atmel ATA5771/73/74 120 7 6 ...

Page 121

... R/W R/W R Section 4.16.3 “Accessing 16-bit Registers” on page – – ICIE1 Section 4.12 “Interrupts” on page Section 4.12 “Interrupts” on page Section 4.12 “Interrupts” on page Atmel ATA5771/73/ ICR1[15:8] ICR1[7:0] R/W R/W R – – OCIE1B OCIE1A ...

Page 122

... The setting of this flag is dependent of the WGM13:0 bits setting. In Normal and CTC modes, the TOV1 flag is set when the timer overflows. See behavior when using another WGM13:0 bit setting. TOV1 is automatically cleared when the Timer/Counter1 Overflow Interrupt Vector is exe- cuted. Alternatively, TOV1 can be cleared by writing a logic one to its bit location. Atmel ATA5771/73/74 122 – ...

Page 123

... Timer/Counter clock pulse is generated. 9137E–RKE–12/10 ). Alternatively, one of four taps from the prescaler can be CLK_I/O /256 /1024. CLK_I clk I/O Synchronization Atmel ATA5771/73/74 Figure 4-50 pulse for each positive (CSn2 negative Edge Detector /8, f /64, CLK_I/O CLK_I/O ). The Tn shows a ). The latch is clk ...

Page 124

... Timer/Counter start counting. • Bit 0 – PSR10: Prescaler 0 Reset Timer/Counter n When this bit is one, the Timer/Countern prescaler will be Reset. This bit is normally cleared immediately by hardware, except if the TSM bit is set. Atmel ATA5771/73/74 124 < f /2) given a 50/50% duty cycle. Since the edge detector ...

Page 125

... USIDR 4-bit Counter 1 0 [1] USISR 2 USICR Atmel ATA5771/73/74 Figure 4-52. For the actual placement of I/O Section 4.9.10 “Register Descrip- DO DI/SDA TIM0 COMP 0 USCK/SCL 1 CLOCK HOLD Two-wire Clock Control Unit (Output only) (Input/Open Drain) (Input/Open Drain) 125 ...

Page 126

... The Counter Overflow (interrupt) Flag, or USIOIF, can therefore be used to determine when a transfer is completed. The clock is generated by the Master device software by tog- gling the USCK pin via the PORT Register or by writing a one to the USITC bit in USICR. Atmel ATA5771/73/74 126 Bit7 ...

Page 127

... Idle mode. Depending of the protocol used the slave device can now set its out- put to high impedance. 9137E–RKE–12/10 ( Reference ) 1 2 USCK USCK DO MSB 6 DI MSB (Figure Atmel ATA5771/73/ Figure 4-54. At the top of the figure is a USCK cycle 4-54), a bus transfer involves the following steps: ...

Page 128

... The fourth and fifth instruction set Three-wire mode, positive edge Shift Register clock, count at USITC strobe, and toggle USCK. The loop is repeated 16 times. The following code demonstrates how to use the USI module as a SPI Master with maximum speed (f SPITransfer_Fast: Atmel ATA5771/73/74 128 out USIDR,r16 ldi r16,(1< ...

Page 129

... USI Counter Overflow Flag is set. 9137E–RKE–12/10 in r16,USIDR ldi r16,(1<<USIWM0)|(1<<USICS1) out USICR,r16 out USIDR,r16 ldi r16,(1<<USIOIF) out USISR,r16 in r16, USISR sbrs r16, USIOIF rjmp SlaveSPITransfer_loop in r16,USIDR ret Atmel ATA5771/73/74 129 ...

Page 130

... The clock is generated by the master by toggling the USCK pin via the PORT Register. The data direction is not given by the physical layer. A protocol, like the one used by the TWI-bus, must be implemented to control the data flow. Atmel ATA5771/73/74 130 Bit7 Bit6 ...

Page 131

... Figure 4-57. Start Condition Detector, Logic Diagram 9137E–RKE–12/10 SDA SCL ADDRESS R (Figure (Figure SDA SCL Write( USISIF) Atmel ATA5771/73/ ACK DATA ACK DATA E 4-56), a bus transfer involves the following steps: 4-57) detects the start condition and sets the CLR CLR 9 ...

Page 132

... USICS1 bit. 4.18.4.5 Software Interrupt The counter overflow interrupt can be used as a software interrupt triggered by a clock strobe. Atmel ATA5771/73/74 132 Figure 4-57 on page 131. The SDA line is delayed (in Section 4.9.1 “Clock Systems and their Distribution” on page for further details ...

Page 133

... A start condition interrupt will wakeup the processor from all sleep modes. 9137E–RKE–12/ MSB MSB R/W R/W R/W R USISIF USIOIF USIPF USIDC R/W R/W R Atmel ATA5771/73/ LSB LSB R/W R/W R/W R USICNT3 USICNT2 USICNT1 USICNT0 R/W R/W R/W R USIBR USIDR ...

Page 134

... Bit 7 – USISIE: Start Condition Interrupt Enable Setting this bit to one enables the Start Condition detector interrupt. If there is a pending inter- rupt when the USISIE and the Global Interrupt Enable Flag is set to one, this will immediately be executed. See the USISIF bit description in further details. Atmel ATA5771/73/74 134 ...

Page 135

... SCL line is also held low when a counter overflow occurs, and is held low until the Counter Overflow Flag (USIOIF) is cleared. 1. The DI and USCK pins are renamed to Serial Data (SDA) and Serial Clock (SCL) respec- tively to avoid confusion between the modes of operation. Atmel ATA5771/73/74 “USISR – USI Status Register” on page 133 Table 4-44. ...

Page 136

... When an external clock source is selected (USICS1 = 1) and the USICLK bit is set to one, writ- ing to the USITC strobe bit will directly clock the 4-bit counter. This allows an early detection of when the transfer is done when operating as a master device. Atmel ATA5771/73/74 136 shows the relationship between the USICS1..0 and USICLK setting and clock Relations between the USICS1 ...

Page 137

... Table 4-46. Analog Comparator Multiplexed Input ADEN MUX4.. 00000 1 0 00001 1 0 00010 1 0 00011 1 0 00100 1 0 00101 1 0 00110 1 0 00111 Atmel ATA5771/73/74 (1) Analog Comparator Negative Input AIN1 AIN1 ADC0 ADC1 ADC2 ADC3 ADC4 ADC5 ADC6 ADC7 Table 137 ...

Page 138

... Alternatively, ACI is cleared by writing a logic one to the flag. • Bit 3 – ACIE: Analog Comparator Interrupt Enable When the ACIE bit is written logic one and the I-bit in the Status Register is set, the Analog Comparator interrupt is activated. When written logic zero, the interrupt is disabled. Atmel ATA5771/73/74 138 7 6 ...

Page 139

... ACIS1/ACIS0 Settings ACIS0 Interrupt Mode 0 0 Comparator Interrupt on Output Toggle Reserved 1 0 Comparator Interrupt on Falling Output Edge Comparator Interrupt on Rising Output Edge ADC7D ADC6D ADC5D R/W R/W R Atmel ATA5771/73/74 4-47 ADC4D ADC3D ADC2D ADC1D R/W R/W R/W R ADC0D DIDR0 R/W 0 139 ...

Page 140

... A block diagram of the ADC is shown in 4-59 on page Internal reference voltage of nominally 1.1V is provided On-chip. Alternatively, V used as reference voltage for single ended channels. There is also an option to use an exter- nal voltage reference and turn-off the internal voltage reference. Atmel ATA5771/73/74 140 ADC Input Voltage Range CC ® ...

Page 141

... CC INTERNAL REFERENCE 1.1V TEMPERATURE SENSOR ADC8 AGND POS. INPUT MUX + - NEG. INPUT MUX Atmel ATA5771/73/74 ADC CONVERSION COMPLETE IRQ INTERRUPT FLAGS 15 ADC CTRL. & STATUS A ADC DATA REGISTER REGISTER (ADCSRA) (ADCH/ADCL) TRIGGER SELECT PRESCALER CONVERSION LOGIC SAMPLE & HOLD COMPARATOR 10-BIT DAC ...

Page 142

... Note that an Interrupt Flag will be set even if the specific interrupt is disabled or the Global Interrupt Enable bit in SREG is cleared. A con- version can thus be triggered without causing an interrupt. However, the Interrupt Flag must be cleared in order to trigger a new conversion at the next interrupt event. Atmel ATA5771/73/74 142 9137E–RKE–12/10 ...

Page 143

... ADC can be higher than 200 kHz to get a higher sample rate. 9137E–RKE–12/10 ADTS[2:0] ADIF SOURCE EDGE DETECTOR SOURCE n ADSC ADEN START CK ADPS0 ADPS1 ADPS2 Atmel ATA5771/73/74 START ADATE CONVERSION Reset 7-BIT ADC PRESCALER ADC CLOCK SOURCE PRESCALER CLK ADC LOGIC 143 ...

Page 144

... In Free Running mode, a new conversion will be started immediately after the conversion completes, while ADSC remains high. For a summary of conversion times, see page Figure 4-62. ADC Timing Diagram, First Conversion (Single Conversion Mode) Cycle Number ADC Clock ADEN ADSC ADIF ADCH ADCL Atmel ATA5771/73/74 144 146 MUX and REFS Update ...

Page 145

... Sample & Prescaler Hold Reset MUX and REFS Update One Conversion Cycle Number ADC Clock ADSC ADIF ADCH ADCL Conversion Complete Atmel ATA5771/73/74 Next Conversion Sign and MSB of Result LSB of Result Conversion Complete One Conversion Sign and MSB of Result LSB of Result ...

Page 146

... Since the next conversion has already started automatically, the next result will reflect the previous channel selection. Subsequent conversions will reflect the new channel selection. Atmel ATA5771/73/74 146 ADC Conversion Time Sample & Hold (Cycles from Start of Conversion) 14 ...

Page 147

... If another interrupt wakes up the CPU before the ADC conversion is com- plete, that interrupt will be executed, and an ADC Conversion Complete interrupt request will be generated when the ADC conversion completes. The CPU will remain in active mode until a new sleep command is executed. Atmel ATA5771/73/74 can be selected as REF Figure 4-66 ...

Page 148

... The lowest code is read as 0, and the highest code is read as 2 Several parameters describe the deviation from the ideal behavior: • Offset: The deviation of the first transition (0x000 to 0x001) compared to the ideal transition (at 0.5 LSB). Ideal value: 0 LSB. Figure 4-67. Offset Error Atmel ATA5771/73/74 148 I IH ADCn ...

Page 149

... Differential Non-linearity (DNL): The maximum deviation of the actual code width (the interval between two adjacent transitions) from the ideal code width (1 LSB). Ideal value: 0 LSB. 9137E–RKE–12/10 Output Code Output Code Atmel ATA5771/73/74 Gain Error Ideal ADC Actual ADC ...

Page 150

... Single Ended Conversion For single ended conversion, the result is where V Table 4-50 on page 152 0x3FF represents the selected reference voltage minus one LSB. The result is presented in one-sided form, from 0x3FF to 0x000. Atmel ATA5771/73/74 150 Output Code 0x3FF 1 LSB 0x000 0 ADC ...

Page 151

... POS the selected voltage reference. The result is presented in two’s complement form, REF C and the accuracy of the temperature measurement is +/- ° Temperature vs. Sensor Output Voltage (Typical Case) -40°C 243 mV Atmel ATA5771/73/74 V – 1024 NEG GAIN V REF the voltage on the negative input pin, ...

Page 152

... AREF higher than (V allowed to connect internal voltage reference to AREF pin external voltage is being applied to it already. Internal voltage reference is connected AREF pin when REFS1:0 is set to value ‘11’. Table 4-50. REFS1 Atmel ATA5771/73/74 152 Table 4-49 on page 151 T = {[(ADCH << ADCL] - TOS ...

Page 153

... Section 4.20.9 “Temperature Measurement” on page 151 3. For offset calibration only .See on page 141 for details of selections of differential input channel selections as Table 4-52 on page Section 4.20.3 “ADC Operation” on page 141 Atmel ATA5771/73/74 Table 4-51 for details. If these bits are changed (1) 001000 - 011111 (3) ...

Page 154

... Table 4-52. Positive Differential 1. Atmel ATA5771/73/74 154 Differential Input channel Selections. Negative Differential Input Input ADC0 (PA0) ADC0 (PA0) ADC1 (PA1) ADC3 (PA3) ADC0 (PA0) ADC1 (PA1) ADC2 (PA2) ADC3 (PA3) ADC1 (PA1) ADC2 (PA2) ADC3 (PA3) ADC0 (PA0) ADC1 (PA1) ...

Page 155

... Bits 2:0 – ADPS2:0: ADC Prescaler Select Bits These bits determine the division factor between the system clock frequency and the input clock to the ADC. 9137E–RKE–12/ ADEN ADSC ADATE ADIF R/W R/W R/W R Atmel ATA5771/73/ ADIE ADPS2 ADPS1 ADPS0 R/W R/W R/W R ADCSRA 155 ...

Page 156

... If ADLAR is set, the result is left adjusted. If ADLAR is cleared (default), the result is right adjusted. • ADC9:0: ADC Conversion Result These bits represent the result from the conversion, as detailed in version Result” on page Atmel ATA5771/73/74 156 ADC Prescaler Selections ADPS2 ADPS1 ...

Page 157

... Running mode (ADTS[2:0]=0) will not cause a trigger event, even if the ADC Interrupt Flag is . set 9137E–RKE–12/ BIN ACME – ADLAR R/W R/W R/W R ® ATtiny44V and will always read as what was wrote there. 156. Atmel ATA5771/73/ – ADTS2 ADTS1 ADTS0 R/W R/W R/W R 157. Section 4.20.10.3 “ADCL ADCSRB 157 ...

Page 158

... The corresponding PIN register bit will always read as zero when this bit is set. When an analog signal is applied to the ADC7..0 pin and the digital input from this pin is not needed, this bit should be written logic one to reduce power consumption in the digital input buffer. Atmel ATA5771/73/74 158 ADC Auto Trigger Source Selections ...

Page 159

... The system clock is not affected by debugWIRE and will always be the clock source selected by the CKSEL Fuses. 9137E–RKE–12/10 ® ® AVR instructions in the CPU and to program the different dW dW(RESET) GND shows the schematic of a target MCU, with debugWIRE enabled, and the emula- Atmel ATA5771/73/74 1.8 - 5.5V VCC 159 ...

Page 160

... Initial Value The DWDR Register provides a communication channel from the running program in the MCU to the debugger. This register is only accessible by the debugWIRE and can therefore not be used as a general purpose register in the normal operations. Atmel ATA5771/73/74 160 will not work. CC ® ...

Page 161

... SPMCSR also erased after a system reset. Note that it is not possible to write more than one time to each address without erasing the temporary buffer. If the EEPROM is written in the middle of an SPM Page Load operation, all data loaded will be lost. 9137E–RKE–12/10 Atmel ATA5771/73/74 161 ...

Page 162

... Page Erase and Page Write operation. The LPM instruction uses the Z-pointer to store the address. Since this instruction addresses the Flash byte-by-byte, also the LSB (bit Z0) of the Z-pointer is used. Figure 4-72. Addressing the Flash During SPM Note: Atmel ATA5771/73/74 162 ...

Page 163

... FLB7 FLB6 FLB5 FLB4 Table 4-59 on page 167 for detailed description and mapping of the Fuse FHB7 FHB6 FHB5 FHB4 , the Flash program can be corrupted because the supply voltage is CC Atmel ATA5771/73/ – – LB2 LB1 Table 4-60 on page 168 FLB3 FLB2 ...

Page 164

... Bit 3 – RFLB: Read Fuse and Lock Bits An LPM instruction within three cycles after RFLB and SPMEN are set in the SPMCSR Regis- ter, will read either the Lock bits or the Fuse bits (depending the Z-pointer) into the destination register. See page 163 Atmel ATA5771/73/74 164 ® ® AVR ...

Page 165

... SPM instruction is executed within four clock cycles. During Page Erase and Page Write, the SPMEN bit remains high until the operation is completed. Writing any other combination than “10001”, “01001”, “00101”, “00011” or “00001” in the lower five bits will have no effect. 9137E–RKE–12/10 Atmel ATA5771/73/74 165 ...

Page 166

... Program memory can be read out via the debugWIRE interface when the DWEN fuse is pro- grammed, even if the Lock Bits are set. Thus, when Lock Bit security is required, should always debugWIRE be disabled by clearing the DWEN fuse. Table 4-56. LB2 LB1 Note: Table 4-57. LB Mode Notes: Atmel ATA5771/73/74 166 (1) Lock Bit Byte Lock Bit Byte Bit ...

Page 167

... Data Memory Lock Bits” on page 3. The SPIEN Fuse is not accessible in SPI Programming mode. 4. See Table 4-16 on page 50 for details. 5. See Table 8-4 on page 190 for BODLEVEL Fuse decoding. Atmel ATA5771/73/74 Table 4-59 to Table 4-60 on page 168 Default Value 1 (unprogrammed) 1 (unprogrammed) 1 (unprogrammed) ...

Page 168

... Signature area of the ATtiny44V has one byte of calibration data for the internal RC Oscillator. This byte resides in the high byte of address 0x000. During reset, this byte is automatically written into the OSCCAL Register to ensure correct frequency of the calibrated RC Oscillator. Atmel ATA5771/73/74 168 Fuse Low Byte ...

Page 169

... GND 1. If the device is clocked by the internal Oscillator need to connect a clock source to the CLKI pin. Pin Mapping Serial Programming Symbol Pins MOSI PA6 MISO PA5 SCK PA4 Atmel ATA5771/73/74 PCWORD No. of Pages PCPAGE PC[4:0] 64 PC[10:5] PCWORD No. of Pages PCPAGE EEA[1:0] 64 EEA[7:2] ...

Page 170

... MSB of the address. If polling (RDY/BSY) is not used, the user must wait at least t serial programming interface before the Flash write operation completes can result in incorrect programming. Atmel ATA5771/73/74 170 < 12 MHz, 3 CPU clock cycles for f ck < 12 MHz, 3 CPU clock cycles for f ck ® ...

Page 171

... In a chip erased device, no 0xFFs in the data file(s) need to be pro- Table 4-65 on page power off. CC Minimum Wait Delay Before Writing the Next Flash or EEPROM Location Symbol t WD_FLASH t WD_EEPROM t WD_ERASE t WD_FUSE Atmel ATA5771/73/74 Table 4-65 on WD_EEPROM 171 chip erased device, no Minimum Wait Delay 4.5 ms 4.0 ms 4.0 ms 4.5 ms 171 ...

Page 172

... Refer to the correspondig section for Fuse and Lock bits, Calibration and Signature bytes and Page size. 6. Instructions accessing program memory use a word address. This address may be random within the page range. 7. See htt://www.atmel.com/avr for Application Notes regarding programming and programmers. Atmel ATA5771/73/74 172 and Figure 4-74 on page 173 describes the Instruction set ...

Page 173

... Serial Programming Instruction Byte 3 Byte 4 Adr LSB 0 Page Buffer Page Offset Page 0 Page 1 Page 2 Page N-1 Program Memory/ EEPROM Memory Atmel ATA5771/73/74 Write Program Memory Page/ Write EEPROM Memory Page Byte 1 Byte 2 Byte 3 Adr MSB Bit 15 B Page Number Figure 4-74 on page Byte 4 0 ...

Page 174

... SDI SII SDO SCI The minimum period for the Serial Clock Input (SCI) during High-voltage Serial Programming is 220 ns. Table 4-68. Pin PA0 PA1 PA2 Atmel ATA5771/73/74 174 ® ATtiny44V. +11.5 - 12.5V PB3 (RESET) SCI PB0 GND Pin Name Mapping Pin Name ...

Page 175

... High-voltage Reset Characteristics RESET Pin High-voltage Threshold V HVRST 11.5V 11.5V 1. The EEPROM memory is preserved during Chip Erase if the EESAVE Fuse is programmed. Atmel ATA5771/73/74 Table 4-70 on page Table 4-68 on page 174 to “000” and wait at least Minimum High-voltage Period for Latching Prog_enable (1) memories plus Lock bits ...

Page 176

... Figure 4-76. Addressing the Flash which is Organized in Pages Figure 4-77. High-voltage Serial Programming Waveforms SDI MSB PB0 SII MSB PB1 SDO MSB PB2 SCI 0 1 PB3 Atmel ATA5771/73/74 176 Figure 8-5 on page 194, PCMSB PROGRAM PCPAGE COUNTER PAGE ADDRESS WITHIN THE FLASH PROGRAM MEMORY PAGE Section 4.23.5 “ ...

Page 177

... Power-off sequence Set SCI to “0”. Set RESET to “1”. Turn V 9137E–RKE–12/10 Table 4-70 on page 178): 178. 178. CC Atmel ATA5771/73/74 Table 8-7 on page 193. When programming the Table 4-70 on page Table 4-70 on page power off. 178): Table 4-70 177 ...

Page 178

... The EEPROM is written page-wise. But only the bytes that are loaded into the page are actually written to the EEPROM. Page-wise EEPROM access is more efficient when multiple bytes are to be written to the same page. Note that auto-erase of EEPROM is not available in High-voltage Serial Programming, only in SPI Programming. Atmel ATA5771/73/74 178 ® ...

Page 179

... I_HGFE_DCBx_xx 0_0000_0000_00 0_0000_0000_00 0_0110_1010_00 0_0110_1110_00 x_xxxx_xxxx_xx x_xxxx_xxJx_xx Atmel ATA5771/73/74 ATtiny44V (Continued) Instr.4 Operation Remarks Wait after Instr. 2 until SDO goes high. Repeat Instr for each loaded EEPROM page until the entire EEPROM or all data is programmed. 0_0000_0000_00 Repeat Instr for each new 0_0110_1101_00 address ...

Page 180

... The EEPROM is written page-wise. But only the bytes that are loaded into the page are actually written to the EEPROM. Page-wise EEPROM access is more efficient when multiple bytes are to be written to the same page. Note that auto-erase of EEPROM is not available in High-voltage Serial Programming, only in SPI Programming. Atmel ATA5771/73/74 180 ® ...

Page 181

... PXY PXY PXY PXY PXY f/4 CLK XTO C4 st harmonic. Therefore the position should be selected that the XTO runs on the load resonance frequency of the 4 Atmel ATA5771/73/ nF/X7R is recommended and allowing the possibility of realiz- 2 VDD VS GND PXY PXY PXY PXY PXY Power ...

Page 182

... Figure 5-2. Table 5-1. Bill of Material Component 315 MHz 433.92MHz L1 100nH L2 39nH C1 1nF C2 3.9pF C3 27pF C4 3.9pF C5 68nF Atmel ATA5771/73/74 182 Typical ASK Application Atmel VCC 23 VDD C7 PB0/XTAL1 C6 R3 PB1/XTAL2 PB3/RESET PB2 PA7 ADC7 R2 R1 Type/ Value Manufacturer Note 868.3MHz LL1608-FSL/ 82nH ...

Page 183

... PA7 ADC7 R2 R1 FSK Modulation is achieved by switching on and off an additional capacitor between the XTAL load capacitor and GND. This is done using a MOS switch controlled by a microcontroller output. Atmel ATA5771/73/74 This cap must placed as close as possible to the VDD ® ATA577x VCC C8 T1 ...

Page 184

... C3 27pF C4 3.9pF C5 68nF C6 100nF C7 100nF C8 3.9pF C9 18pF T1 Q1 9.843750MHz 13.56MHz R1 100k R2 100k R3 10k Atmel ATA5771/73/74 184 Type/ Value Manufacturer Note 868.3MHz LL1608-FSL/ 82nH 22nH TOKO LL1608-FSL/ 27nH 2.2nH TOKO GRM1885C/ 1nF 1nF Murata GRM1885C/ 2.7pF 1.5pF Murata GRM1885C/ 16pF 4.3pF ...

Page 185

... P tot stg T amb V maxPA_ENABLE ESD Protection Circuit of the Transmitter VS CLK GND Note: +0.5V CC (1) ........................±5.0mA Atmel ATA5771/73/74 Minimum Maximum 5 100 150 –55 +125 –55 +125 –0 0.3) S ANT1 PA_ENABLE ANT2 XTAL Stresses beyond those listed under “Absolute Maximum Ratings” may cause permanent damage to the device. ...

Page 186

... Output power Output power variation for the full temperature range Note higher than 3.6V, the maximum voltage will be reduced to 3.6V. S Atmel ATA5771/73/74 186 Symbol R thJA = 25°C. amb Transmitter (T5750/3/4) Typ. < 10nA Max. 350nA Typ ...

Page 187

... Load Duty cycle of the modulation signal = 50% Duty cycle of the modulation signal = 50% Low level input voltage High level input voltage Input current high Low level input voltage High level input voltage Input current high Atmel ATA5771/73/74 Symbol Min. Typ. Max. 0 8.0 P Out_typ 0 7 ...

Page 188

... The sum of all IOH, for all ports, should not exceed 60mA. If IOH exceeds the test condition, VOH may exceed the related specification. Pins are not guaranteed to source current greater than the listed test condition. Pull up driving strenght of the PB3 RESET pad is weak. Atmel ATA5771/73/74 188 (1) Condition Min ...

Page 189

... External Clock Drive Waveforms Figure 8-2. External Clock Drive Waveforms V IL1 9137E–RKE–12/10 CC curve is linear between 1.8V < MHz 4 MHz Safe Operating Area 1.8V 2. 1.8V to 3.6V V IH1 Atmel ATA5771/73/ shown in Figure 8-1, the Maximum Frequency CC < 3.6V CC 3.6V Temperature – +85 C Accuracy ±25% 189 ...

Page 190

... For devices where this is the case, the device BOT is tested down drops to a voltage where correct operation of the microcontroller is no longer guaranteed Atmel ATA5771/73/74 190 External Clock Drive Parameter Clock Frequency Clock Period ...

Page 191

... T = –40°C to +85° 1.8V 1.8V, CC Ref ADC clock = 200kHz –3 –40°C to +85°C A Free Running Conversion T = –40°C to +85°C A GND Atmel ATA5771/73/74 Typ Max 10 2 4.0 2 4.0 0.5 1.5 0.2 0.7 –3.0 +5.0 +1.5 +3.5 65 260 50 200 1 ...

Page 192

... Gain Error Offset Error Clock Frequency Conversion Time V Reference Voltage REF V Input Voltage IN V Input Differential Voltage DIFF Atmel ATA5771/73/74 192 = –40°C to +85°C, unless otherwise noted A Condition Differential conversion, gain = 1x BIPOLAR mode only T = –40°C to +85° 1.8V to 3.6V ...

Page 193

... Oscillator Period (Atmel ATtiny44VV) SCK Pulse Width High SCK Pulse Width Low MOSI Setup to SCK High MOSI Hold after SCK High SCK Low to MISO Valid for f < 12MHz CLCL ck CLCL Atmel ATA5771/73/ SLSH SHOX t SHSL t SLIV = –40°C to +85° Min ...

Page 194

... High-voltage Serial Programming Characteristics Figure 8-5. Table 8-8. Symbol t WLWH_PFB Atmel ATA5771/73/74 194 High-voltage Serial Programming Timing CC CK High-voltage Serial Programming Characteristics T = 25°C ± 10 5.0V ± 10% (Unless otherwise noted Parameter t SCI (PB0) Pulse Width High SHSL t SCI (PB0) Pulse Width Low ...

Page 195

... L CC Active Supply Current vs. Low Frequency (0.1 - 1.0MHz) - Temp. = 25°C ACTIVE CURRENT vs . LOW FREQUENCY 0.1 - 1.0 MHz - Temperature = 25˚C 1.2 1 0.8 0.6 0.4 0 0.1 0.2 0.3 0.4 Frequency (MHz) Atmel ATA5771/73/74 0.5 0.6 0.7 0.8 0 5.5 V 5.0 V 4.5 V 3.3 V 3 195 ...

Page 196

... Figure 8-7. Figure 8-8. Atmel ATA5771/73/74 196 Active Supply Current vs. frequency (1 - 20MHz) - Temp. = 25°C ACTIVE CURRENT vs . FREQUENCY MHz - Temperature = 25˚ Frequency (MHz) Active Supply Current vs. V ACTIVE CURRENT INTERNAL RC OSCILLATOR, 8 MHz 2 (Internal RC Oscillator, 8MHz 4 (V) CC 5.5 V 5.0 V 4 ...

Page 197

... ACTIVE CURRENT INTERNAL RC OSCILLATOR, 1MHz 1.4 1.2 1 0.8 0.6 0.4 0.2 0 2.5 3 3.5 ACTIVE CURRENT INTERNAL RC OSCILLATOR, 128 KHz 0.2 0.16 0.12 0.08 0.04 0 2.5 3 3.5 Atmel ATA5771/73/74 (Internal RC Oscillator, 1MHz 4 (V) CC (Internal RC Oscillator, 128kHz 4 (V) CC 125 ˚C 85 ˚C 25 ˚C -40 ˚C 5.5 -40 ˚ ...

Page 198

... Idle Supply Current Figure 8-11. Idle Supply Current vs. V Figure 8-12. Idle Supply Current vs. V Atmel ATA5771/73/74 198 CC IDLE CURRENT INTERNAL RC OSCILLATOR, 8 MHz 2 1.8 1.6 1.4 1.2 1 0.8 0.6 0.4 0.2 0 2.5 3 3.5 CC IDLE CURRENT INTERNAL RC OSCILLATOR, 1 MHz 0.35 0.3 ...

Page 199

... Additional Current Consumption for the Different I/O Modules (Absolute Values) PRR Bit MHz CC PRTIM1 6.6 uA PRTIM0 8.7 uA PRUSI 5.5 uA PRADC 22 uA Atmel ATA5771/73/74 (Internal RC Oscillator, 8MHz 4 (V) CC Section 4.10.6 “Power Reduction Regis- Typical Numbers MHz 125 ˚ ...

Page 200

... Power-down Supply Current Figure 8-14. Power-down Supply Current vs. V Figure 8-15. Power-down Supply Current vs. V Atmel ATA5771/73/74 200 P OWER-DOWN CURRENT WATCHDOG TIMER DISABLED 5 4.5 4 3.5 3 2.5 2 1.5 1 0.5 0 2.5 3 3.5 P OWER-DOWN CURRENT WATCHDOG TIMER ENABLED 2.5 3 3.5 (Watchdog Timer Disabled) ...