LAN7500I-ABZJ SMSC, LAN7500I-ABZJ Datasheet - Page 31

LAN7500I-ABZJ

Manufacturer Part Number

LAN7500I-ABZJ

Description

IC USB-10/100/1K ETH CTRL 56QFN

Manufacturer

SMSC

Specifications of LAN7500I-ABZJ

Design Resources

LAN7500I BOM LAN7500I Schematic

Controller Type

Ethernet Controller, USB 2.0 to 10/100/1K

Interface

USB/Serial

Voltage - Supply

1.2V, 2.5V, 3.3V

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

56-VFQFN Exposed Pad

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Current - Supply

-

Other names

638-1109

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Part Number:

LAN7500I-ABZJ

Manufacturer:

MICROCHIP/微芯

Quantity:

20 000

Hi-Speed USB 2.0 to 10/100/1000 Ethernet Controller

Datasheet

SMSC LAN7500/LAN7500i

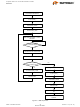

The Host Processor is connected to a Chipset containing the Host USB Controller (HC). The USB Host

Controller interfaces to LAN7500/LAN7500i via the DP/DM USB signals. An Embedded Controller (EC)

signals the Chipset and the Host processor to power up via an Enable signal. The EC interfaces to

LAN7500/LAN7500i via four signals. The PME signal is an input to the EC from the device that

indicates the occurrence of a wakeup event. The VBUS_DET output of the EC is used to indicate bus

power availability. The PME_CLEAR (nRESET) signal is used to clear the PME. The

PME_MODE_SEL signal is sampled by the device when PME_CLEAR (nRESET) is asserted and is

used by the device to determine whether it should remain in PME mode or resume normal operation.

GPIO pins are used for PME handling.

GPIO6

The application scenario in

off, the EC is operational, and the device is in PME mode, waiting for a wake event to occur. A wake

event will result in the device signaling a PME event to the EC, which will then wake up the Host

Processor and Chipset via the Enable signal. The EC asserts VBUS_DET after the USB bus is

powered, sets PME_MODE_SEL to determine whether the device is to begin normal operation or

continue in PME mode, and asserts PME_CLEAR (nRESET) to clear the PME.

The following wake events are supported:

In order to facilitate PME mode of operation, the

must be set and all remaining

or level signaling, buffer type, and GPIO PME WOL selection. The PME event is signaled on GPIO5.

The PME_MODE_SEL pin (GPIO6) must be driven to the value that determines whether or not the

device remains in PME mode of operation (1) or resumes normal operation (0) when the PME is

recognized and cleared by the EC via PME_CLEAR (nRESET) assertion.

Note: When in PME mode or nRESET will always cause the contents of the EEPROM to be

Wakeup Pin(s)

The GPIO pins not reserved for PME handling have the capability to wake up the device when

operating in PME mode. In order for a GPIO to generate a wake event, it’s enable bit must be set

in the

appropriate. During PME mode of operation, the GPIOs used for signaling

not affected by the values set in the corresponding bits of

GPIOs 0 - 4 and 7 - 10 are available as wakeup pins in PME mode of operation and are active

low by default.

Magic Packet

Reception of a Magic Packet when in PME mode will result in a PME being asserted.

Perfect DA match of Physical address

Reception of an Ethernet frame whose Destination address matches the device’s MAC address will

result in a PME being asserted.

PHY Link Up

Detection of a PHY link partner when in PME mode will result in a PME being asserted.

is reserved for use as the PME_MODE_SEL input.

reloaded.

GPI0[11:8] Wakeup Enables

Figure 4.1

GPIO PME Flags

DATASHEET

assumes that the Host Processor and the Chipset are powered

or

GPIO5

GPIO[7:0] Wakeup Enables

31

is reserved for use as an output to signal the PME.

GPIO PME Enable

field bits must be appropriately configured for pulse

GPIO[7:0] Wakeup

bit in the

bytes of the EEPROM, as

(GPIO5

GPIO PME Flags

Revision 1.0 (11-01-10)

Enables.

and GPIO6) are

field,