WM9090ECS/R Wolfson Microelectronics, WM9090ECS/R Datasheet

WM9090ECS/R

Specifications of WM9090ECS/R

Related parts for WM9090ECS/R

WM9090ECS/R Summary of contents

Page 1

... WM9090 SPKVDD Boost Amplifier Class D Driver SPKOUTP Speaker SPKOUTN +6dB to -57dB in 1dB steps HPOUTL DC Offset Correction +6dB to -57dB in 1dB steps HPOUTR DC Offset Correction CPVOUTP CPVOUTN Charge Pump CPCA CPCB GND AVDD Pre-Production, January 2010, Rev 3.0 Copyright ©2010 Wolfson Microelectronics plc ...

Page 2

WM9090 DESCRIPTION ....................................................................................................... 1 FEATURES............................................................................................................. 1 APPLICATIONS ..................................................................................................... 1 BLOCK DIAGRAM ................................................................................................. 1 TABLE OF CONTENTS ......................................................................................... 2 PIN CONFIGURATION ........................................................................................... 4 ORDERING INFORMATION .................................................................................. 4 PIN DESCRIPTION ................................................................................................ 5 ABSOLUTE MAXIMUM RATINGS ......................................................................... 6 RECOMMENDED OPERATING CONDITIONS ..................................................... 6 ...

Page 3

Pre-Production DC SERVO READBACK ........................................................................................................................... 48 REFERENCE VOLTAGES AND MASTER BIAS .......................................................... 49 POWER MANAGEMENT ............................................................................................. 50 THERMAL SHUTDOWN .............................................................................................. 52 SOFTWARE RESET AND CHIP ID ............................................................................. 52 REGISTER MAP ................................................................................................... 53 REGISTER BITS BY ADDRESS .................................................................................. 55 APPLICATIONS INFORMATION ...

Page 4

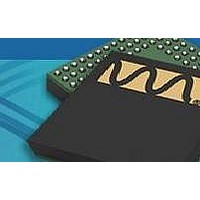

... WM9090 PIN CONFIGURATION 20-bump CSP package; Top View ORDERING INFORMATION ORDER CODE TEMPERATURE RANGE WM9090ECS/R -40°C to +85°C Note: Reel quantity = 3500 w PACKAGE MOISTURE SENSITIVITY LEVEL 20-ball W-CSP MSL1 (Pb-free, Tape and reel) Pre-Production PEAK SOLDERING TEMPERATURE 260°C PP, January 2010, Rev 3.0 ...

Page 5

Pre-Production PIN DESCRIPTION PIN NO NAME A1 SPKOUTN Analogue Output A2 SPKVDD Supply A3 DNC A4 IN2P Analogue Input A5 IN2N Analogue Input B1 SPKOUTP Analogue Output B2 GND Supply B3 DNC B4 IN1N Analogue Input B5 IN1P Analogue Input ...

Page 6

WM9090 ABSOLUTE MAXIMUM RATINGS Absolute Maximum Ratings are stress ratings only. Permanent damage to the device may be caused by continuously operating at or beyond these limits. Device functional operating limits and guaranteed performance specifications are given under Electrical Characteristics ...

Page 7

Pre-Production THERMAL PERFORMANCE Thermal analysis should be performed in the intended application to prevent the WM9090 from exceeding maximum junction temperature. Several contributing factors affect thermal performance most notably the physical properties of the mechanical enclosure, location of the device ...

Page 8

WM9090 ELECTRICAL CHARACTERISTICS Test Conditions SPKVDD = 3.6V, AVDD=1.8V, GND=0V, T PARAMETER Analogue Input Pins Maximum Full-Scale input signal level - IN1P/N and IN2P/N Input Resistance Input Capacitance Input Programmable Gain Amplifiers (PGAs) IN1A, IN1B, IN2A and IN2B Minimum Programmable ...

Page 9

Pre-Production Test Conditions SPKVDD = 3.6V, AVDD=1.8V, GND=0V, T PARAMETER Speaker Driver Class D Audio Performance (R SNR (A-weighted) THD (P =500mW) O THD+N (P =500mW) O PSRR DC Offset at Load Efficiency Output Power SPKVDD Leakage Current Quiescent Current ...

Page 10

WM9090 TERMINOLOGY 1. Signal-to-Noise Ratio (dB) – SNR is a measure of the difference in level between the maximum full scale output signal and the output with no input signal applied. 2. Total Harmonic Distortion (dB) – THD is the ...

Page 11

Pre-Production AUDIO SIGNAL PATHS DIAGRAM w WM9090 PP, January 2010, Rev 3.0 11 ...

Page 12

WM9090 CONTROL INTERFACE TIMING START SCLK (input SDA Figure 2 Control Interface Timing Test Conditions SPKVDD = 3.6V, AVDD=1.8V, GND=0V, T PARAMETER SCLK Frequency SCLK Low Pulse-Width SCLK High Pulse-Width Hold Time (Start Condition) Setup Time ...

Page 13

Pre-Production DEVICE DESCRIPTION INTRODUCTION The WM9090 is an ultra-low power, high quality audio subsystem, including a headphone and speaker driver. Its flexible architecture is designed to interface with a wide range of analogue components. The small 2.0 x 2.5mm footprint ...

Page 14

WM9090 INPUT SIGNAL PATH The WM9090 supports two differential analogue input channels, configurable in a number of combinations: The inputs may be mixed together or independently routed to different combinations of output drivers. The WM9090 input signal paths and control ...

Page 15

Pre-Production LINE INPUTS All of the analogue input pins are designed as line inputs. These pins can be configured as single- ended or differential inputs, with flexible routing options and gain controls suitable for many different usage cases. These inputs ...

Page 16

WM9090 INPUT PGA CONFIGURATION The input PGAs can be configured in single-ended mode or differential mode, using the IN1_DIFF and IN2_DIFF register bits described in Table 2. In single-ended mode, an input pin is routed to each individual PGA. In ...

Page 17

Pre-Production REGISTER ADDRESS R25 (19h) IN1 Line Input B Volume R26 (1Ah) IN2 Line Input A Volume w BIT LABEL DEFAULT IN1A_VOL IN1A Volume (differential mode) 2:0 011 [2:0] 000 = -6dB 001 = -3.5dB 010 = 0dB 011 = ...

Page 18

WM9090 REGISTER ADDRESS R27 (1Bh) IN2 Line Input B Volume Table 3 Input PGA Volume Control w BIT LABEL DEFAULT 6 IN2A_ZC 0 IN2A PGA Zero Cross Control 0 = Change gain immediately 1 = Change gain on zero cross ...

Page 19

Pre-Production OUTPUT SIGNAL PATH The WM9090 output mixers provide a high degree of flexibility, allowing configurable operation of multiple signal paths through the device to a variety of analogue outputs. The outputs comprise a ground referenced headphone driver and Class ...

Page 20

WM9090 REGISTER ADDRESS (3) Table 4 Output Signal Paths Enable SPEAKER MIXER CONTROL The signal path configuration registers for the Speaker Mixer are described in Table 5. Each of the input PGAs IN1A, IN1B, IN2A and IN2B is independently selectable ...

Page 21

Pre-Production REGISTER ADDRESS Table 5 Speaker Mixer (SPKMIX) Control SPEAKER OUTPUT VOLUME CONTROL The speaker output PGA controls are shown in Table 6. A zero-cross function is provided on the speaker output PGA. Note that the timeout clock TOCLK must ...

Page 22

WM9090 HEADPHONE MIXER CONTROL The Headphone Mixer configuration registers are described in Table 8 for the Left Channel (MIXOUTL) and Table 9 for the Right Channel (MIXOUTR). A subset of the available input PGAs IN1A, IN1B, IN2A and IN2B is ...

Page 23

Pre-Production REGISTER ADDRESS Table 9 Right Output Mixer (MIXOUTR) Control HEADPHONE OUTPUT VOLUME CONTROL The headphone output PGA controls are shown in Table 10. A zero-cross function is provided on the headphone output PGAs. Note that the timeout clock TOCLK ...

Page 24

WM9090 REGISTER ADDRESS R29 (1Dh) Right Output Volume Table 10 Headphone Output PGA Control PGA GAIN SETTING Table 11 Output PGA Volume Range w BIT LABEL 8 HPOUT1_VU 7 HPOUT1R_ZC 6 HPOUT1R_MUTE 5:0 HPOUT1R_VOL [5:0] VOLUME (dB) PGA GAIN SETTING ...

Page 25

Pre-Production AUTOMATIC GAIN CONTROL (AGC) The Speaker Output PGA incorporates an Automatic Gain Control (AGC) circuit. This feature provides an automatic reduction in the speaker path gain in order to prevent clipping or power overload at the loudspeaker. The AGC ...

Page 26

WM9090 When the AGC applies signal attenuation triggered by the anti-clip threshold, the signal gain is reduced at a rate that is set by the AGC_CLIP_ATK register. When the anti-clip threshold is no longer met (due to the signal level ...

Page 27

Pre-Production AGC POWER LIMITING The second mechanism used by the AGC to monitor signal conditions is the power limit function. The speaker output voltage is measured, and the corresponding power output is determined. The power limiting function can be disabled ...

Page 28

WM9090 REGISTER ADDRESS R99 (63h) AGC Control 1 Table 14 AGC Power Limit Control w BIT LABEL DEFAULT 15 AGC_PWR_ENA 1 AGC_PWR_AVG 12 0 11:8 AGC_PWR_THR [2:0] 0000 6:4 AGC_PWR_ATK [2:0] 000 2:0 AGC_PWR_DCY [2:0] 000 Pre-Production DESCRIPTION Enable AGC ...

Page 29

Pre-Production ANALOGUE OUTPUTS The speaker, headphone and earpiece outputs are highly configurable and may be used in many different ways. SPEAKER OUTPUT CONFIGURATIONS The Class D speaker output is driven by the speaker mixer, SPKMIX. The speaker output operates in ...

Page 30

WM9090 HEADPHONE OUTPUT CONFIGURATIONS The headphone output pins HPOUTL and HPOUTR are driven by the headphone output PGAs. Each PGA has its own dedicated volume control, as described in the “Output Signal Path” section. The inputs to these PGAs come ...

Page 31

Pre-Production CLK_SYS Internal Oscillator OSC_ENA Figure 7 Clocking Scheme REGISTER ADDRESS R1 (01h) Power Management (1) R6 (06h) Clocking 1 R66 (42h) Clocking 4 Table 16 Clocking Control TOCLK_RATE Table 17 TOCLK Rates w f/N f/N f/N TOCLK_ENA f/1024 TOCLK_RATE_DIV16 ...

Page 32

WM9090 CONTROL INTERFACE The WM9090 is controlled by writing to registers through a 2-wire serial control interface. Readback is available for all registers, including Chip ID and power management status. The WM9090 is a slave device on the control interface; ...

Page 33

Pre-Production The sequence of signals associated with a single register write operation is illustrated in Figure 8. Figure 8 Control Interface Register Write The sequence of signals associated with a single register read operation is illustrated in Figure 9. SCLK ...

Page 34

WM9090 Figure 10 Single Register Write to Specified Address Figure 11 Single Register Read from Specified Address Figure 12 Multiple Register Write to Specified Address using Auto-increment Figure 13 Multiple Register Read from Specified Address using Auto-increment Figure 14 Multiple ...

Page 35

Pre-Production CONTROL WRITE SEQUENCER The Control Write Sequencer is a programmable unit that forms part of the WM9090 control interface logic. It provides the ability to perform a sequence of register write operations with the minimum of demands on the ...

Page 36

WM9090 REGISTER ADDRESS R70 (46h) Write Sequencer 0 R73 (49h) Write Sequencer 3 R74 (4Ah) Write Sequencer 4 R75 (4Bh) Write Sequencer 5 Table 19 Write Sequencer Control - Initiating a Sequence PROGRAMMING A SEQUENCE A sequence consists of write ...

Page 37

Pre-Production WSEQ_DATA_WIDTH is a 3-bit field which identifies the width of the data block to be written. This enables selected portions of a Control Register to be updated without any concern for other bits within the same register, eliminating the ...

Page 38

WM9090 Note that a ‘Dummy’ write can be inserted into a control sequence by commanding the sequencer to write a value bit 0 of Register R255 (FFh). This is effectively a write to a non-existent register location. ...

Page 39

Pre-Production The following default control sequences are provided: 1. Headphone Start-Up - This sequence powers up the headphone driver and charge pump. It commands the DC Servo to perform offset correction. This sequence is intended for enabling the headphone output ...

Page 40

WM9090 Generic Shut-Down The Generic Shut-Down sequence can be initiated by writing 0110h to Register 73 (49h). This single operation starts the Control Write Sequencer at Index Address 16 (10h) and executes the sequence defined in Table 22. This sequence ...

Page 41

Pre-Production POWER SEQUENCES AND POP SUPPRESSION CONTROL The WM9090 incorporates a number of features, including Wolfson’s SilentSwitch™ technology, designed to suppress pops normally associated with Start-Up, Shut-Down or signal path control. To achieve maximum benefit from these features, careful attention ...

Page 42

WM9090 Step 1 Step 2 Table 25 Headphone Output Disable Sequence The register bits relating to pop suppression control are defined in Table 26. REGISTER ADDRESS R1 (01h) Power Management (1) R96 (60h) Analogue SEQUENCE HEADPHONE DISABLE ...

Page 43

Pre-Production REGISTER ADDRESS Table 26 Pop Suppression Control w BIT LABEL DEFAULT HPOUT1R_OUTP HPOUT1R_DLY 0 WM9090 DESCRIPTION Enables HPOUT1R output stage 0 = Disabled 1 = Enabled For pop-free operation, this bit should be set to 1 ...

Page 44

WM9090 CHARGE PUMP The WM9090 incorporates a dual-mode Charge Pump which generates the supply rails for the headphone output drivers, HPOUT1L and HPOUT1R. The Charge Pump has a single supply input, AVDD, and generates split rails CPVOUTP and CPVOUTN according ...

Page 45

Pre-Production DC SERVO The WM9090 provides a DC servo circuit on the headphone outputs HPOUTL and HPOUTR in order to remove DC offset from these ground-referenced outputs. When enabled, the DC servo ensures that the DC level of these outputs ...

Page 46

WM9090 REGISTER ADDRESS R84 (54h) DC Servo 0 R87 (57h) DC Servo 3 R88 (58h) DC Servo Readback 0 w BIT LABEL DEFAULT 5 DCS_TRIG_START 0 UP_1 4 DCS_TRIG_START 0 UP_0 DCS_TRIG_DAC_W 3 0 R_1 2 DCS_TRIG_DAC_W 0 R_0 1 ...

Page 47

Pre-Production REGISTER ADDRESS Table 28 DC Servo Enable and Start-Up Modes DC SERVO ACTIVE MODES The DC Servo modes described above are suitable for initialising the DC offset correction circuit on the Headphone outputs as part of a controlled start-up ...

Page 48

WM9090 REGISTER ADDRESS R85 (55h) DC Servo 1 Table 29 DC Servo Active Modes DC SERVO READBACK The current DC offset value for each Headphone output channel can be read from Registers R89 and R90, as described in Table 30. ...

Page 49

Pre-Production REFERENCE VOLTAGES AND MASTER BIAS This section describes the analogue reference voltage and bias current controls. It also describes the VMID soft-start circuit for pop suppressed start-up and shut-down. The analogue circuits in the WM9090 require a mid-rail analogue ...

Page 50

WM9090 POWER MANAGEMENT The WM9090 provides control registers that allow users to select which functions are active. For minimum power consumption, unused functions should be disabled. To minimise pop or click noise important to enable or disable functions ...

Page 51

Pre-Production REGISTER ADDRESS R3 (03h) Power Management (3) R57 (39h) AntiPOP2 R70 (46h) Write Sequencer 0 R76 (4Ch) Charge Pump 1 R84 (54h) DC Servo 0 Table 32 Power Management w BIT LABEL DEFAULT IN2B_ENA SPKLVOL_ENA 0 ...

Page 52

WM9090 THERMAL SHUTDOWN The WM9090 incorporates a temperature sensor which detects when the device temperature is within normal limits or if the device is approaching a hazardous temperature condition. The temperature status can be polled at any time by reading ...

Page 53

Pre-Production REGISTER MAP w WM9090 PP, January 2010, Rev 3.0 53 ...

Page 54

WM9090 w Pre-Production PP, January 2010, Rev 3.0 54 ...

Page 55

Pre-Production REGISTER BITS BY ADDRESS REGISTER BIT LABEL ADDRESS R0 (00h) 15:0 SW_RESET Software [15:0] Reset Register 00h Software Reset REGISTER BIT LABEL ADDRESS R1 (01h) 12 SPKOUTL_EN Power A Managemen t (1) 9 HPOUT1L_EN A 8 HPOUT1R_EN A 3 ...

Page 56

WM9090 REGISTER BIT LABEL ADDRESS 6 IN1B_ENA 5 IN2A_ENA 4 IN2B_ENA Register 02h Power Management (2) REGISTER BIT LABEL ADDRESS R3 (03h) 14 AGC_ENA Power Managemen t (3) 8 SPKLVOL_EN A 5 MIXOUTL_EN A 4 MIXOUTR_EN A 3 SPKMIX_ENA Register ...

Page 57

Pre-Production REGISTER BIT LABEL ADDRESS R22 (16h) 1 IN1_DIFF IN1 Line Control 0 IN1_CLAMP Register 16h IN1 Line Control REGISTER BIT LABEL ADDRESS R23 (17h) 1 IN2_DIFF IN2 Line Control 0 IN2_CLAMP Register 17h IN2 Line Control REGISTER BIT LABEL ...

Page 58

WM9090 REGISTER BIT LABEL ADDRESS R25 (19h) 8 IN1_VU IN1 Line Input B Volume 7 IN1B_MUTE 6 IN1B_ZC 2:0 IN1B_VOL [2:0] Register 19h IN1 Line Input B Volume REGISTER BIT LABEL ADDRESS R26 (1Ah) 8 IN2_VU IN2 Line Input A ...

Page 59

Pre-Production REGISTER BIT LABEL ADDRESS Register 1Ah IN2 Line Input A Volume REGISTER BIT LABEL ADDRESS R27 (1Bh) 8 IN2_VU IN2 Line Input B Volume 7 IN2B_MUTE 6 IN2B_ZC 2:0 IN2B_VOL [2:0] Register 1Bh IN2 Line Input B Volume REGISTER ...

Page 60

WM9090 REGISTER BIT LABEL ADDRESS 5:0 HPOUT1L_VO L [5:0] Register 1Ch Left Output Volume REGISTER BIT LABEL ADDRESS R29 (1Dh) 8 HPOUT1_VU Right Output Volume 7 HPOUT1R_ZC 6 HPOUT1R_MU TE 5:0 HPOUT1R_VO L [5:0] Register 1Dh Right Output Volume REGISTER ...

Page 61

Pre-Production REGISTER BIT LABEL ADDRESS R36 (24h) 4 SPKMIXL_TO_ SPKOUT SPKOUTL Mixers Register 24h SPKOUT Mixers REGISTER BIT LABEL ADDRESS R37 (25h) 5:3 SPKOUTL_BO ClassD3 OST [2:0] Register 25h ClassD3 REGISTER BIT LABEL ADDRESS R38 (26h) 8 SPKOUT_VU Speaker Volume ...

Page 62

WM9090 REGISTER BIT LABEL ADDRESS R46 (2Eh) 6 IN1A_TO_MIX Output OUTR Mixer2 4 IN1B_TO_MIX OUTR 2 IN2A_TO_MIX OUTR 0 IN2B_TO_MIX OUTR Register 2Eh Output Mixer2 REGISTER BIT LABEL ADDRESS R47 (2Fh) 8 MIXOUTL_MU Output TE Mixer3 7:6 IN1A_MIXOUT L_VOL [1:0] ...

Page 63

Pre-Production REGISTER BIT LABEL ADDRESS R_VOL [1:0] Register 30h Output Mixer4 REGISTER BIT LABEL ADDRESS R54 (36h) 6 IN1A_TO_SPK Speaker MIX Mixer 4 IN1B_TO_SPK MIX 2 IN2A_TO_SPK MIX 0 IN2B_TO_SPK MIX Register 36h Speaker Mixer REGISTER BIT LABEL ADDRESS R57 ...

Page 64

WM9090 REGISTER BIT LABEL ADDRESS R71 (47h) 14:12 WSEQ_DATA_ Write WIDTH [2:0] Sequencer 1 11:8 WSEQ_DATA_ START [3:0] 7:0 WSEQ_ADDR [7:0] Register 47h Write Sequencer 1 REGISTER BIT LABEL ADDRESS R72 (48h) 14 WSEQ_EOS Write Sequencer 2 11:8 WSEQ_DELAY [3:0] ...

Page 65

Pre-Production REGISTER BIT LABEL ADDRESS R74 (4Ah) 0 WSEQ_BUSY Write Sequencer 4 Register 4Ah Write Sequencer 4 REGISTER BIT LABEL ADDRESS R75 (4Bh) 5:0 WSEQ_CURR Write ENT_INDEX Sequencer 5 [5:0] Register 4Bh Write Sequencer 5 REGISTER BIT LABEL ADDRESS R76 ...

Page 66

WM9090 REGISTER BIT LABEL ADDRESS 1 DCS_ENA_CH AN_1 0 DCS_ENA_CH AN_0 Register 54h DC Servo 0 REGISTER BIT LABEL ADDRESS R85 (55h) 11:5 DCS_SERIES_ DC Servo 1 NO_01 [6:0] 3:0 DCS_TIMER_P ERIOD_01 [3:0] Register 55h DC Servo 1 REGISTER BIT ...

Page 67

Pre-Production REGISTER BIT LABEL ADDRESS R_COMPLETE [1:0] 1:0 DCS_STARTU P_COMPLETE [1:0] Register 58h DC Servo Readback 0 REGISTER BIT LABEL ADDRESS R89 (59h) 7:0 DCS_DAC_W DC Servo R_VAL_1_RD Readback 1 [7:0] Register 59h DC Servo Readback 1 REGISTER BIT LABEL ...

Page 68

WM9090 REGISTER BIT LABEL ADDRESS 3 HPOUT1R_RM V_SHORT 2 HPOUT1R_OU TP 1 HPOUT1R_DL Y Register 60h Analogue HP 0 REGISTER BIT LABEL ADDRESS R98 (62h) 15 AGC_CLIP_EN A AGC Control 0 11:8 AGC_CLIP_TH R [3:0] 6:4 AGC_CLIP_AT K [2:0] w ...

Page 69

Pre-Production REGISTER BIT LABEL ADDRESS 2:0 AGC_CLIP_DC Y [2:0] Register 62h AGC Control 0 REGISTER BIT LABEL ADDRESS R99 (63h) 15 AGC_PWR_E NA AGC Control 1 12 AGC_PWR_AV G 11:8 AGC_PWR_TH R [2:0] 6:4 AGC_PWR_AT K [2:0] 2:0 AGC_PWR_D CY ...

Page 70

WM9090 REGISTER BIT LABEL ADDRESS Register 63h AGC Control 1 REGISTER BIT LABEL ADDRESS R100 (64h) 8 AGC_RAMP AGC Control 2 5:0 AGC_MINGAIN [5:0] Register 64h AGC Control 2 w DEFAULT DESCRIPTION power limiting 000 = 1080ms/6dB 001 = 1200ms/6dB ...

Page 71

Pre-Production APPLICATIONS INFORMATION RECOMMENDED EXTERNAL COMPONENTS Figure 17 below provides a summary of recommended external components for WM9090. Note that the diagram does not include any components that are specific to the end application e.g. they do not include filtering ...

Page 72

WM9090 AUDIO INPUT PATHS The WM9090 provides 4 analogue audio inputs. Each of these inputs is referenced to the internal DC reference, VMID blocking capacitor is required for each input pin used in the target application. The choice ...

Page 73

Pre-Production POWER SUPPLY DECOUPLING Electrical coupling exists particularly in digital logic systems where switching in one sub-system causes fluctuations on the power supply. This effect occurs because the inductance of the power supply acts in opposition to the changes in ...

Page 74

WM9090 CLASS D SPEAKER CONNECTIONS The WM9090 incorporates a Class D speaker driver. As the Class D output is a pulse width modulated (PWM) signal, the choice of speakers and tracking of signals is critical for ensuring good performance and ...

Page 75

Pre-Production A simple equivalent circuit of a loudspeaker consists of a serially connected resistor and inductor, as shown in Figure 21. This circuit provides a low pass filter for the speaker output. If the loudspeaker characteristics are suitable, then the ...

Page 76

WM9090 PCB LAYOUT CONSIDERATIONS Poor PCB layout will degrade the performance and be a contributory factor in EMI, ground bounce and resistive voltage losses. All external components should be placed as close to the WM9090 device as possible, with current ...

Page 77

Pre-Production PACKAGE DIMENSIONS B: 20 BALL W-CSP PACKAGE 2.530 DETAIL 2 e BOTTOM VIEW bbb Dimensions (mm) Symbols MIN NOM A 0.615 0.700 0.219 0.244 A1 ...

Page 78

... WM9090 IMPORTANT NOTICE Wolfson Microelectronics plc (“Wolfson”) products and services are sold subject to Wolfson’s terms and conditions of sale, delivery and payment supplied at the time of order acknowledgement. Wolfson warrants performance of its products to the specifications in effect at the date of shipment. Wolfson reserves the right to make changes to its products and specifications or to discontinue any product or service without notice ...