A3PN030-ZQNG68 Actel, A3PN030-ZQNG68 Datasheet - Page 58

A3PN030-ZQNG68

Manufacturer Part Number

A3PN030-ZQNG68

Description

FPGA - Field Programmable Gate Array 30K System Gates ProASIC3 nano

Manufacturer

Actel

Datasheet

1.A3PN030-ZVQG100.pdf

(106 pages)

Specifications of A3PN030-ZQNG68

Processor Series

A3PN030

Core

IP Core

Number Of Macrocells

256

Maximum Operating Frequency

350 MHz

Number Of Programmable I/os

49

Supply Voltage (max)

3.3 V

Supply Current

2 mA

Maximum Operating Temperature

+ 70 C

Minimum Operating Temperature

- 20 C

Development Tools By Supplier

AGLN-Nano-Kit, AGLN-Z-Nano-Kit, Silicon-Explorer II, Silicon-Sculptor 3, SI-EX-TCA, FloasPro 4, FlashPro 3, FlashPro Lite

Mounting Style

SMD/SMT

Supply Voltage (min)

1.5 V

Number Of Gates

30 K

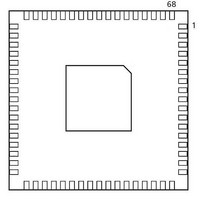

Package / Case

QFN-68

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

A3PN030-ZQNG68I

Manufacturer:

ACT

Quantity:

5

ProASIC3 nano DC and Switching Characteristics

Figure 2-14 • Output Enable Register Timing Diagram

Table 2-60 • Output Enable Register Propagation Delays

2- 44

Parameter

t

t

t

t

t

t

t

t

t

t

t

t

t

Note:

D_Enable

Enable

Preset

EOUT

OECLKQ

OESUD

OEHD

OECLR2Q

OEPRE2Q

OEREMCLR

OERECCLR

OEREMPRE

OERECPRE

OEWCLR

OEWPRE

OECKMPWH

OECKMPWL

CLK

Clear

For specific junction temperature and voltage supply levels, refer to

Commercial-Case Conditions: T

Clock-to-Q of the Output Enable Register

Data Setup Time for the Output Enable Register

Data Hold Time for the Output Enable Register

Asynchronous Clear-to-Q of the Output Enable Register

Asynchronous Preset-to-Q of the Output Enable Register

Asynchronous Clear Removal Time for the Output Enable Register

Asynchronous Clear Recovery Time for the Output Enable Register

Asynchronous Preset Removal Time for the Output Enable Register

Asynchronous Preset Recovery Time for the Output Enable Register

Asynchronous Clear Minimum Pulse Width for the Output Enable Register

Asynchronous Preset Minimum Pulse Width for the Output Enable Register

Clock Minimum Pulse Width HIGH for the Output Enable Register

Clock Minimum Pulse Width LOW for the Output Enable Register

Output Enable Register

Timing Characteristics

50%

50%

t

OESUE

1

t

OEHE

50%

t

OESUD

50%

t

OECLKQ

0

t

50%

OEHD

50%

50%

J

Description

t

= 70°C, Worst-Case VCC = 1.425 V

OEWPRE

t

OEPRE2Q

50%

50%

t

50%

OERECPRE

R e visio n 8

50%

t

t

OEWCLR

OECLR2Q

50%

50%

Table 2-6 on page 2-5

t

50%

OERECCLR

50%

t

OECKMPWH

t

OEREMPRE

0.44 0.51 0.59

0.31 0.36 0.42

0.00 0.00 0.00

0.67 0.76 0.89

0.67 0.76 0.89

0.00 0.00 0.00

0.22 0.25 0.30

0.00 0.00 0.00

0.22 0.25 0.30

0.22 0.25 0.30

0.22 0.25 0.30

0.36 0.41 0.48

0.32 0.37 0.43

50%

–2

for derating values.

50%

t

OECKMPWL

–1

Std. Units

t

OEREMCLR

50%

50%

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns

ns