KSZ8842-16MBL Micrel Inc, KSZ8842-16MBL Datasheet

KSZ8842-16MBL

Specifications of KSZ8842-16MBL

Available stocks

Related parts for KSZ8842-16MBL

KSZ8842-16MBL Summary of contents

Page 1

... KSZ8842, the KSZ8842MVLI, can be ordered Information). The KSZ8842M can be configured as a switch low-latency (≤ 310 nanoseconds) repeater in latency- critical, embedded or industrial Ethernet applications. For industrial applications, the KSZ8842M can run in half-duplex mode regardless of the application. Functional Diagram ...

Page 2

... Information). Additional Features In addition to offering all of the features of an integrated Layer-2 managed switch, the KSZ8842M offers: • Repeater mode capabilities to allow for cut through in latency critical industrial Ethernet or embedded Ethernet applications • Dynamic buffer memory scheme – ...

Page 3

... Added QMU RX Flow Control High Watermark QRFCR register and updated body text Improve the ARDY low time in read cycle and in write cycle during QMU data register access Updated ordering information and thermal data Add 100 ohm resistor between 1.2V and 3.3V in Appendix Add KSZ8842-16MBL 100-Ball BGA package information 3 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 4

... Ball Configuration for KSZ8842-16 Switches (8/16-Bit) ..................................................................................... 12 Pin Description for KSZ8842-16 Switches (8/16-Bit) .......................................................................................... 13 Ball Description for KSZ8842-16 Switches (8/16-Bit) ......................................................................................... 18 Pin Configuration for KSZ8842-32 Switches (32-Bit).......................................................................................... 22 Pin Description for KSZ8842-32 Switches (32-Bit) ............................................................................................. 23 Functional Description .......................................................................................................................................... 28 Functional Overview: Physical Layer Transceiver ............................................................................................. 28 100BASE-TX Transmit ..........................................................................................................................................................28 100BASE-TX Receive ...........................................................................................................................................................28 Scrambler/De-scrambler (100BASE-TX only) ...

Page 5

... Bank 18 Interrupt Status Register (0x02): ISR.......................................................................................................................70 Bank 18 Receive Status Register (0x04): RXSR ...................................................................................................................71 Bank 18 Receive Byte Counter Register (0x06): RXBC ........................................................................................................72 Bank 19 Multicast Table Register 0 (0x00): MTR0 ................................................................................................................72 Bank 19 Multicast Table Register 1 (0x02): MTR1 ................................................................................................................72 Bank 19 Multicast Table Register 2 (0x04): MTR2 ................................................................................................................72 October 2007 KSZ8842-16/32 MQL/MVL/MVLI/MBL 5 M9999-102207-1.9 ...

Page 6

... Bank 47 PHY1 LinkMD Control/Status (0x00): P1VCT..........................................................................................................96 Bank 47 PHY1 Special Control/Status Register (0x02): P1PHYCTRL ..................................................................................97 Bank 47 PHY2 LinkMD Control/Status (0x04): P2VCT..........................................................................................................97 Bank 47 PHY2 Special Control/Status Register (0x06): P2PHYCTRL ..................................................................................98 Bank 48 Port 1 Control Register 1 (0x00): P1CR1 ................................................................................................................99 Bank 48 Port 1 Control Register 2 (0x02): P1CR2 ..............................................................................................................100 October 2007 KSZ8842-16/32 MQL/MVL/MVLI/MBL 6 M9999-102207-1.9 ...

Page 7

... Timing Specifications .......................................................................................................................................... 124 Asynchronous Timing without using Address Strobe (ADSN = 0) .......................................................................................124 Asynchronous Timing using Address Strobe (ADSN)..........................................................................................................125 Asynchronous Timing using DATACSN (KSZ8842-32MQL/MVL device only) ....................................................................126 Address Latching Timing for All Modes ...............................................................................................................................127 Synchronous Timing in Burst Write (VLBUSN = 1)..............................................................................................................128 Synchronous Timing in Burst Read (VLBUSN = 1)..............................................................................................................129 Synchronous Write Timing (VLBUSN = 0) ...

Page 8

... Micrel, Inc. Appendix .............................................................................................................................................................. 141 October 2007 KSZ8842-16/32 MQL/MVL/MVLI/MBL 8 M9999-102207-1.9 ...

Page 9

... Figure 2. Standard – KSZ8842-16 MQL 128-Pin PQFP (Top View)............................................................................................ 11 Figure 3. Option – KSZ8842-16 MVL 128-Pin LQFP (Top View) ................................................................................................ 11 Figure 4. KSZ8842-16MBL 100-Ball LFBGA (Top View)............................................................................................................. 12 Figure 5. Standard – KSZ8842-32 MQL 128-Pin PQFP (Top View)............................................................................................ 22 Figure 6. Option – KSZ8842-32 MVL 128-Pin LQFP (Top View) ................................................................................................ 22 Figure 7 ...

Page 10

... Table 31. Synchronous Read (VLBUSN = 0) Timing Parameters ............................................................................................. 131 Table 32. EEPROM Timing Parameters.................................................................................................................................... 132 Table 33. Auto Negotiation Timing Parameters......................................................................................................................... 133 Table 34. Reset Timing Parameters.......................................................................................................................................... 134 Table 35. Transformer Selection Criteria................................................................................................................................... 135 Table 36. Qualified Single Port Magnetic .................................................................................................................................. 135 Table 37. Typical Reference Crystal Characteristics................................................................................................................. 135 October 2007 KSZ8842-16/32 MQL/MVL/MVLI/MBL 10 M9999-102207-1.9 ...

Page 11

... DIO N C D15 D14 D13 D12 D11 D10 DIO Figure 3. Option – KSZ8842-16 MVL 128-Pin LQFP (Top View) October 2007 iew ) 100 101 102 103 104 105 106 K SZ8842-16 107 108 109 110 111 112 M VL 113 114 115 116 117 ...

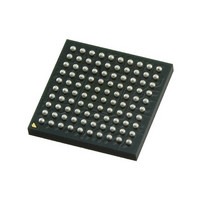

Page 12

... Micrel, Inc. Ball Configuration for KSZ8842-16 Switches (8/16-Bit) October 2007 Figure 4. KSZ8842-16MBL 100-Ball LFBGA (Top View) 12 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 13

... Micrel, Inc. Pin Description for KSZ8842-16 Switches (8/16-Bit) Pin Number Pin Name Type 1 TEST_EN 2 SCAN_EN 3 P1LED2 Opu 4 P1LED1 Opu 5 P1LED0 Opu 6 P2LED2 Opu 7 P2LED1 Opu 8 P2LED0 Opu 9 DGND Gnd 10 VDDIO 11 RDYRTNN Ipd October 2007 Pin Function I Test Enable For normal operation, pull-down this pin to ground. ...

Page 14

... For VLBus-like mode, the falling edge of this signal indicates ready. This signal is synchronous to the bus clock signal BCLK. For burst mode (32-bit interface only), the KSZ8842M drives this pin low to signal wait states. Interrupt Active Low signal to host CPU to indicate an interrupt status bit is set, this pin need an external 4 ...

Page 15

... Port 1 physical transmit (MDI) or receive (MDIX) signal (– differential) 3.3V analog V input power supply with well decoupling capacitors. DD 3.3V analog V input power supply with well decoupling capacitors. DD Port 2 physical receive (MDI) or transmit (MDIX) signal (- differential) Port 2 physical receive (MDI)or transmit (MDIX) signal (+ differential) Analog ground 15 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 16

... Byte Enable 0 Not, Active low for Data byte 0 enable (there is an internal inverter enabled and connected to the BE1N for 8-bit bus mode). No Connect Digital core ground 1.2V digital core V input power supply from VDDCO (pin24) through external DD Ferrite bead and capacitor. 16 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 17

... IO with well decoupling capacitors. DDIO No Connect Data 15 Data 14 Data 13 Data 12 Data 11 Data 10 Data 9 Data 8 Data 7 Data 6 Data 5 Data 4 Data 3 Digital IO ground Digital core ground 3.3V digital V input power supply for IO with well decoupling capacitors. DDIO Data 2 Data 1 Data 0 17 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 18

... Micrel, Inc. Ball Description for KSZ8842-16 Switches (8/16-Bit) Ball Number Ball Name Type E8 TEST_EN D10 SCAN_EN A10 P1LED2 Opu B10 P1LED1 Opu C10 P1LED0 Opu A9 P2LED2 Opu B9 P2LED1 Opu C9 P2LED0 Opu D9 RDYRTNN Ipd A8 BCLK Ipd October 2007 Ball Function I Test Enable For normal operation, pull-down this ball to ground ...

Page 19

... For VLBus-like mode, the falling edge of this signal indicates ready. This signal is synchronous to the bus clock signal BCLK. For burst mode (32-bit interface only), the KSZ8842M drives this ball low to signal wait states. Interrupt Active Low signal to host CPU to indicate an interrupt status bit is set, this ball need an external 4 ...

Page 20

... Note: Clock requirement is ± 50ppm for either crystal or oscillator. Hardware reset ball (active Low). This reset input is required minimum of 10ms low after stable supply voltage 3.3V. Address 15 Address 14 Address 13 Address 12 Address 11 Address 10 Address 9 Address 8 Address 7 Address 6 Address 5 Address 4 Address 3 Address 2 20 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 21

... Ferrite bead and capacitor. 3.3V analog V input power supply with well decoupling capacitors. DD 3.3V analog V input power supply with well decoupling capacitors. DD 3.3V digital V input power supply for IO with well decoupling capacitors. DDIO All digital and analog grounds No Connect 21 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 22

... Figure 5. Standard – KSZ8842-32 MQL 128-Pin PQFP (Top View) D26 D25 D24 D23 D22 D21 D 20 D19 D18 D17 DGND VDDIO D16 D15 D14 D13 D12 D11 D10 VDDIO Figure 6. Option – KSZ8842-32 MVL 128-Pin LQFP (Top View) October 2007 8842-32 ...

Page 23

... Micrel, Inc. Pin Description for KSZ8842-32 Switches (32-Bit) Pin Number Pin Name Type 1 TEST_EN 2 SCAN_EN 3 P1LED2 Opu 4 P1LED1 Opu 5 P1LED0 Opu 6 P2LED2 Opu 7 P2LED1 Opu 8 P2LED0 Opu 9 DGND Gnd 10 VDDIO 11 RDYRTNN Ipd October 2007 Pin Function I Test Enable For normal operation, pull-down this pin to ground. ...

Page 24

... For VLBus-like mode, the falling edge of this signal indicates ready. This signal is synchronous to the bus clock signal BCLK. For burst mode (32-bit interface only), the KSZ8842M drives this pin low to signal wait states. Interrupt Active Low signal to host CPU to indicate an interrupt status bit is set, this pin need an external 4 ...

Page 25

... Port 1 physical transmit (MDI) or receive (MDIX) signal (+ differential) Port 1 physical transmit (MDI) or receive (MDIX) signal (– differential) 3.3V analog V input power supply with well decoupling capacitors. DD 3.3V analog V DD Port 2 physical receive (MDI) or transmit (MDIX) signal (- differential) Port 2 physical receive (MDI) or transmit (MDIX) signal (+ differential) 25 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 26

... Byte Enable 2 Not, Active low for Data byte 2 enable. Byte Enable 1 Not, Active low for Data byte 1 enable. Byte Enable 0 Not, Active low for Data byte 0 enable. Data 31 Digital core ground 1.2V digital core V input power supply from VDDCO (pin24) through external DD Ferrite bead and capacitor. 26 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 27

... Data 7 Data 6 Data 5 Data 4 Data 3 Digital IO ground Digital core ground 3.3V digital V input power supply for IO with well decoupling capacitors. DDIO Data 2 Data 1 Data 0 Gnd = Ground Input O = Output. Ipu = Input with internal pull-up. Opu = Output with internal pull-up. 27 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 28

... The KSZ8842M contains two 10/100 physical layer transceivers (PHYs), two MAC units, and a DMA channel integrated with a Layer-2 switch. The KSZ8842M contains a bus interface unit (BIU), which controls the KSZ8842M via an 8, 16, or 32-bit host interface. Physical signal transmission and reception are enhanced through the use of analog circuits in the PHY that make the design more efficient and allow for low power consumption ...

Page 29

... Micrel, Inc. Power Management The KSZ8842M features per port power-down mode. To save power, the user can power-down the port that is not in use by setting bit 11 in either P1CR4 or P1MBCR register for port 1 and setting bit 11 in either P2CR4 or P2MBCR register for port 2. To bring the port back up, reset bit 11 in these registers. ...

Page 30

... If auto negotiation is not supported or the link partner to the KSZ8842M is forced to bypass auto negotiation, the mode is set by observing the signal at the receiver. This is known as parallel mode because while the transmitter is sending auto negotiation advertisements, the receiver is listening for advertisements or a fixed signal protocol ...

Page 31

... Set Link Mode LinkMD Cable Diagnostics The KSZ8842M LinkMD uses time domain reflectometry (TDR) to analyze the cabling plant for common cabling problems such as open circuits, short circuits, and impedance mismatches. LinkMD works by sending a pulse of known amplitude and duration down the MDI and MDI-X pairs and then analyzes the shape of the reflected signal. Timing the pulse duration gives an indication of the distance to the cabling fault with a maximum distance of 200m and an accuracy of +/– ...

Page 32

... If P1VCT[14:13]=11 or P2VCT[14:13]=11, this indicates an invalid test, and occurs when the KSZ8842M is unable to shut down the link partner. In this instance, the test is not run not possible for the KSZ8842M to determine if the detected signal is a reflection of the signal generated or a signal from another source. ...

Page 33

... Micrel, Inc. Forwarding The KSZ8842M forwards packets using the algorithm that is depicted in the following flowcharts. Figure 10 shows stage one of the forwarding algorithm where the search engine looks up the VLAN ID, static table, and dynamic table for the destination address, and comes up with “port to forward 1” (PTF1). PTF1 is then further modified by spanning tree, IGMP snooping, port mirroring, and port VLAN processes to come up with “ ...

Page 34

... These include framing errors, Frame Check Sequence (FCS) errors, alignment errors, and illegal size packet errors. 2. 802.3x pause frames. The KSZ8842M intercepts these packets and performs the flow control. 3. "Local" packets. Based on destination address (DA) lookup. If the destination port from the lookup table matches the port from which the packet originated, the packet is defined as " ...

Page 35

... KSZ8842M issues a flow control frame (Xoff), containing the maximum pause time defined in IEEE standard 802.3x. Once the resource is freed up, the KSZ8842M sends out the other flow control frame (Xon) with zero pause time to turn off the flow control (turn on transmission to the port). A hysteresis feature is provided to prevent the flow control mechanism from being constantly activated and deactivated ...

Page 36

... In terms of physical data bus size, the KSZ8842M supports 8, 16, and 32 bit host/industrial standard data bus sizes. Given a physical data bus size, the KSZ8842M supports 8, 16, or 32-bit data transfers depending on the size of the October 2007 ...

Page 37

... Micrel, Inc. physical data bus. For example, for a 32-bit system/host data bus, it allows 8, 16, and 32-bit data transfers (KSZ8842- 32MQL); for a 16-bit system/host data bus, it allows 8 and 16-bit data transfers (KSZ8842-16MQL); and for 8-bit system/host data bus, it only allows 8-bit data transfers (KSZ8842-16MQL). ...

Page 38

... EISA-like bus (non-burst) interface as shown in the Figure 18. This type of interface requires ADSN to latch the address on the rising edge. The BIU decodes latched A[15:4] and qualifies with AEN to determine if the KSZ8842M switch is the intended target. The data transfer is the same as the first case. ...

Page 39

... The M/nIO signal connection in VLBus is routed to AEN. The CYCLEN in this application is used to sample the SWR signal when it is asserted. Usually, CYCLEN is one clock delay of ADSN. There is a handshaking process to end the cycle of VLBus-like transfers. When the KSZ8842M is ready to finish the cycle ...

Page 40

... Micrel, Inc. ISA Non-burst EISA Burst VLBus Figure 12. Mapping from ISA-like, EISA-like, and VLBus-like transactions to the KSZ8842M Bus KSZ8842-16 HA[1] A[1] HA[15:2] A[15:2] HD[7:0] D[7:0] D[15:8] HA[0] BE0N BE1N VDD 8-bit Data Bus Figure 13. KSZ8842M 8-Bit, 16-Bit, and 32-Bit Data Bus Connections ...

Page 41

... Micrel, Inc. BIU Implementation Principles Since the KSZ8842M is an I/O device with 16 addressable locations, address decoding is based on the values of A15-A4 and AEN. Whenever DATACSN is asserted, the address decoder is disabled and a 32-bit transfer to Data Register is assumed (BE3N – BE0N are ignored). If address latching is required, the address is latched on the rising edge of ADSN and is transparent when ADSN=0. ...

Page 42

... On transmit, all bytes are provided by the CPU, including the source address. The KSZ8842M does not insert its own source address. The 802.3 Frame Length word (Frame Type in Ethernet) is not interpreted by the KSZ8842M treated transparently as data for transmit operations. ...

Page 43

... Table 8 gives the format of the RX byte count field. Bit Description 15-11 Reserved 10-0 RXBC Receive Byte Count Receive Byte Count. October 2007 Table 7. FRXQ Packet Receive Status Table 8. FRXQ RX Byte Count Field 43 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 44

... BPDU packets). The “overriding” bit is set so that the switch forwards those specific packets to the processor. The processor can send packets to the port(s) in this state. Address learning is enabled on the port in this state. Table 9. Spanning Tree States 44 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 45

... The KSZ8842M supports 16 active VLANs out of the 4096 possible VLANs specified in the IEEE 802.1Q specification. KSZ8842M provides a 16-entry VLAN table, which converts the 12-bits VLAN ID (VID) to the 4-bits Filter ID (FID) for address lookup non-tagged or null-VID-tagged packet is received, the ingress port default VID is used for lookup. In VLAN mode, the lookup process starts with VLAN table lookup to determine whether the VID is valid ...

Page 46

... Yes QoS Priority Support The KSZ8842M provides Quality of Service (QoS) for applications such as VoIP and video conferencing. Offering four priority queues per port, the per-port transmit queue can be split into four priority queues: Queue 3 is the highest priority queue and Queue 0 is the lowest priority queue. Bit 0 of registers P1CR1, P2CR1, and P3CR1 is used to enable split transmit queues for ports 1, 2, and the host port, respectively ...

Page 47

... DSCP register to determine priority. Rate Limiting Support The KSZ8842M supports hardware rate limiting from 64 Kbps to 88 Mbps, independently on the “receive side” and on the “transmit side” per port basis. For 10-base T, a rate setting above 10 Mbps means the rate is not limited. On the receive side, the data receive rate for each priority at each port can be limited by setting up Ingress Rate Control Registers ...

Page 48

... The KSZ8842M operates only as a managed switch. EEPROM Interface It is optional in the KSZ8842M to use an external EEPROM. In the case that an EEPROM is not used, the EEEN pin must be tied Low or floating. The external serial EEPROM with a standard microwire bus interface is used for non-volatile storage of information such as the host MAC address, base address, and default configuration settings ...

Page 49

... Figure 15. Near-end (Remote) Loopback Near-end (Remote) loopback is conducted at either PHY port 1 or PHY port 2 of the KSZ8842M. The loopback path starts at the PHY port’s receive inputs (RXPx/RXMx), wraps around at the same PHY port’s PMD/PMA, and ends at the PHY port’ ...

Page 50

... Micrel, Inc Figure 16. Port 1 and port 2 Near-End (Remote) Loopback Path October 2007 Figure 15. Port 2 Far-End Loopback Path / KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 51

... Micrel, Inc. CPU Interface I/O Registers The KSZ8842M provides an EISA-like, ISA-like, or VLBUS-like bus interface for the CPU to access its internal I/O registers. I/O registers serve as the address that the microprocessor uses when communicating with the device. This is used for configuring operational settings, reading or writing control, status information, and transferring packets by reading and writing through the packet data registers ...

Page 52

... Address High Info [15:8] [15:8] Global Reset [7:0] Reserved Reserved Global Reset [15:8] Bus Configuration [7:0] Reserved Reserved Bus Configuration [15:8] Reserved Reserved Bank Select [7:0] Bank Select [15:8] 52 KSZ8842-16/32 MQL/MVL/MVLI/MBL Bank 4 Bank 5 Bank 6 Reserved Reserved Reserved Reserved Reserved M9999-102207-1.9 Bank 7 ...

Page 53

... To 0xF 0xE 0xE - 0xF 0xF October 2007 Bank Location Bank 9 Bank 10 Bank 11 Reserved Reserved Reserved Reserved Reserved Reserved Reserved Bank Select [7:0] Bank Select [15:8] 53 KSZ8842-16/32 MQL/MVL/MVLI/MBL Bank 12 Bank 13 Bank 14 M9999-102207-1.9 Bank 15 ...

Page 54

... QMU Data Low [7:0] Reserved Reserved QMU Data Low [15:8] QMU Data High [7:0] QMU Data High [15:8] Reserved Bank Select [7:0] Bank Select [15:8] 54 KSZ8842-16/32 MQL/MVL/MVLI/MBL Bank 20 Bank 21 Bank 22 Reserved Reserved Reserved Reserved Reserved Reserved M9999-102207-1.9 Bank 23 ...

Page 55

... To 0xF 0xE 0xE - 0xF 0xF October 2007 Bank Location Bank 25 Bank 26 Bank 27 Reserved Reserved Reserved Reserved Reserved Reserved Reserved Bank Select [7:0] Bank Select [15:8] 55 KSZ8842-16/32 MQL/MVL/MVLI/MBL Bank 28 Bank 29 Bank 30 M9999-102207-1.9 Bank 31 ...

Page 56

... Switch Global Control 6 [7:0] Switch Global Control 6 [15:8] Switch Global Control 7 [7:0] Switch Global Control 7 [15:8] Reserved Reserved Bank Select [7:0] Bank Select [15:8] 56 KSZ8842-16/32 MQL/MVL/MVLI/MBL Bank 36 Bank 37 Bank 38 Reserved Reserved Reserved Reserved Reserved M9999-102207-1.9 Bank 39 MAC Address 1 [7:0] MAC Address 1 [15:8] ...

Page 57

... Access Data 4 [15:8] Indirect Access Data 5 [7:0] Reserved Reserved Indirect Access Data 5 [15:8] Reserved Bank Select [7:0] Bank Select [15:8] 57 KSZ8842-16/32 MQL/MVL/MVLI/MBL Bank 44 Bank 45 Bank 46 Digital Test PHY1 MII- PHY2 MII- Status Register Register Basic Control Basic Control [7:0] [7:0] [7:0] ...

Page 58

... Port2 Ingress Rate Control [15:8] Port2 Egress Rate Control [7:0] Reserved Reserved Port2 Egress Rate Control [15:8] Bank Select [7:0] Bank Select [15:8] 58 KSZ8842-16/32 MQL/MVL/MVLI/MBL Bank 52 Bank 53 Bank 54 Host Port Control 1 [7:0] Reserved Host Port Control 1 [15:8] Host Port Control 2 [7:0] ...

Page 59

... To 0xF 0xE 0xE - 0xF 0xF October 2007 Bank Location Bank 57 Bank 58 Bank 59 Reserved Reserved Reserved Reserved Reserved Reserved Reserved Bank Select [7:0] Bank Select [15:8] 59 KSZ8842-16/32 MQL/MVL/MVLI/MBL Bank 60 Bank 61 Bank 62 M9999-102207-1.9 Bank 63 ...

Page 60

... Description BARH Base Address High These bits are compared against the address on the bus ADDR[15:8] to determine the BASE for the KSZ8842M registers. BARL Base Address Low These bits are compared against the address on the bus ADDR[7:5] to determine the BASE for the KSZ8842M registers. ...

Page 61

... Synchronous and Asnychronous Transfers occur simultaneously. 0: normal. Write 1 to clear. Reserved Description Reserved BRL Burst Length (for burst read and write) 000: single. 011: fixed burst read length of 4. 101: fixed burst read length of 8. 111: fixed burst read length of 16. Reserved 61 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 62

... MARM[15:0] = EEPROM 0x2(MAC Byte 4 and 3) MARH[15:0] = EEPROM 0x3(MAC Byte 6 and 5) The Host MAC address is used to define the individual destination address that the KSZ8842M responds to when receiving frames. Network addresses are generally expressed in the form of 01:23:45:67:89:AB, where the bytes are received from left to right, and the bits within each byte are received from right to left (LSB to MSB). For example, the actual transmitted and received bits are on the order of 10000000 11000100 10100010 11100110 10010001 11010101 ...

Page 63

... Bank 3 On-Chip Bus Control Register (0x00): OBCR This register controls the on-chip bus speed for the KSZ8842M used for power management when the external host CPU is running at a slow frequency. The default of the on-chip bus speed is 125 MHz without EEPROM. When the external host CPU is running at a higher clock rate, the on-chip bus should be adjusted for the best performance ...

Page 64

... Software reset will affect PHY, MAC, QMU, DMA, and the switch core, only the BIU (base address registers) remains unaffected by a software reset. Description Reserved Bus Configuration (only for KSZ8842-16 device) 1: bus width is 16 bits. 0: bus width is 8 bits. (this bit is only avaiable when EEPROM is enabled) ...

Page 65

... Reserved RXFCE Receive Flow Control Enable When this bit is set, the KSZ8842M will acknowledge a PAUSE frame from the receive interface; i.e., the outgoing packets are pending in the transmit buffer until the PAUSE frame control timer expires. When this bit is cleared, flow control is not enabled. ...

Page 66

... When this bit is set, the KSZ8842M receives all incoming frames, regardless of the frame’s destination address. RXSCE Receive Strip CRC When this bit is set, the KSZ8842M strips the CRC on the received frames. Once cleared, the CRC is stored in memory following the packet. QMU Receive Multicast Hash-Table Enable When this bit is set, this bit enables the RX function to receive multicast frames that pass the CRC Hash filtering mechanism ...

Page 67

... When this bit is reset, the TX frame data pointer is manually controlled by user to access the TX frame location. Reserved TXFP TX Frame Pointer TX Frame Pointer index to the Frame Data register for access. This field reset to next available TX frame location when the TX Frame Data has been enqueued through the TXQ command register. 67 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 68

... This register is mapped into two uni-directional buffers for 16-bit buses, and one uni- directional buffer for 32-bit buses, (TXQ when Write, RXQ when Read) that allow moving words to and from the KSZ8842M regardless of whether the pointer is even, odd, or Dword aligned. Byte, word, and Dword access can be mixed on the fly in any order ...

Page 69

... When this bit is set, the Receive Process Stopped interrupt is enabled. When this bit is reset, the Receive Process Stopped interrupt is disabled. RXEFIE Receive Error Frame Interrupt Enable When this bit is set, the Receive error frame interrupt is enabled. When this bit is reset, the Receive error frame interrupt is disabled. Reserved 69 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 70

... This edge-triggered interrupt status is cleared by writing 1 to this bit. RXEFIE Receive Error Frame Interrupt Status When this bit is set, it indicates that the Receive error frame status has occurred. This edge-triggered interrupt status is cleared by writing 1 to this bit. Reserved 70 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 71

... RXCR register). RXCE Receive CRC Error When set, it indicates that a CRC error has occurred on the current received frame. A CRC error frame is passed to the host only if the pass bad frame bit is set (bit 9 in RXCR register). 71 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 72

... When the appropriate bit is cleared, the packet will drop. Note: When the receive all (RXRA) or receive multicast (RXRM) bit is set in the RXCR, all multicast addresses are received regardless of the multicast table value. 72 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 73

... Note: When the receive all (RXRA) or receive multicast (RXRM) bit is set in the RXCR, all multicast addresses are received regardless of the multicast table value. Description Family ID Chip family ID Chip ID 0x0 is assigned to KSZ8842M Revision ID Start Switch 1 = start the chip switch is disabled. Description Pass All Frames 1 = switch all packets including bad ones ...

Page 74

... Reserved Sniff Mode Select 1 =performs RX and TX sniff (both the source port and destination port need to match performs sniff (either the source port or destination port needs to match). This is the mode used to implement RX only sniff. 74 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 75

... Priority Buffer Reserve 1 = each port is pre-allocated 48 buffers, used exclusively for high priority (q3, q2, and q1) packets. Effective only when the multiple queue feature is turned on each port is pre-allocated 48 buffers used for all priority packets (q3, q2,q1, and q0). 75 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 76

... The switch supports only half duplex , 100BT in repeater mode. Switch Host Half-Duplex Mode The KSZ8842M supports only half-duplex 100-BaseT throughput in repeater mode enable host port interface half-duplex mode, this bit must be set for repeater mode 0 = enable host port interface full-duplex mode.. ...

Page 77

... PnLED2 LINK PnLED1 FULL_DPX/COL PnLED0 SPEED For repeater mode: [LEDSEL1, LEDSEL0] [0, 0] P1LED3; P2LED3 RPT_COL; RPT_ACT P1LED2; P2LED2 RPT_LINK3/RX; RPT_ERR3 P1LED1; P2LED1 RPT_LINK2/RX; RPT_ERR2 P1LED0; P2LED0 RPT_LINK1/RX; RPT_ERR1 Reserved Reserved 77 KSZ8842-16/32 MQL/MVL/MVLI/MBL [0, 1] ------ 100LINK/ACT 10LINK/ACT FULL_DPX [1, 1] ------ ------ ------ ------ [0, 1] [1, 0] [1, 1] ------ ------ ------ ------ M9999-102207-1.9 ...

Page 78

... Unknown Packet Default Port(s) Specify which ports to send packets with unknown destination addresses. Feature is enabled by bit [7]. Bit 2 for the host port, bit 1 for port 2, and bit 0 for port 1 Description MACA[47:32] Specifies MAC address 1. This value has to be same as MARH in Bank2. 78 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 79

... The value in this field is used as the frame’s priority when bits [7: TOS/DiffServ/Traffic Class value is 0x08. DSCP[3:2] The value in this field is used as the frame’s priority when bits [7: TOS/DiffServ/Traffic Class value is 0x04. DSCP[1:0] The value in this field is used as the frame’s priority when bits [7: TOS/DiffServ/Traffic Class value is 0x00. 79 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 80

... The value in this field is used as the frame’s priority when bits [7: TOS/DiffServ/Traffic Class value is 0x28. DSCP[19:18] The value in this field is used as the frame’s priority when bits [7: TOS/DiffServ/Traffic Class value is 0x24. DSCP[17:16] The value in this field is used as the frame’s priority when bits [7: TOS/DiffServ/Traffic Class value is 0x20. 80 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 81

... The value in this field is used as the frame’s priority when bits [7: TOS/DiffServ/Traffic Class value is 0x48. DSCP[35:34] The value in this field is used as the frame’s priority when bits [7: TOS/DiffServ/Traffic Class value is 0x44. DSCP[33:32] The value in this field is used as the frame’s priority when bits [7: TOS/DiffServ/Traffic Class value is 0x40. 81 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 82

... The value in this field is used as the frame’s priority when bits [7: TOS/DiffServ/Traffic Class value is 0x68. DSCP[51:50] The value in this field is used as the frame’s priority when bits [7: TOS/DiffServ/Traffic Class value is 0x64. DSCP[49:48] The value in this field is used as the frame’s priority when bits [7: TOS/DiffServ/Traffic Class value is 0x60. 82 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 83

... The value in this field is used as the frame’s priority when bits [7: TOS/DiffServ/Traffic Class value is 0x88. DSCP[67:66] The value in this field is used as the frame’s priority when bits [7: TOS/DiffServ/Traffic Class value is 0x84. DSCP[65:64] The value in this field is used as the frame’s priority when bits [7: TOS/DiffServ/Traffic Class value is 0x80. 83 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 84

... The value in this field is used as the frame’s priority when bits [7: TOS/DiffServ/Traffic Class value is 0xa8. DSCP[83:82] The value in this field is used as the frame’s priority when bits [7: TOS/DiffServ/Traffic Class value is 0xa4. DSCP[81:80] The value in this field is used as the frame’s priority when bits [7: TOS/DiffServ/Traffic Class value is 0xa0. 84 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 85

... The value in this field is used as the frame’s priority when bits [7: TOS/DiffServ/Traffic Class value is 0xc8. DSCP[99:98] The value in this field is used as the frame’s priority when bits [7: TOS/DiffServ/Traffic Class value is 0xc4. DSCP[97:96] The value in this field is used as the frame’s priority when bits [7: TOS/DiffServ/Traffic Class value is 0xc0. 85 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 86

... The value in this field is used as the frame’s priority when bits [7: TOS/DiffServ/Traffic Class value is 0xe0. Description Reserved Read High. Write Low 1 = read cycle write cycle. Table Select 00 = static MAC address table selected VLAN table selected dynamic address table selected MIB counter selected. Indirect Address Bit 9-0 of indirect address. 86 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 87

... Reserved Indirect Data Bit 66-64 of indirect data. Description Indirect Data Bit 47-32 of indirect data. Description Indirect Data Bit 63-48 of indirect data. Description Indirect Data Bit 15-0 of indirect data. Description Indirect Data Bit 31-16 of indirect data. 87 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 88

... Bank 44 Analog Testing Control Register 2 (0x0A): ATCR2 This register contains the user defined register for the switch function. Bit Default R/W 15-0 0x0000 RW October 2007 Description Reserved Reserved Description Reserved Reserved Description Reserved Reserved Description Reserved Reserved Description Reserved Description Reserved 88 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 89

... Reserved Disable Transmit 1 = disable transmit normal operation. Disable LED 1 = disable LED normal operation. 89 KSZ8842-16/32 MQL/MVL/MVLI/MBL Bit is same as: Bank 49 0x02 bit 8 Bank 49 0x02 bit 6 Bank 49 0x02 bit 7 Bank 49 0x02 bit 11 Bank 49 0x02 bit 13 Bank 49 0x02 bit 5 Bank 49 0x04 bit 15 Bank 49 0x02 bit 9 ...

Page 90

... Reserved AN Capable 1 = auto-negotiation capable not auto-negotiation capable. Link Status 1 = link is up link is down. Jabber test Not supported. Extended Capable 1 = extended register capable not extended register capable. 90 KSZ8842-16/32 MQL/MVL/MVLI/MBL Bit is same as: Bank 49 0x04 bit 6 Bank 49 0x04 bit 8 Bank49 0x04 bit 5 M9999-102207-1.9 ...

Page 91

... Adv 10 Full 1 = advertise 10 full-duplex capable not advertise 10 full-duplex capability. Adv 10 Half 1 = advertise 10 half-duplex capable not advertise 10 half-duplex capability. Selector Field 802.3 91 KSZ8842-16/32 MQL/MVL/MVLI/MBL Bit is same as: Bank 49 0x02 bit 4 Bank49 0x02 bit 3 Bank49 0x02 bit 2 Bank49 0x02 bit 1 Bank49 0x02 bit 0 M9999-102207-1.9 ...

Page 92

... End: TXP1/TXM1 (port normal operation. Force 100 1 = 100 Mbps Mbps. AN Enable 1 = auto-negotiation enabled auto-negotiation disabled. 92 KSZ8842-16/32 MQL/MVL/MVLI/MBL Bit is same as: Bank 49 0x04 bit 4 Bank 49 0x04 bit 3 Bank 49 0x04 bit 2 Bank 49 0x04 bit 1 Bank 49 0x04 bit 0 Bit is same as: Bank 51 0x02 bit 8 Bank 51 0x02 bit 6 Bank 51 0x02 bit 7 M9999-102207-1 ...

Page 93

... disable transmit normal operation. Disable LED disable LED normal operation. October 2007 KSZ8842-16/32 MQL/MVL/MVLI/MBL Bit is same as: Bank 51 0x02 bit 11 Bank 51 0x02 bit 13 Bank 51 0x02 bit 5 Bank 51 0x04 bit 15 Bank 51 0x02 bit 9 Bank 51 0x02 bit 10 Bank 51 0x02 bit 12 Bank 51 0x02 bit 14 Bank 51 0x02 bit 15 93 M9999-102207-1 ...

Page 94

... Link Status 1 = link is up link is down. Jabber test Not supported. Extended Capable 0 = not extended register capable. Description PHYID Low Low order PHYID bits. 94 KSZ8842-16/32 MQL/MVL/MVLI/MBL Bit is same as: Bank 51 0x04 bit 6 Bank 51 0x04 bit 8 Bank 51 0x04 bit 5 M9999-102207-1.9 ...

Page 95

... Adv 10 Full 1 = advertise 10 full-duplex capability not advertise 10 full-duplex capability. Adv 10 Half 1= advertise 10 half-duplex capability not advertise 10 half-duplex capability. Selector Field 802.3 95 KSZ8842-16/32 MQL/MVL/MVLI/MBL Bit is same as: Bank 51 0x02 bit 4 Bank 51 0x02 bit 3 Bank 51 0x02 bit 2 Bank 51 0x02 bit 1 Bank 51 0x02 bit 0 M9999-102207-1.9 ...

Page 96

... Vct 10M Short 1 = Less than 10m short. Reserved Vct_fault_count Distance to the fault. The distance is approximately 0.4m*vct_fault_count. 96 KSZ8842-16/32 MQL/MVL/MVLI/MBL Bit is same as: Bank 51 0x04 bit 4 Bank 51 0x04 bit 3 Bank 51 0x04 bit 2 Bank 51 0x04 bit 1 Bank 51 0x04 bit 0 Bit is same as: ...

Page 97

... Vct 10M Short 1 = Less than 10m short. Reserved Vct_fault_count Distance to the fault. The distance is approximately 0.4m*vct_fault_count. 97 KSZ8842-16/32 MQL/MVL/MVLI/MBL Bit is same as: Bank 49 0x04 bit 13 Bank 49 0x04 bit 7 Bank 49 0x00 bit 11 Bank 49 0x00 bit 10 Bank 49 0x00 bit 9 Bit is same as: ...

Page 98

... Remote (Near-End) Loopback (rlb perform remote loopback at Port 2's PHY(RXP2/RXM2 -> TXP2/TXM2. see Figure 16 normal operation Reserved 98 KSZ8842-16/32 MQL/MVL/MVLI/MBL Bit is same as: Bank 51 0x04 bit 13 Bank 51 0x04 bit 7 Bank 51 0x00 bit 11 Bank 51 0x00 bit 10 Bank 51 0x00 bit 9 M9999-102207-1.9 ...

Page 99

... The switch will not modify packets received without tags disable tag removal. TX Multiple Queues Select Enable 1 = the port output queue is split into four priority queues single output queue on the port. There is no priority differentiation even though packets are classified into high or low priority. 99 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 100

... Define the port’s Port VLAN membership. Bit 2 stands for the host port, bit 1 for port 2, and bit 0 for port 1. The port can only communicate within the membership. A ‘1’ includes a port in the membership; a ‘0’ excludes a port from the membership. 100 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 101

... Ingress and Egress rate limiting calculations. 0= IFG bytes are not counted. Count Preamble Count preamble Bytes each frame’s preamble bytes (8 per frame) are included in Ingress and Egress rate limiting calculations preamble bytes are not counted. 101 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 102

... Mbps 1101 = 72Mbps 1110 = 80Mbps 1111 = 88Mbps Note: For 10BT, rate settings above 10Mbps are set to the default value 0000 (not limited). 102 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 103

... Mbps 1101 = 72Mbps 1110 = 80Mbps 1111 = 88Mbps Note: For 10BT, rate settings above 10Mbps are set to the default value 0000 (not limited). 103 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 104

... Notes: For 10BT, rate settings above 10Mbps are set to the default value 0000 (not limited). When multiple queue select enable is off (only 1 queue per port), rate limiting applies only to priority 0 queue. 104 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 105

... Notes: For 10BT, rate settings above 10Mbps are set to the default value 0000 (not limited). When multiple queue select enable is off (only 1 queue per port), rate limiting applies only to priority 0 queue. 105 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 106

... Vct_fault_count 8-0 0x000 RO VCT fault count. Distance to the fault. It’s approximately 0.4m*vct_fault_count. October 2007 KSZ8842-16/32 MQL/MVL/MVLI/MBL Bit is same as: Bank 47 0x00 bit 12 Bank 47 0x00 bit 14-13 Bank 47 0x00 bit 15 Bank 47 0x02 bit 3 Bank 47 0x02 bit 2 Bank 47 0x02 bit 1 Bank 47 0x00 bit 8-0 106 M9999-102207-1 ...

Page 107

... RW Advertised flow control capability advertise flow control (pause) capability suppress flow control (pause) capability from transmission to link partner. October 2007 KSZ8842-16/32 MQL/MVL/MVLI/MBL Bit is same as: Bank 45 0x00 bit 0 Bank 45 0x00 bit1 Bank 45 0x00 bit 9 Bank 45 0x00 bit 2 Bank 45 0x00 bit 11 Bank 45 0x00 bit 3 ...

Page 108

... RO Reserved MDI-X status MDI MDI-X. October 2007 KSZ8842-16/32 MQL/MVL/MVLI/MBL Bit is same as: Bank 45 0x08 bit 8 Bank 45 0x08 bit 7 Bank 45 0x08 bit 6 Bank 45 0x08 bit 5 Bit is same as: Bank 45 0x00 bit 5 Bank 47 0x02 bit 5 Bank 45 0x02 bit 4 Bank 47 0x02 bit 4 108 ...

Page 109

... This register contains per port ingress rate control. See description in P1IRCR, Bank 48 (0x08) Bank 50 Port 2 Egress Rate Control Register (0x0A): P2ERCR This register contains per port egress rate control. See description in P1ERCR, Bank 48 (0x0A) October 2007 KSZ8842-16/32 MQL/MVL/MVLI/MBL Bit is same as: Bank 45 0x02 bit 5 Bank 45 0x02 bit 2 ...

Page 110

... RO Vct_fault_count VCT fault count. The distance to the fault is approximately 0.4m*vct_fault_count. October 2007 KSZ8842-16/32 MQL/MVL/MVLI/MBL Bit is same as: Bank 47 0x04 bit 12 Bank 47 0x04 bit 14-13 Bank 47 0x04 bit 15 Bank 47 0x06 bit 3 Bank 47 0x06 bit 2 Bank 47 0x06 bit 1 Bank 47 0x04 bit 8-0 110 M9999-102207-1 ...

Page 111

... RW Advertised flow control capability advertise flow control (pause) capability suppress flow control (pause) capability from transmission to the link partner. October 2007 KSZ8842-16/32 MQL/MVL/MVLI/MBL Bit is same as: Bank 46 0x00 bit 0 Bank 46 0x00 bit 1 Bank 46 0x00 bit 9 Bank 46 0x00 bit 2 Bank 46 0x00 bit 11 ...

Page 112

... Advertised 10BT half-duplex capability advertise 10BT half-duplex capability suppress 10BT half-duplex capability from transmission to the link partner. October 2007 KSZ8842-16/32 MQL/MVL/MVLI/MBL Bit is same as: Bank 46 0x08 bit 8 Bank 46 0x08 bit 7 Bank 46 0x08 bit 6 Bank 46 0x08 bit 5 112 M9999-102207-1.9 ...

Page 113

... Partner 10BT half-duplex capability link partner 10BT half-duplex capable link partner not 10BT half-duplex capable. October 2007 KSZ8842-16/32 MQL/MVL/MVLI/MBL Bit is same as: Bank 46 0x00 bit 5 Bank 47 0x06 bit 5 Bank 46 0x02 bit 4 Bank 47 0x06 bit 4 Bank 46 0x02 bit 5 Bank 46 0x02 bit 2 ...

Page 114

... Define the port’s Port VLAN membership. Bit 2 stands for host port, bit 1 for port 2, and bit 0 for port 1. The port can only communicate within the membership. A ‘1’ includes a port in the membership; a ‘0’ excludes a port from the membership. October 2007 KSZ8842-16/32 MQL/MVL/MVLI/MBL 114 M9999-102207-1.9 ...

Page 115

... This register contains per port ingress rate control. See description in P1IRCR, Bank 48 (0x08) Bank 52 Host Port Egress Rate Control Register (0x0A): P3ERCR This register contains per port egress rate control. See description in P1ERCR, Bank 48 (0x0A) Banks 53 – 63: Reserved Except Bank Select Register (0xE) October 2007 KSZ8842-16/32 MQL/MVL/MVLI/MBL 115 M9999-102207-1.9 ...

Page 116

... MIB (Management Information Base) Counters The KSZ8842M provides 34 MIB counters for each port. These counters are used to monitor the port activity for network management. The MIB counters are formatted “per port” as shown in Table 14 and “all ports dropped packet” as shown in Table 16 ...

Page 117

... Successfully Tx frames on a port for which Tx is inhibited by more than one collision Table 15. Port 1 MIB Counters Indirect Memory Offset Description Reserved Counter Value Description TX packets dropped due to lack of resources TX packets dropped due to lack of resources RX packets dropped due to lack of resources RX packets dropped due to lack of resources 117 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 118

... All Ports Dropped Packet MIB counters are not cleared after they are accessed. The application needs to keep track of overflow and valid conditions on these counters. October 2007 KSZ8842-16/32 MQL/MVL/MVLI/MBL // If bit restart (reread) from this register // If bit restart (reread) from this register 118 ...

Page 119

... The static DA look up result takes precedence over the dynamic DA look up result. If there match in both tables, the result from the static table is used. These entries in the static table will not be aged out by the KSZ8842M. Bit ...

Page 120

... Time Stamp Specifies the 2-bit counter for internal aging. Source port Identifies the source port where FID+MAC is learned: 00: port 1 01: port 2 10: port 3 FID Specifies the filter ID. MAC Address Specifies the 48-bit MAC address. 120 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 121

... R/W If 802.1Q VLAN mode is enabled, then KSZ8842M will assign a VID to every ingress packet. If the packet is untagged or tagged with a null VID, then the packet is assigned with the default port VID of the ingress port. If the packet is tagged with non null VID, then VID in the tag will be used. The look up process will start from the VLAN table look up. If the VID is not valid, then packet will be dropped and no address learning will take place ...

Page 122

... All Inputs All Outputs N/A N/A Table 21. Maximum Ratings Table 22. Operating Ratings /θ is under air velocity 0 m/ 122 KSZ8842-16/32 MQL/MVL/MVLI/MBL Value –0.5V to +4.0V –0.5V to +5V –0.5V to +4.0V 270°C –55°C to +150°C Min Typ 3.1V 3.3V 3.1V 3.3V 0°C 42.91 °C/W 19.6 ° ...

Page 123

... set Peak to peak 5MHz square wave 100Ω termination on the differential o output Peak to peak Table 23. Electrical Characteristics 123 KSZ8842-16/32 MQL/MVL/MVLI/MBL Min Typ Max 122mA 90mA 2.0V 0.8V -10µA 10µA 2.4V 0.4V 10µA +0.95V +1.05V 2% 3ns 5ns 0ns 0.5ns + 0 ...

Page 124

... Note 2: In order to speed up the ARDY low time to 40 ns, user has to use the turbo software driver which is only supported in the A6 device. Please refer to the “KSZ88xx Programmer's Guide” for detail. Table 24. Asynchronous Cycle (ADSN = 0) Timing Parameters October 2007 valid Figure 17. Asynchronous Cycle – ADSN = 0 124 KSZ8842-16/32 MQL/MVL/MVLI/MBL t2 t4 valid t5 t6 valid t8 t10 Min Typ ...

Page 125

... A6 device. Please refer to the “KSZ88xx Programmer's Guide” for detail. Table 25. Asynchronous Cycle using ADSN Timing Parameters October 2007 t8 valid t10 Figure 18. Asynchronous Cycle – Using ADSN 125 KSZ8842-16/32 MQL/MVL/MVLI/MBL valid t3 t5 valid t2 t9 t11 Min Typ Max Unit ...

Page 126

... Micrel, Inc. Asynchronous Timing using DATACSN (KSZ8842-32MQL/MVL device only) DATACSN Read Data RDN, WRN Write Data ARDY (Read Cycle) ARDY ( Write Cycle) Symbol Parameter t1 DATACSN setup to RDN, WRN active t2 DATACSN hold after RDN, WRN inactive (assume ADSN tied Low) t3 Read data hold to ARDY rising ...

Page 127

... Symbol Parameter t1 A1-A15, AEN, BExN[3:0] setup to ADSN t2 A1-A15, AEN, BExN[3:0] hold after ADSN rising t3 A4-A15, AEN to LDEVN delay October 2007 t1 t3 Figure 20. Address Latching Cycle for All Modes Table 27. Address Latching Timing Parameters 127 KSZ8842-16/32 MQL/MVL/MVLI/MBL t2 Min Typ Max Unit M9999-102207-1.9 ...

Page 128

... SRDYN hold to BCLK rising t10 DATACSN hold to BCLK rising t11 SWR hold to BCLK falling t12 CYCLEN hold to BCLK rising October 2007 Figure 21. Synchronous Burst Write Cycles – VLBUSN = 1 Table 28. Synchronous Burst Write Timing Parameters 128 KSZ8842-16/32 MQL/MVL/MVLI/MBL Min Typ Max Unit ...

Page 129

... DATACSN hold to BCLK rising t11 SWR hold to BCLK falling t12 CYCLEN hold to BCLK rising October 2007 data0 Figure 22. Synchronous Burst Read Cycles – VLBUSN = 1 Table 29. Synchronous Burst Read Timing Parameters 129 KSZ8842-16/32 MQL/MVL/MVLI/MBL t10 t11 t12 data1 data2 data3 Min Typ Max Unit ...

Page 130

... SRDYN setup to BCLK t10 SRDYN hold to BCLK t11 RDYRTNN setup to BCLK t12 RDYRTNN hold to BCLK Table 30. Synchronous Write (VLBUSN = 0) Timing Parameters October 2007 t2 valid t1 t5 Figure 23. Synchronous Write Cycle – VLBUSN = 0 130 KSZ8842-16/32 MQL/MVL/MVLI/MBL valid t9 t10 t11 t12 Min Typ Max Unit ...

Page 131

... SRDYN hold to BCLK t10 RDYRTNN setup to BCLK rising t11 RDYRTNN hold after BCLK rising Table 31. Synchronous Read (VLBUSN = 0) Timing Parameters October 2007 t2 valid t1 t5 Figure 24. Synchronous Read Cycle – VLBUSN = 0 131 KSZ8842-16/32 MQL/MVL/MVLI/MBL valid t8 t9 t10 t11 Min Typ Max Unit ...

Page 132

... Setup time th Hold time October 2007 D15 Figure 25. EEPROM Read Cycle Timing Diagram Min Typ 4 (OBCR[1:0]=11 on-chip bus speed @ 25 MHz) or 0.8 (OBCR[1:0]=00 on-chip bus speed @ 125 MHz Table 32. EEPROM Timing Parameters 132 KSZ8842-16/32 MQL/MVL/MVLI/MBL tcyc D13 D14 Max Unit µ M9999-102207-1.9 ...

Page 133

... Clock pulse to CTD data pulse t Clock pulse to CTC clock pulse Number of Clock/Data pulses per burst October 2007 Figure 26. Auto-Negotiation Timing Min Typ 100 55.5 64 111 128 17 Table 33. Auto Negotiation Timing Parameters 133 KSZ8842-16/32 MQL/MVL/MVLI/MBL Max Unit 69.5 µs 139 µs 33 M9999-102207-1.9 ...

Page 134

... Micrel, Inc. Reset Timing As long as the stable supply voltages to reset High timing (minimum of 10ms) are met, there is no power-sequencing requirement for the KSZ8842M supply voltage (3.3V). The reset timing requirement is summarized in the Figure 27 and Table 34. Symbol Parameter Stable supply voltages to reset High ...

Page 135

... HB726 Yes S558-5999-U7 Yes LF8505 Yes LF-H41S Yes TLA-6T718 Yes Table 36. Qualified Single Port Magnetic Value 25 ± Table 37. Typical Reference Crystal Characteristics 135 KSZ8842-16/32 MQL/MVL/MVLI/MBL Test Condition 100mV, 100kHz, 8mA 1MHz (min) 0MHz – 65MHz Number of Port Units MHz ppm pF Ω ...

Page 136

... Micrel, Inc. Package Information October 2007 Figure 28. 128-Pin PQFP Package. 136 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 137

... Micrel, Inc. October 2007 Figure 29. Optional 128-Pin LQFP Package 137 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 138

... Micrel, Inc. October 2007 Figure 30. Optional 100-Ball LFBGA Package 138 KSZ8842-16/32 MQL/MVL/MVLI/MBL M9999-102207-1.9 ...

Page 139

... ISA Industry Standard Architecture Jumbo Packet October 2007 KSZ8842-16/32 MQL/MVL/MVLI/MBL The host interface function that performs code conversion, buffering, and the like required for communications to and from a network. A packet containing ports, addresses, etc. to make sure data being passed through a bridged network arrives at its proper destination. ...

Page 140

... TDR Time Domain Reflectometry UTP Unshielded Twisted Pair VLAN Virtual Local Area Network October 2007 KSZ8842-16/32 MQL/MVL/MVLI/MBL An Ethernet port connection that allows network hubs or switches to connect to other hubs or switches without a null-modem, or crossover, cable. MDI provides the standard interface to a particular media (copper or fiber) and is therefore 'media dependent ...

Page 141

... A Purchaser’s use or sale of Micrel Products for use in life support appliances, devices or systems is a Purchaser’s own risk and Purchaser agrees to fully indemnify Micrel for any damages resulting from such use or sale. October 2007 KSZ8842-16/32 MQL/MVL/MVLI/MBL 1.2V (pin 91) 100 (0603-1/8W) © ...