WM8976GEFL/V Wolfson Microelectronics, WM8976GEFL/V Datasheet - Page 70

WM8976GEFL/V

Manufacturer Part Number

WM8976GEFL/V

Description

Audio CODECs Mono ADC Stereo DAC with Spkr

Manufacturer

Wolfson Microelectronics

Datasheet

1.WM8976GEFLV.pdf

(111 pages)

Specifications of WM8976GEFL/V

Mounting Style

SMD/SMT

Package / Case

QFN-32

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

- Current page: 70 of 111

- Download datasheet (2Mb)

WM8976

w

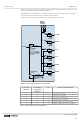

Table 55 Clock Control

The CLKSEL bit selects the internal source of the Master clock from the PLL (CLKSEL=1) or from

MCLK (CLKSEL=0). When the internal clock is switched from one source to another using the

CLKSEL bit, the clock originally selected must generate at least one falling edge after CLKSEL has

changed for the switching of clocks to be successful.

EXAMPLE:

If the PLL is the current source of the internal clock (CLKSEL=1) and it is required to switch to the

MCLK, change CLKSEL to select MCLK (CLKSEL=0) and then disable PLL (PLLEN=0).

R6

Clock

Generation

Control

REGISTER

ADDRESS

0

4:2

7:5

8

BIT

MS

BCLKDIV

MCLKDIV

CLKSEL

LABEL

0

000

010

1

DEFAULT

Sets the chip to be master over LRC and

BCLK

0=BCLK and LRC clock are inputs

1=BCLK and LRC clock are outputs

generated by the WM8976 (MASTER)

Configures the BCLK output frequency,

for use when the chip is master over

BCLK.

000=divide by 1 (BCLK=SYSCLK)

001=divide by 2 (BCLK=SYSCLK/2)

010=divide by 4

011=divide by 8

100=divide by 16

101=divide by 32

110=reserved

111=reserved

Sets the scaling for either the MCLK or

PLL clock output (under control of

CLKSEL)

000=divide by 1

001=divide by 1.5

010=divide by 2

011=divide by 3

100=divide by 4

101=divide by 6

110=divide by 8

111=divide by 12

Controls the source of the clock for all

internal operation:

0=MCLK

1=PLL output

DESCRIPTION

PD Rev 4.4 July 2009

Production Data

70

Related parts for WM8976GEFL/V

Image

Part Number

Description

Manufacturer

Datasheet

Request

R

Part Number:

Description:

Manufacturer:

Wolfson Microelectronics

Datasheet: