TDA9955HL/17/C1:55 NXP Semiconductors, TDA9955HL/17/C1:55 Datasheet

TDA9955HL/17/C1:55

Specifications of TDA9955HL/17/C1:55

TDA9955HL/17/C1-S

TDA9955HL/17/C1-S

Available stocks

Related parts for TDA9955HL/17/C1:55

TDA9955HL/17/C1:55 Summary of contents

Page 1

TDA9955HL Triple 8-bit analog-to-digital video converter for HDTV Rev. 01 — 17 March 2008 1. General description The TDA9955HL is a triple 8-bit video converter interface. The TDA9955HL converts an RGB analog signal into a RGB or YUV (YC signal ...

Page 2

... NXP Semiconductors I TTL inputs 5 V tolerant I LV-TTL outputs I Power-down mode I 1.8 V and 3.3 V power supplies 3. Applications I Set Top Box (STB) I YUV or RGB high-speed video digitizer I Projector, plasma and LCD TV I Rear projection TV I High-end TV 4. Ordering information Table 1. Type number TDA9955HL 5 ...

Page 3

... NXP Semiconductors 6. Functional diagram B1 ( B/U CHANNEL B2 ( (or Y) G/Y CHANNEL R/P CHANNEL CLAMP AVI CLOCK GENERATOR SOG/Y 1 SYNC SLICERS SOG/Y 2 HCSYNC1 HCSYNC2 ACTIVITY DETECTION VSYNC1 VSYNC2 I SYNC TIME MCLK MEASUREMENT Fig 2. Functional diagram TDA9955HL_1 Product data sheet Triple 8-bit analog-to-digital video converter for HDTV ...

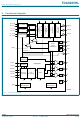

Page 4

... NXP Semiconductors 7. Pinning information 7.1 Pinning Fig 3. 7.2 Pin description Table 2. Symbol VPC1 VPC2 VPC3 V DDC(1V8) V SSC V DDO(3V3) V SSO VPC4 VPC5 VPC6 VPC7 V DDO(3V3) V SSO VCLK FREF/CS VREF/VS HREF/HS DE VAI_N V DDA(OSC)(3V3) V SSA(OSC) V DDA(BIAS)(3V3) V SSA(BIAS) TDA9955HL_1 Product data sheet Triple 8-bit analog-to-digital video converter for HDTV ...

Page 5

... NXP Semiconductors Table 2. Symbol BIAS V SSA V SSA(B) V DDA(B)(3V3) B2 REF_B B1 V DDA(B)(1V8) V SSA(B) V SSA(G) V DDA(G)(3V3) G2 REF_G G1 V DDA(G)(1V8) V SSA(G) V SSA(R) V DDA(R)(3V3) R2 REF_R R1 V DDA(R)(1V8) V SSA(R) SOG2 SOG1 V DDA(SOG)(3V3) V SSA(SOG) V DDA(SOG)(3V3) V SSA(SOG) V SSA(PLL) V SSA(PLL) V DDA(PLL)(3V3) ...

Page 6

... NXP Semiconductors Table 2. Symbol VSYNC1 VSYNC2 MCLK CLAMP COAST CKEXT A0 V DDI(3V3) SCL SDA V SSA V DDC(1V8) V SSC V DDO(3V3) V SSO VPA0 VPA1 VPA2 VPA3 V DDO(3V3) V SSO VPA4 VPA5 VPA6 VPA7 V DDO(3V3) V SSO VPB0 VPB1 VPB2 VPB3 V DDO(3V3) V SSO VPB4 VPB5 VPB6 VPB7 ...

Page 7

... This high-rate front end is designed to convert analog signals coming from an analog source (RGB or YUV) into parallel digital data used by media processor ICs such as the NXP Semiconductors Nexperia devices for HDTV or by other video signal ICs. The high-rate front end is able to output RGB YUV YUV semi-planar and YUV ITU-R BT ...

Page 8

... NXP Semiconductors 8.4 Activity detection The device detects the presence of signals on each sync input VSYNCx, HCSYNCx and SOGx after slicing to indicate which kind of synchronization is present (where x equals 1 or 2): • Digital separated syncs on VSYNCx and HCSYNCx • Analog composite sync on SOGx A change of activity is notifi HIGH-to-LOW transition on the VAI_N output pin. ...

Page 9

... NXP Semiconductors The origin of those pulses can be the VHREF timing generator or the SDRS block. 8.9 Color conversion The color conversion allows an RGB signal coming from the analog video interface to convert into YUV format or to convert a YUV signal coming from the analog video interface into an RGB format ...

Page 10

... NXP Semiconductors 8.13 Video port selection Each channel ( RGB mode affected to a specified video port VPA, VPB or VPC via the I 8.14 Output buffers The levels of the output buffers are LV-TTL compatible. The switch of the outputs between active and high-impedance is set by the I 8 ...

Page 11

Registers definitions The configuration of the registers is given in 2 Table 4. I C-bus registers; (R): reading register Register Sub R/W Bit definition addr 7 (MSB) VERSION 00h R 0 INPUT_SEL 01h W x Reserved for test 02h ...

Page 12

Table 4. I C-bus registers; (R): reading register Register Sub R/W Bit definition addr 7 (MSB) COARSE_GAINRV 20h W - FINE_GAINRV 21h W - AGC_HIGHRV 22h W AGC_LOWRV 23h W x COARSE_GAINBU 2Ah W - FINE_GAINBU 2Bh W - ...

Page 13

Table 4. I C-bus registers; (R): reading register Register Sub R/W Bit definition addr 7 (MSB) MAT_P21_MSB 8Dh W - MAT_P21_LSB 8Eh W MAT_P22_MSB 8Fh W - MAT_P22_LSB 90h W MAT_P23_MSB 91h W - MAT_P23_LSB 92h W MAT_P31_MSB 93h ...

Page 14

Table 4. I C-bus registers; (R): reading register Register Sub R/W Bit definition addr 7 (MSB) HS_MSB ABh W HS_E_LSB ACh W VREF_F1_S_MSB ADh W - VREF_F1_S_LSB AEh W VREF_F1_WIDTH AFh W VREF_F2_S_MSB B0h W - VREF_F2_S_LSB B1h W ...

Page 15

Table 4. I C-bus registers; (R): reading register Register Sub R/W Bit definition addr 7 (MSB) CLP_F2_LINE_S_LSB CFh W CLP_F2_LINE_WIDTH D0h W GAIN_S_LSB D1h W GAIN_MSB D2h W GAIN_E_LSB D3h W FDW_S_LSB D4h W FDW_MSB D5h W FDW_E_LSB D6h ...

Page 16

Table 4. I C-bus registers; (R): reading register Register Sub R/W Bit definition addr 7 (MSB) PD_AVI_CNTRL0 F4h W - PD_AVI_CNTRL1 F5h W - FVH_SEL F6h W - LSB_OUT_SEL F7h W OR_SEL F9h W x [1] The symbol ‘x’ ...

Page 17

... NXP Semiconductors 9.2.1 Version register Table 5. Legend default value Bit Symbol 9.2.2 Input selection register Table 6. Legend default value Bit Symbol VINS[1:0] 9.2.3 Sync detection recognition and separation registers Table 7. Legend default value Bit Table 8. Legend default value Bit Symbol Access Value Description ...

Page 18

... NXP Semiconductors Table 8. Legend default value Bit Symbol Access Value Description 6 SOGD2 DSSD2 SOGD1 DSSD1 R [1] When one of these bits changes, the VAI_N pin is pulled down until SDRS_FLAGS0 is read. 9.2.4 PLL registers Table 9. Legend default value Bit [1] By default, the SDRS toggles automatically the HSYNC to have an internal positive HSYNC signal ...

Page 19

... NXP Semiconductors Table 10. PLL_MNDIV registers (address 11h and 12h) bit description Legend default value Address Register 11h PLL_MNDIV_MSB 12h PLL_NDIV_LSB Table 11. Legend default value Bit 9.2.5 Pixel clocks generation registers Table 12. Legend default value Bit PHASE[4:0] TDA9955HL_1 Product data sheet Triple 8-bit analog-to-digital video converter for HDTV ...

Page 20

... NXP Semiconductors Table 13. Legend default value Bit Symbol CLKOUT_PRST[2: CLKFOR_PRST[1: CLKPIX_PRST[2:0] Table 14. Legend default value Bit CLKOUT_DIV[1: CLKFOR_DIV[1: CLKPIX_DIV[1:0] TDA9955HL_1 Product data sheet Triple 8-bit analog-to-digital video converter for HDTV PIXCLKGEN_PRST register (address 15h) bit description Access Value Description 110* 10* ...

Page 21

... NXP Semiconductors Table 14. Legend default value Bit Symbol 1 PR_DEL 0 PH_CORR Table 15. PHASE[4: Table 16. Relation between master division and clock division MDIV[1:0] Master semi-planar ITU-R BT.656 formatter clock division CLKOUT _DIV 9.2.6 Pixel clocks generation registers Table 17. Legend default value Bit Symbol ...

Page 22

... NXP Semiconductors Table 17. Legend default value Bit Symbol CLKFOR_SEL[1: 9.2.7 Clamp levels registers Table 18. Bright levels registers (address 1Ah to 1Ch) bit description Legend default value Addr Register Bit Symbol 1Ah BRIGHT_GY BRIGHT_ GY[7:0] W 1Bh BRIGHT_BU BRIGHT_ BU[7:0] W 1Ch BRIGHT_RV BRIGHT_ RV[7:0] W Table 19 ...

Page 23

... NXP Semiconductors Table 21. B/U video gain registers (addresses 2Ah to 2Dh) bit description Legend default value Addr Register Bit 2Ah COARSE_GAINBU COARSE_GY[3:0] W 2Bh FINE_GAINBU FINE_BU[6:0] 2Ch AGC_HIGHBU HIGH_BU[7:0] 2Dh AGC_LOWBU LOW_BU[6:0] Table 22. G/Y video gain registers (addresses 34h to 37h) bit description Legend default value ...

Page 24

... NXP Semiconductors 9.2.10 Color space conversion registers Table 24. Legend default value Bit and 0 MAT_SC[1:0] W Table 25. Offset input registers (address 81h to 86h) bit description [1] Legend default value Addr Register Bit Symbol 81h MAT_OI1_MSB MAT_OI1[8:6] 82h MAT_OI1_LSB OFFSET_IN1[5: 83h MAT_OI2_MSB MAT_OI2[8:6] 84h MAT_OI2_LSB OFFSET_IN2[5:0] ...

Page 25

... NXP Semiconductors Table 25. Offset input registers (address 81h to 86h) bit description [1] Legend default value Addr Register Bit Symbol 85h MAT_OI3_MSB MAT_OI3[8:6] 86h MAT_OI3_LSB OFFSET_IN3[5: [1] The default values correspond with the RGB full-scale to YC [2] The value is signed 11-bit two’s complement integer. ...

Page 26

... NXP Semiconductors Table 27. Offset output registers (address 99h to 9Eh) bit description [1] Legend default value Addr Register Bit Symbol 99h MAT_OO1_MSB OFFSET_OUT1[10:8] W 9Ah MAT_OO1_LSB OFFSET_OUT1[7:0] 9Bh MAT_OO2_MSB OFFSET_OUT2[10:8] W 9Ch MAT_OO2_LSB OFFSET_OUT2[7:0] 9Dh MAT_OO3_MSB OFFSET_OUT3[10:8] W 9Eh MAT_OO3_LSB OFFSET_OUT3[7:0] 9Fh MAT_BYPASS MAT_BP [1] The default values correspond with the RGB full-scale to YC [2] The value is signed 11-bit two’ ...

Page 27

... NXP Semiconductors line 1 pixel 1 line counter counts iHS pulses modulo NLIN iHS Fig 4. Line and pixel counters Table 30. Horizontal reference registers (address A7h to A9h) bit description Legend default value Address Register Bit A7h HREF_S_LSB HREF_START[7:0] A8h HREF_MSB HREF_START[11: HREF_END[11:8] A9h HREF_E_LSB HREF_END[7:0] Table 31 ...

Page 28

... NXP Semiconductors Table 32. Vertical reference registers (address ADh to B2h) bit description Legend default value Addr Register Bit ADh VREF_F1_S_MSB VREF_F1_START[10:8] AEh VREF_F1_S_LSB VREF_F1_START[7:0] AFh VREF_F1_WIDTH VREF_F1_WIDTH[7:0] B0h VREF_F2_S_MSB VREF_F2_START[10:8] B1h VREF_F2_S_LSB VREF_F2_START[7:0] B2h VREF_F2_WIDTH VREF_F2_WIDTH[7:0] [1] In progressive case, bits VREF_F2_START[10:0] and VREF_F2_WIDTH[7:0] must be set to logic 0. ...

Page 29

... NXP Semiconductors Table 33. Vertical sync registers (address B3h to BEh) bit description Legend default value Addr Register Bit B9h VS_F1_PIX_S_LSB VS_F1_PIX_START[7:0] BAh VS_F1_PIX_MSB VS_F1_PIX_START[11: VS_F1_PIX_END[11:8] BBh VS_F1_PIX_E_LSB VS_F1_PIX_END[7:0] BCh VS_F2_PIX_S_LSB VS_F2_PIX_START[7:0] BDh VS_F2_PIX_MSB VS_F2_PIX_START[11: VS_F2_PIX_END[11:8] BEh VS_F2_PIX_E_LSB VS_F2_PIX_END[7:0] [1] In progressive case bits VS_F2_LINE_START[12:0] and VS_F2_LINE_WIDTH[7:0] must be set to logic 0. ...

Page 30

... NXP Semiconductors line 1 pixel 1 blanking period HREF (1) HREF_START[11:0] Fig 6. HREF and VREF in progressive case Table 34. Field reference registers (address BFh to C1h) bit description Legend default value Addr Register Bit BFh FREF_F1_S_LSB FREF_F1_START[7:0] C0h FREF_POL_MSB FREF_F1_START[10: FREF_F2_START[10:8] W C1h FREF_F2_S_LSB FREF_F2_START[7:0] TDA9955HL_1 Product data sheet ...

Page 31

... NXP Semiconductors line 1 pixel 1 blanking period FREF changes state at pixel 1 Fig 7. FREF in interlaced case Table 35. Clamp signal registers (address C8h to CAh) bit description Legend default value Addr Register Bit C8h CLAMP_PIX_S_LSB CLAMP_ PIX_ START[7:0] C9h CLAMP_PIX_MSB CLAMP_ PIX_ START[11: CLAMP_ PIX_ END[11:8] ...

Page 32

... NXP Semiconductors Table 36. CLP_Fx_LINE_nnn registers (address CBh to D0h) bit description Legend default value Addr Register CEh CLP_F2_LINE_S_MSB CFh CLP_F2_LINE_S_LSB CLAMP_F2_LINE_START[7:0] D0h CLP_F2_LINE_WIDTH CLAMP_F2_LINE_WIDTH[7:0] Table 37. GAIN signal registers (address D1h to D3h) bit description Legend default value Address Register Bit D1h GAIN_S_LSB GAIN_START[7:0] ...

Page 33

... NXP Semiconductors Table 39. Measured lines and pixels registers (address D7h to DAh) bit description Legend default value Addr Register Bit D7h ASD_MEASLIN_MSB MEAS_LINES[10:8] R D8h MEASLIN_LSB MEAS_LINES[7:0] D9h MEASPIX_MSB MEAS_PIX[11:8] DAh MEASPIX_LSB MEAS_PIX[7:0] Table 40. Blanking code registers (address DCh to DFh) bit description Legend default value ...

Page 34

... NXP Semiconductors [1] These register control the blanking code of the x/x channel; this code is output during the horizontal blanking (HREF is LOW) or the vertical blanking (VREF is HIGH) 9.2.12 Prefiltering register (PRE_FILTERS) This register is used to downsample the R/P semi-planar and ITU-R BT.656 formats. ...

Page 35

... NXP Semiconductors 9.2.14 Output formatter register Table 43. Legend default value Bit and 0 FOR_SEL[1: the video is output on three video ports, one per color. [ semi-planar, the video is output on two video ports, one for luminance (Y) and one for chrominance (C [ ITU-R BT.656, the video is output on one video port (C Table 44 ...

Page 36

... NXP Semiconductors 9.2.15 Sync output selection registers Table 45. Legend default value Bit 9.2.16 Output polarity control register Table 46. Legend default value Bit TDA9955HL_1 Product data sheet Triple 8-bit analog-to-digital video converter for HDTV CSVSHS_SEL register (address E8h) bit description Symbol Access Value Description ...

Page 37

... NXP Semiconductors Table 46. Legend default value Bit 1 0 9.2.17 Video ports control register Table 47. Legend default value Bit 7 and and 4 VPC_SEL[1: and 2 VPB_SEL[1: and 0 VPA_SEL[1:0] W Table 48. Data stream selection VPx_SEL[1: RGB high-impedance 9.2.18 Data enable signal control register Table 49. Legend default value ...

Page 38

... NXP Semiconductors Table 49. Legend default value Bit Symbol 5 DE_PXQ 4 DE_POL apx : active panel - HREF_PXQ = 0 HREF HREF_PXQ = 1 DE_PXQ = 0 DE DE_PXQ = 1 Fig 8. Pixel qualification 9.2.19 Software reset registers Table 50. Legend default value Bit Symbol RST_MAN W 3 RST_AVI TDA9955HL_1 Product data sheet Triple 8-bit analog-to-digital video converter for HDTV ...

Page 39

... NXP Semiconductors Registers that are reset to the default value are as follows: • Video gain registers (address 20h to 3Eh) • Color space conversion registers (address 80h to 9Eh) • VHREF timing registers (address A0h to DFh) • Prefiltering registers (address E0h) • Output formatter registers (address E1h to E5h) • ...

Page 40

... NXP Semiconductors Table 52. Legend default value Bit Symbol 1 PD_ADC_GY W 0 PD_ADC_RV W Table 53. Legend default value Bit Symbol FVH_SEL Table 54. Legend default value Bit Symbol LSB_SEL Table 55. Legend default value Bit 7 and 6 TDA9955HL_1 Product data sheet Triple 8-bit analog-to-digital video converter for HDTV ...

Page 41

... NXP Semiconductors Table 55. Legend default value Bit [1] Defines the internal signals on ORGY, ORBU and ORRV. [2] The signals are not effected by changing the position of the digital output ports with register EAh. 10. Limiting values Table 56. In accordance with the Absolute Maximum Rating System (IEC 60134). ...

Page 42

... NXP Semiconductors 12. Characteristics Table 58. Characteristics 3. 3. DDA(3V3) DDI(3V3) DDO(3V3) values measured DDA(3V3) otherwise specified. Symbol Parameter Supplies V analog supply voltage (3.3 V) DDA(3V3) V analog supply voltage (1.8 V) DDA(1V8) V input supply voltage (3.3 V) DDI(3V3) V core supply voltage (1.8 V) DDC(1V8) V output supply voltage (3.3 V) ...

Page 43

... NXP Semiconductors Table 58. Characteristics …continued 3. 3. DDA(3V3) DDI(3V3) DDO(3V3) values measured DDA(3V3) otherwise specified. Symbol Parameter Clamps N clamping accuracy CL M channel-to-channel clamp matching CL(CTC) Phase-locked loop (PLL) of analog video part t peak-to-peak PLL jitter time jit(PLL)(p-p) N number of pixels pix f reference clock frequency ...

Page 44

... NXP Semiconductors Table 58. Characteristics …continued 3. 3. DDA(3V3) DDI(3V3) DDO(3V3) values measured DDA(3V3) DDI(3V3) otherwise specified. Symbol Parameter LV-TTL digital outputs (VPA0 to VPA7, VPB0 to VPB7, VPC0 to VPC7, VCLK, DE, HS, VS, CS, HREF, VREF, FREF) V LOW-level output voltage OL V HIGH-level output voltage C-bus (fast-mode tolerant; SCL and SDA) ...

Page 45

... NXP Semiconductors Table 59. Output formats (register OUTPUT_CTRL = EAh) Signal RGB YUV VPA0 R0 V0 VPA1 R1 V1 VPA2 R2 V2 VPA3 R3 V3 VPA4 R4 V4 VPA5 R5 V5 VPA6 R6 V6 VPA7 R7 V7 VPB0 B0 U0 VPB1 B1 U1 VPB2 B2 U2 VPB3 B3 U3 VPB4 B4 U4 VPB5 B5 U5 VPB6 B6 U6 ...

Page 46

... NXP Semiconductors VPA0 to VPA7 VPB0 to VPB7 VPC0 to VPC7 VCLK Fig 12. YUV format data timing VPA0 to VPA7 VPB0 to VPB7 VPC0 to VPC7 VCLK HREF start of active line Fig 13. YUV semi-planar format data timing (1) With SAV/EAV timing codes (2) Without SAV/EAV timing codes Fig 14. YUV ITU-R BT.656 format data timing with blanking code ...

Page 47

... NXP Semiconductors Y 621 622 623 HREF VREF FREF 2nd field 310 HREF VREF FREF Fig 15. 576i timing in automatic mode TDA9955HL_1 Product data sheet Triple 8-bit analog-to-digital video converter for HDTV 624 625 1st field 311 312 313 314 315 316 Rev. 01 — 17 March 2008 ...

Page 48

... NXP Semiconductors Y 521 HREF VREF FREF Y 258 259 260 HREF VREF FREF 1st field Fig 16. 480i timing in automatic mode TDA9955HL_1 Product data sheet Triple 8-bit analog-to-digital video converter for HDTV 522 523 524 525 261 262 263 264 265 266 2nd field Rev. 01 — ...

Page 49

... NXP Semiconductors 13. Package outline LQFP100: plastic low profile quad flat package; 100 leads; body 1 pin 1 index 100 DIMENSIONS (mm are the original dimensions) A UNIT max. 0.15 1.45 1.6 mm 0.25 0.05 1.35 Note 1. Plastic or metal protrusions of 0.25 mm maximum per side are not included. ...

Page 50

... NXP Semiconductors 14. Soldering An in-depth account of reflow soldering can be found in Application Note AN10365 “Surface mount reflow soldering description” . 15. Revision history Table 60. Revision history Document ID Release date TDA9955HL_1 20080317 TDA9955HL_1 Product data sheet Triple 8-bit analog-to-digital video converter for HDTV Data sheet status ...

Page 51

... Right to make changes — NXP Semiconductors reserves the right to make changes to information published in this document, including without limitation specifications and product descriptions, at any time and without notice ...

Page 52

... NXP Semiconductors 18. Contents 1 General description . . . . . . . . . . . . . . . . . . . . . . 1 2 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 3 Applications . . . . . . . . . . . . . . . . . . . . . . . . . . . . 2 4 Ordering information . . . . . . . . . . . . . . . . . . . . . 2 5 Block diagram . . . . . . . . . . . . . . . . . . . . . . . . . . 2 6 Functional diagram . . . . . . . . . . . . . . . . . . . . . . 3 7 Pinning information . . . . . . . . . . . . . . . . . . . . . . 4 7.1 Pinning . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 4 7.2 Pin description . . . . . . . . . . . . . . . . . . . . . . . . . 4 8 Functional description . . . . . . . . . . . . . . . . . . . 7 8.1 Analog multiplexers 8.2 R/P , B/P and G/Y channels 8.2.1 Clamps . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 7 8.2.2 ADCs ...