MT41J256M8HX-15E:D Micron Technology Inc, MT41J256M8HX-15E:D Datasheet - Page 86

MT41J256M8HX-15E:D

Manufacturer Part Number

MT41J256M8HX-15E:D

Description

MICMT41J256M8HX-15E:D 2GB:X4,X8,X16 DDR3

Manufacturer

Micron Technology Inc

Type

DDR3 SDRAMr

Series

-r

Specifications of MT41J256M8HX-15E:D

Organization

256Mx8

Address Bus

18b

Maximum Clock Rate

1.333GHz

Operating Supply Voltage (typ)

1.5V

Package Type

FBGA

Operating Temp Range

0C to 95C

Operating Supply Voltage (max)

1.575V

Operating Supply Voltage (min)

1.425V

Supply Current

165mA

Pin Count

78

Mounting

Surface Mount

Operating Temperature Classification

Commercial

Format - Memory

RAM

Memory Type

DDR3 SDRAM

Memory Size

2G (256M x 8)

Speed

667MHz

Interface

Parallel

Voltage - Supply

1.425 V ~ 1.575 V

Operating Temperature

0°C ~ 95°C

Package / Case

78-TFBGA

Lead Free Status / RoHS Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MT41J256M8HX-15E:D

Manufacturer:

SAMSUNG

Quantity:

1 001

Company:

Part Number:

MT41J256M8HX-15E:D

Manufacturer:

MICRON

Quantity:

11 200

Company:

Part Number:

MT41J256M8HX-15E:D

Manufacturer:

MICRON21

Quantity:

1 684

Company:

Part Number:

MT41J256M8HX-15E:D

Manufacturer:

Micron Technology Inc

Quantity:

10 000

Part Number:

MT41J256M8HX-15E:D

Manufacturer:

MICRON/美光

Quantity:

20 000

Company:

Part Number:

MT41J256M8HX-15E:D TR

Manufacturer:

Micron Technology Inc

Quantity:

10 000

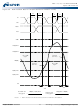

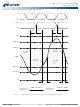

Data Setup, Hold, and Derating

Table 61:

PDF: 09005aef826aaadc/Source: 09005aef82a357c3

DDR3_D3.fm - Rev G 2/09 EN

t

t

t

DH (base) DC100

DS (base) AC175

DS (base) AC150

Symbol

Data Setup and Hold Values at 1 V/ns (DQS, DQS# at 2 V/ns) – AC/DC-Based

DDR3-800

125

150

75

The total

sheet

page 70) to the Δ

Example:

signal has to remain above/below V

page 88).

Although the total setup time for slow slew rates might be negative (for example, a valid

input signal will not have reached V

tion), a valid input signal is still required to complete the transition and to reach V

V

derating values may obtained by linear interpolation.

Setup (

last crossing of V

rate for a falling signal is defined as the slew rate between the last crossing of V

and the first crossing of V

nominal slew rate line between the shaded “V

slew rate for derating value (see Figure 36 on page 89). If the actual signal is later than the

nominal slew rate line anywhere between the shaded “V

rate of a tangent line to the actual signal from the AC level to the DC level is used for

derating value (see Figure 38 on page 91).

Hold (

last crossing of V

rate for a falling signal is defined as the slew rate between the last crossing of

V

nominal slew rate line between the shaded “DC-to-V

slew rate for derating value (see Figure 37 on page 90). If the actual signal is earlier than

the nominal slew rate line anywhere between the shaded “DC-to-V

slew rate of a tangent line to the actual signal from the “DC-to-V

for derating value (see Figure 39 on page 92).

IL

IH

(

(

AC

DC

t

). For slew rates which fall between the values listed in Table 63 on page 87, the

t

DS (base) and

DH) nominal slew rate for a rising signal is defined as the slew rate between the

) MIN and the first crossing of V

t

DS) nominal slew rate for a rising signal is defined as the slew rate between the

DDR3-1066

t

t

DS (setup time) and

DS (total setup time) =

100

25

75

t

REF

IL

DS and Δ

(

DC

(

DC

t

DH (base) values (see Table 61; values come from Table 56 on

) MAX and the first crossing of V

) and the first crossing of V

DDR3-1333

IL

t

DH derating values (see Table 62 on page 87), respectively.

(

AC

30

65

–

86

) MAX. If the actual signal is always earlier than the

t

DH (hold time) required is calculated by adding the data

t

DS (base) + Δ

IH

IH

(

[

REF

AC

AC

Micron Technology, Inc., reserves the right to change products or specifications without notice.

DDR3-1600

)/V

]/V

(

DC

10

45

IL

IL

–

). If the actual signal is always later than the

(

[

REF

AC

AC

t

DS. For a valid transition, the input

) for some time

]) at the time of the rising clock transi-

(

2Gb: x4, x8, x16 DDR3 SDRAM

DC

IH

(

)-to-AC region,” use the nominal

REF

AC

REF

) MIN. Setup (

(

REF

DC

(

Units

DC

ps

ps

ps

(

) region,” use the nominal

DC

). Hold (

©2006 Micron Technology, Inc. All rights reserved.

)-to-AC region,” the slew

REF

t

VAC (see Table 64 on

Speed Bin Tables

REF

(

DC

t

DH) nominal slew

t

DS) nominal slew

(

) region” is used

V

V

V

DC

IH

IH

IH

Reference

) region,” the

(

(

(

AC

AC

DC

)/V

)/V

)/V

REF

IL

IL

IL

(

(

(

AC

AC

DC

(

IH

DC

)

)

)

/

)