IDT5T93GL06NLGI8 IDT, Integrated Device Technology Inc, IDT5T93GL06NLGI8 Datasheet

IDT5T93GL06NLGI8

Specifications of IDT5T93GL06NLGI8

Available stocks

Related parts for IDT5T93GL06NLGI8

IDT5T93GL06NLGI8 Summary of contents

Page 1

LVDS, 1:6 Glitchless Clock Buffer TERABUFFER™ II General Description The IDT5T93GL06 2.5V differential clock buffer is a user- selectable differential input to six LVDS outputs. The fanout from a differential input to six LVDS outputs reduces loading on the ...

Page 2

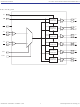

IDT5T93GL06 Data Sheet Block Diagram SEL FSEL IDT5T93GL06 REVISION C OCTOBER 1, 2009 2.5V LVDS 1:6 GLITCHLESS CLOCK BUFFER TERABUFFER™ II OUTPUT CONTROL OUTPUT CONTROL OUTPUT CONTROL OUTPUT CONTROL OUTPUT ...

Page 3

IDT5T93GL06 Data Sheet Table 1. Pin Descriptions Name Type A[1:2] Input Adjustable A[1:2] Input Adjustable G Input LVTTL GL Input LVTTL Q[1:2] Output LVDS Q[1:2] Output LVDS SEL Input LVTTL PD Input LVTTL FSEL Input LVTTL V Power DD GND ...

Page 4

IDT5T93GL06 Data Sheet Function Tables Table 3A. Gate Control Output Table Control Output GL G Q[1: Toggling 0 1 LOW 1 0 Toggling 1 1 HIGH Table 3B. Input Selection Table Selection SEL pin 0 1 Absolute Maximum ...

Page 5

IDT5T93GL06 Data Sheet DC Electrical Characteristics Table 4A. LVDS Power Supply DC Characteristics Symbol Parameter Quiescent DDQ Power Supply Current Total Power I TOT V Supply Current DD Total Power Down I PD Supply Current NOTE 1: ...

Page 6

IDT5T93GL06 Data Sheet Table 4D. LVDS DC Characteristics Symbol Parameter Differential Output Voltage for the V OT(+) True Binary State Differential Output Voltage for the V OT(–) False Binary State Change in V Between Complementary ∆ Output States ...

Page 7

IDT5T93GL06 Data Sheet Table 5B. eHSTL AC Differential Input Characteristics, T Symbol Parameter (1) V Input Signal Swing DIF V Differential Input Signal Crossing Point X D Duty Cycle H V Input Timing Measurement Reference Level THI ...

Page 8

IDT5T93GL06 Data Sheet Table 5E. AC Differential Input Characteristics Symbol Parameter ( Differential Voltage DIF V Differential Input Cross Point Voltage X V Common Mode Input Voltage Range CM V Input Voltage IN NOTE 1.The output will not ...

Page 9

IDT5T93GL06 Data Sheet Differential AC Timing Waveforms Output Propagation and Skew Waveforms 1/ [1:2] [1:2] t PLH SK( NOTE 1: Pulse skew is calculated using the following expression ...

Page 10

IDT5T93GL06 Data Sheet Glitchless Output Operation with Switching Input Clock Selection SEL When SEL changes, the output clock goes LOW on the falling edge of the ...

Page 11

IDT5T93GL06 Data Sheet FSEL Operation for When Opposite Clock Dies 1. When the differential on the non-selected clock goes below the minimum DC differential, the outputs clock goes to an unknown state. When this happens, the FSEL pin should be ...

Page 12

IDT5T93GL06 Data Sheet Power Down Timing NOTE recommended that outputs be disabled before entering power-down mode also recommended that the ...

Page 13

IDT5T93GL06 Data Sheet Test Circuits and Conditions Test Circuit for Differential Input V IN Pulse Generator V IN Table 6A. Differential Input Test Conditions Symbol V = 2.5V ± 0. Crossing of A and A THI IDT5T93GL06 REVISION ...

Page 14

IDT5T93GL06 Data Sheet Test Circuit for DC Outputs and Power Down Tests V A Pulse Generator D.U.T. A Test Circuit for Propagation, Skew, and Gate Enable/Disable Timing A Pulse Generator D.U.T. A Table 6B. Differential Input Test Conditions Symbol V ...

Page 15

IDT5T93GL06 Data Sheet Recommended Landing Pattern 5.20 0.35 IDT5T93GL06 REVISION C OCTOBER 1, 2009 6.30 4.80 4.80 0.65 5.20 15 2.5V LVDS 1:6 GLITCHLESS CLOCK BUFFER TERABUFFER™ II 6.30 ©2009 Integrated Device Technology, Inc. ...

Page 16

IDT5T93GL06 Data Sheet Ordering Information Table 7. Ordering Information XX XXXXX IDT Package Device Type IDT5T93GL06 REVISION C OCTOBER 1, 2009 X Process I NL NLG 5T93GL06 16 2.5V LVDS 1:6 GLITCHLESS CLOCK BUFFER TERABUFFER™ +85 ...

Page 17

IDT5T93GL06 Data Sheet Revision History Sheet Rev Table Page Description of Change T3A 4 Added Gate Control Output Table. B T3B 4 Added Input Selection Table. Converted datasheet format. 1 Pin Assignment - added GND pad to diagram ...

Page 18

IDT5T93GL06 Data Sheet 6024 Silver Creek Valley Road Sales 800-345-7015 (inside USA) San Jose, California 95138 +408-284-8200 (outside USA) Fax: 408-284-2775 www.IDT.com/go/contactIDT DISCLAIMER Integrated Device Technology, Inc. (IDT) and its subsidiaries reserve the right to modify the products and/or specifications ...