ADC0804LCN/NOPB National Semiconductor, ADC0804LCN/NOPB Datasheet - Page 19

ADC0804LCN/NOPB

Manufacturer Part Number

ADC0804LCN/NOPB

Description

IC ADC 8BIT MPU COMPAT 20-DIP

Manufacturer

National Semiconductor

Datasheet

1.ADC0804LCWMX.pdf

(41 pages)

Specifications of ADC0804LCN/NOPB

Number Of Bits

8

Number Of Converters

1

Power Dissipation (max)

875mW

Voltage Supply Source

Single Supply

Operating Temperature

0°C ~ 70°C

Mounting Type

Through Hole

Package / Case

20-DIP (0.300", 7.62mm)

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

*ADC0804LCN

*ADC0804LCN/NOPB

ADC0804

*ADC0804LCN/NOPB

ADC0804

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

ADC0804LCN/NOPB

Manufacturer:

MICRON

Quantity:

1 000

Functional Description

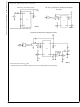

Note 13: CS shown twice for clarity.

Note 14: SAR = Successive Approximation Register.

After the “1” is clocked through the 8-bit shift register (which

completes the SAR search) it appears as the input to the

D-type latch, LATCH 1. As soon as this “1” is output from the

shift register, the AND gate, G2, causes the new digital word

to transfer to the TRI-STATE output latches. When LATCH 1

is subsequently enabled, the Q output makes a high-to-low

transition which causes the INTR F/F to set. An inverting

buffer then supplies the INTR input signal.

Note that this SET control of the INTR F/F remains low for 8

of the external clock periods (as the internal clocks run at

of the frequency of the external clock). If the data output is

continuously enabled (CS and RD both held low), the INTR

output will still signal the end of conversion (by a high-to-low

transition), because the SET input can control the Q output

of the INTR F/F even though the RESET input is constantly

at a “1” level in this operating mode. This INTR output will

therefore stay low for the duration of the SET signal, which is

8 periods of the external clock frequency (assuming the A/D

is not started during this interval).

When operating in the free-running or continuous conversion

mode (INTR pin tied to WR and CS wired low — see also

section 2.8), the START F/F is SET by the high-to-low tran-

sition of the INTR signal. This resets the SHIFT REGISTER

(Continued)

FIGURE 4. Block Diagram

1

⁄

8

19

which causes the input to the D-type latch, LATCH 1, to go

low. As the latch enable input is still present, the Q output will

go high, which then allows the INTR F/F to be RESET. This

reduces the width of the resulting INTR output pulse to only

a few propagation delays (approximately 300 ns).

When data is to be read, the combination of both CS and RD

being low will cause the INTR F/F to be reset and the

TRI-STATE output latches will be enabled to provide the 8-bit

digital outputs.

2.1 Digital Control Inputs

The digital control inputs (CS, RD, and WR) meet standard

T

when compared to the standard A/D Start and Output Enable

labels. In addition, these inputs are active low to allow an

easy interface to microprocessor control busses. For

non-microprocessor based applications, the CS input (pin 1)

can be grounded and the standard A/D Start function is

obtained by an active low pulse applied at the WR input (pin

3) and the Output Enable function is caused by an active low

pulse at the RD input (pin 2).

2

L logic voltage levels. These signals have been renamed

DS005671-13

www.national.com