MAX1304ECM+T Maxim Integrated Products, MAX1304ECM+T Datasheet - Page 24

MAX1304ECM+T

Manufacturer Part Number

MAX1304ECM+T

Description

IC ADC 12BIT 8CH 4MSPS 48LQFP

Manufacturer

Maxim Integrated Products

Datasheet

1.MAX1304ECM.pdf

(37 pages)

Specifications of MAX1304ECM+T

Number Of Bits

12

Sampling Rate (per Second)

3.65M

Data Interface

Parallel

Number Of Converters

1

Power Dissipation (max)

1.82W

Voltage Supply Source

Analog and Digital

Operating Temperature

-40°C ~ 85°C

Mounting Type

Surface Mount

Package / Case

48-LQFP

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

At power-up, all channels are selected for conversion

(see the Configuration Register section). After applying

power, allow the 1ms wake-up time to elapse and then

initiate a dummy conversion and discard the results.

After the dummy conversion is complete, accurate con-

versions can be obtained.

During shutdown the internal reference and analog

circuits in the device shutdown and the analog supply

current drops to 0.6µA (typ). Select shutdown mode

using the SHDN input. Set SHDN high to enter shut-

down mode. SHDN takes precedence over CHSHDN.

Entering and exiting shutdown mode does not change

the configuration byte. However, a new configuration

byte can be written while in shutdown mode by follow-

ing the standard write procedure shown in Figure 6.

EOC and EOLC are high when the MAX1304–MAX1306/

MAX1308–MAX1310/MAX1312–MAX1314 are shut down.

The state of the digital outputs D0–D11 is independent

of the state of SHDN. If CS and RD are low, the digital

outputs D0–D11 are active regardless of SHDN. The

digital outputs only go high impedance when CS or RD

is high. When the digital outputs are powered down, the

digital supply current drops to 20nA.

8-/4-/2-Channel, 12-Bit, Simultaneous-Sampling ADCs

with ±10V, ±5V, and 0 to +5V Analog Input Ranges

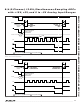

Figure 9. Read After Conversion—Eight Channels Selected, External Clock

24

CONVST

D0–D11

EOLC

______________________________________________________________________________________

EOC

CS*

RD

* CS CAN BE LOW AT ALL TIMES, LOW DURING THE RD CYCLES, OR THE SAME AS RD.

ONLY LAST PULSE SHOWN

Power-Saving Modes

t

CTR

Power-Up Reset

t

EOC

t

ACC

Shutdown Mode

CH0

t

REQ

t

RDL

CH1

CH2

Exiting shutdown (falling edge of SHDN) starts a con-

version in the same way as the rising edge of CONVST.

After coming out of shutdown, initiate a dummy conver-

sion and discard the results. After the dummy conver-

sion, allow the 1ms wake-up time to expire before

initiating the first accurate conversion.

The channel-shutdown feature allows analog input

channels to be powered down when they are not

selected for conversion. Powering down channels that

are not selected for conversion reduces the analog

supply current by 2.9mA per channel. To power down

channels that are not selected for conversion, pull

CHSHDN low. See the Configuration Register section

for information on selecting and deselecting channels

for conversion.

The drawback of powering down analog inputs that are

not selected for conversion is that it takes time to power

them up. Figure 10 shows how a dummy conversion is

used to power up an analog input in external clock

mode. After selecting a new channel in the configura-

tion register, initiate a dummy conversion and discard

the results. After the dummy conversion, allow the 1ms

wake-up time (t

accurate conversion.

CH3

t

RDH

WAKE

CH4

) to expire before initiating the first

CH5

Channel Shutdown ( C C H H S S H H D D N N )

t

QUIET

CH6

= 50ns

t

t

RTC

CVEOLCD

CH7