K4H561638J-HCCC000 Samsung Semiconductor, K4H561638J-HCCC000 Datasheet

K4H561638J-HCCC000

Specifications of K4H561638J-HCCC000

Related parts for K4H561638J-HCCC000

K4H561638J-HCCC000 Summary of contents

Page 1

... K4H560438J K4H560838J K4H561638J 256Mb J-die DDR SDRAM Specification 60 FBGA with Pb-Free and Halogen-Free INFORMATION IN THIS DOCUMENT IS PROVIDED IN RELATION TO SAMSUNG PRODUCTS, AND IS SUBJECT TO CHANGE WITHOUT NOTICE. NOTHING IN THIS DOCUMENT SHALL BE CONSTRUED AS GRANTING ANY LICENSE, EXPRESS OR IMPLIED, BY ESTOPPEL OR OTHERWISE, TO ANY INTELLECTUAL PROPERTY RIGHTS IN SAMSUNG PRODUCTS OR TECHNOLOGY. ALL INFORMATION IN THIS DOCUMENT IS PROVIDED ON AS " ...

Page 2

... K4H560438J K4H560838J K4H561638J Table of Contents 1.0 Key Features ...............................................................................................................................4 2.0 Ordering Information ..................................................................................................................4 3.0 Operating Frequencies ...............................................................................................................4 4.0 Ball Description (Bottom View) .................................................................................................5 5.0 Package Physical Dimension ....................................................................................................6 6.0 Block Diagram (16Mb 8Mb 4Mb x 16 I/O x4 Banks) .................................................7 7.0 Input/Output Function Description ...........................................................................................8 8.0 Command Truth Table ................................................................................................................9 9.0 General Description ..................................................................................................................10 10 ...

Page 3

... K4H560438J K4H560838J K4H561638J Revision History Revision Month Year 1.0 September 2007 - Release revision 1.0 SPEC DDR SDRAM History Rev. 1.0 September 2007 ...

Page 4

... Part No. Org. K4H560438J-HC/LCC 64M x 4 K4H560438J-HC/LB3 K4H560838J-HC/LCC 32M x 8 K4H560838J-HC/LB3 K4H561638J-HC/LCC 16M x 16 K4H561638J-HC/LB3 Note 1. "-B3"(DDR333, CL=2.5) can support "-B0"(DDR266, CL=2.5)/ "-A2"(DDR266, CL=2). 3.0 Operating Frequencies CC(DDR400@CL=3) Speed @CL2 Speed @CL2.5 166MHz Speed @CL3 200MHz ...

Page 5

... K4H560438J K4H560838J K4H561638J 4.0 Ball Description (Bottom 64M VSSQ VDDQ VSSQ 3 VSS DQ3 VDD DQ0 8 NC VSSQ VDDQ 9 VDDQ NC 32M VSSQ NC 2 DQ7 VDDQ VSSQ 3 VSS DQ6 DQ5 VDD DQ1 DQ2 8 DQ0 VSSQ VDDQ 9 VDDQ NC 16M VSSQ DQ14 DQ12 2 DQ15 VDDQ ...

Page 6

... K4H560438J K4H560838J K4H561638J 5.0 Package Physical Dimension 8.0 0 ± 0.10 #A1 TOP VIEW ENCAPSULANT AREA (Datum 0.35 ± 0. ∅ 0.45 SOLDER BALL (Post Reflow 0.50 ± 0.05) 1.10 ± 0.10 ∅0. 60Ball FBGA 256Mb Package Dimension DDR SDRAM Units : Millimeters 8.00 ± ...

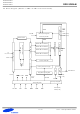

Page 7

... K4H560438J K4H560838J K4H561638J 6.0 Block Diagram (16Mb 8Mb 4Mb x 16 I/O x4 Banks) Bank Select CK, CK ADD LCKE LRAS LCBR CK, CK CKE x4/8/16 CK, CK Data Input Register Serial to parallel x8/16/32 8Mx8/ 4Mx16/ 2Mx32 8Mx8/ 4Mx16/ 2Mx32 8Mx8/ 4Mx16/ 2Mx32 8Mx8/ 4Mx16/ 2Mx32 Column Decoder Latency & ...

Page 8

... K4H560438J K4H560838J K4H561638J 7.0 Input/Output Function Description SYMBOL TYPE CK, CK Input CKE Input CS Input RAS, CAS, WE Input LDM,(UDM) Input BA0, BA1 Input 12] Input DQ I/O LDQS,(U)DQS I VDDQ Supply VSSQ Supply VDD Supply VSS Supply VREF Input Clock : CK and CK are differential clock inputs. All address and control input signals are sam- pled on the positive edge of CK and negative edge of CK ...

Page 9

... K4H560438J K4H560838J K4H561638J 8.0 Command Truth Table COMMAND Register Extended MRS Register Mode Register Set Auto Refresh Entry Refresh Self Refresh Exit Bank Active & Row Addr. Read & Auto Precharge Disable Column Address Auto Precharge Enable Write & Auto Precharge Disable ...

Page 10

... K4H560438J K4H560838J K4H561638J 16M x 4Bit x 4 Banks / 8M x 8Bit x 4 Banks / 4M x 16Bit x 4 Banks Double Data Rate SDRAM 9.0 General Description The K4H560438H / K4H560838H / K4H561638H is 268,435,456 bits of double data rate synchronous DRAM organized as 4x 16,777,216 / 4x 8,388,608 / 4x 4,194,304 words by 4/8/16bits, fabricated with SAMSUNG′s high performance CMOS technology. Syn- chronous features with Data Strobe allow extremely high performance up to 400Mb/s per pin ...

Page 11

... K4H560438J K4H560838J K4H561638J 12.0 DDR SDRAM IDD Spec Items & Test Conditions Operating current - One bank Active-Precharge; tRC=tRCmin; tCK=10ns for DDR200, tCK=7.5ns for DDR266, 6ns for DDR333, 5ns for DDR400; DQ,DM and DQS inputs changing once per clock cycle; address and control inputs changing once every two clock cycles. ...

Page 12

... K4H560438J K4H560838J K4H561638J 14.0 Detailed test condition for DDR SDRAM IDD1 & IDD7A IDD1 : Operating current: One bank operation 1. Typical Case: For DDR200,266,333: Vdd = 2.5V, T=25°C; For DDR400: Vdd=2.6V,T=25°C Worst Case : Vdd = 2.7V, T= 10°C 2. Only one bank is accessed with tRC(min), Burst Mode, Address and Control inputs on NOP edge are changing once per clock cycle ...

Page 13

... IDD3N 60 IDD4R 180 IDD4W 180 IDD5 160 Normal IDD6 Low power IDD7A 290 64Mx4 (K4H560438J) B3(DDR333@CL=2.5) 80 110 160 160 160 3 1.5 270 32Mx8 (K4H560838J) / 16Mx16 (K4H561638J 110 100 160 155 160 155 160 150 3 1.5 270 230 DDR SDRAM (V =2.7V 10°C) ...

Page 14

... K4H560438J K4H560838J K4H561638J 16.0 AC Operating Conditions Parameter/Condition Input High (Logic 1) Voltage, DQ, DQS and DM signals Input Low (Logic 0) Voltage, DQ, DQS and DM signals. Input Differential Voltage, CK and /CK inputs Input Crossing Point Voltage, CK and /CK inputs Note : 1. VID is the magnitude of the difference between the input level on CK and the input level on /CK. ...

Page 15

... K4H560438J K4H560838J K4H561638J 18.0 Overshoot/Undershoot specification for Data, Strobe and Mask Pins Parameter Maximum peak amplitude allowed for overshoot Maximum peak amplitude allowed for undershoot The area between the overshoot signal and VDD must be less than or equal to The area between the undershoot signal and GND must be less than or equal to ...

Page 16

... K4H560438J K4H560838J K4H561638J 19.0 AC Timming Parameters & Specifications Parameter Row cycle time Refresh row cycle time Row active time RAS to CAS delay Row precharge time Row active to Row active delay Write recovery time Last data in to Read command CL=2.0 Clock cycle time CL=2 ...

Page 17

... K4H560438J K4H560838J K4H561638J 20.0 System Characteristics for DDR SDRAM The following specification parameters are required in systems using DDR333, DDR266 & DDR200 devices to ensure proper system performance. these characteristics are for system simulation purposes and are guaranteed by design. Table 1 : Input Slew Rate for DQ, DQS, and DM ...

Page 18

... K4H560438J K4H560838J K4H561638J 21.0 Component Notes 1. All voltages referenced to Vss. 2. Tests for ac timing, IDD, and electrical, ac and dc characteristics, may be conducted at nominal reference/supply voltage levels, but the related specifications and device operation are guaranteed for the full voltage range specified. 3. Figure 1 represents the timing reference load used in defining the relevant timing parameters of the part not intended to be either a precise representation of the typical system environment nor a depiction of the actual load presented by a production tester ...

Page 19

... K4H560438J K4H560838J K4H561638J Component Notes 17. For CK & CK slew rate ≥ 1.0 V/ns 18. These parameters guarantee device timing, but they are not necessarily tested on each device. They may be guaranteed by device design or tester correlation. 19. Slew Rate is measured between VOH(ac) and VOL(ac). 20. Min (tCL, tCH) refers to the smaller of the actual clock low time and the actual clock high time as provided to the device (i.e. this value can be greater than the minimum specification limits for tCL and tCH) ...

Page 20

... K4H560438J K4H560838J K4H561638J 22.0 System Notes a. Pullup slew rate is characteristized under the test conditions as shown in Figure 2. b. Pulldown slew rate is measured under the test conditions shown in Figure 3. c. Pullup slew rate is measured between (VDDQ/2 - 320 mV +/- 250 mV) Pulldown slew rate is measured between (VDDQ/2 + 320 mV +/- 250 mV) Pullup and Pulldown slew rate conditions are to be met for any pattern of data, including all outputs switching and only one output switching ...

Page 21

... K4H560438J K4H560838J K4H561638J 23.0 IBIS : I/V Characteristics for Input and Output Buffers DDR SDRAM Output Driver V-I Characteristics DDR SDRAM Output driver characteristics are defined for full and half strength operation as selected by the EMRS bit A1. Figures 3 and 4 show the driver characteristics graphically, and tables 8 and 9 show the same data in tabular format suitable for input into simulation tools ...

Page 22

... K4H560438J K4H560838J K4H561638J Pulldown Current (mA) Typical Typical Voltage (V) Low High 0.1 6.0 6.8 0.2 12.2 13.5 0.3 18.1 20.1 0.4 24.1 26.6 0.5 29.8 33.0 0.6 34.6 39.1 0.7 39.4 44.2 0.8 43.7 49.8 0.9 47.5 55.2 1.0 51.3 60.3 1.1 54 ...

Page 23

... K4H560438J K4H560838J K4H561638J 0.0 Pullup Characteristics for Weak Output Driver 0.0 0 -10 -20 -30 -40 -50 -60 -70 -80 -90 Pulldown Characteristics for Weak Output Driver Figure 4. I/V characteristics for input/output buffers:Pull up(above) and pull down(below) 1.0 2.0 1.0 2 DDR SDRAM Maximum Typical High Typical Low ...

Page 24

... K4H560438J K4H560838J K4H561638J Pulldown Current (mA) Typical Typical Voltage (V) Low High 0.1 3.4 3.8 0.2 6.9 7.6 0.3 10.3 11.4 0.4 13.6 15.1 0.5 16.9 18.7 0.6 19.6 22.1 0.7 22.3 25.0 0.8 24.7 28.2 0.9 26.9 31.3 1.0 29.0 34.1 1.1 30 ...