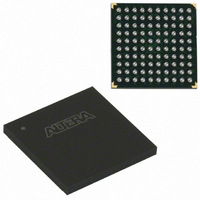

EPM570F100C4N Altera, EPM570F100C4N Datasheet

EPM570F100C4N

Specifications of EPM570F100C4N

Available stocks

Related parts for EPM570F100C4N

EPM570F100C4N Summary of contents

Page 1

... Interest Group (PCI SIG) PCI Local Bus Specification, Revision 2.2 for 3.3-V operation at 66 MHz Supports hot-socketing ■ Built-in Joint Test Action Group (JTAG) boundary-scan test (BST) circuitry ■ compliant with IEEE Std. 1149.1-1990 ■ ISP circuitry compliant with IEEE Std. 1532 © August 2009 Altera Corporation 1. Introduction MAX II Device Handbook ...

Page 2

... MAX II Logic Element to DC and Switching –6 –7 –8 — — — — — — — — — — — — © August 2009 Altera Corporation ...

Page 3

... Micro FineLine FineLine Package BGA BGA Pitch (mm) 0.5 0.5 Area (mm2 Length × width 5 × × 6 (mm × mm) © August 2009 Altera Corporation II software can automatically cross-reference ® 144-Pin 100-Pin Micro FineLine 100-Pin 144-Pin FineLine BGA TQFP TQFP BGA 80 80 — ...

Page 4

... Updated document with MAX IIZ information. Chapter 1: Introduction Referenced Documents EPM240G EPM570G EPM1270G EPM2210G EPM240Z EPM570Z (1) 1.8 V 1.5 V, 1.8 V, 2.5 V, 3.3 V external supply powers the device core directly. white paper Summary of Changes — — — — © August 2009 Altera Corporation ...

Page 5

... Updated timing numbers in Table 1-1. ■ version 1.3 December 2004, Updated timing numbers in Table 1-1. ■ version 1.2 June 2004, Updated timing numbers in Table 1-1. ■ version 1.1 © August 2009 Altera Corporation Changes Made 1–5 Summary of Changes — — — MAX II Device Handbook ...

Page 6

... MAX II Device Handbook Chapter 1: Introduction Document Revision History © August 2009 Altera Corporation ...