MC68HC000EI16 Freescale Semiconductor, MC68HC000EI16 Datasheet - Page 61

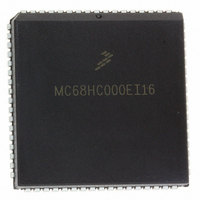

MC68HC000EI16

Manufacturer Part Number

MC68HC000EI16

Description

IC MPU 32BIT 16MHZ 68-PLCC

Manufacturer

Freescale Semiconductor

Specifications of MC68HC000EI16

Processor Type

M680x0 32-Bit

Speed

16MHz

Voltage

3.3V, 5V

Mounting Type

Surface Mount

Package / Case

68-PLCC

Family Name

M68000

Device Core

ColdFire

Device Core Size

16/32Bit

Frequency (max)

16MHz

Instruction Set Architecture

RISC

Supply Voltage 1 (typ)

5V

Operating Supply Voltage (max)

5.25V

Operating Supply Voltage (min)

4.75V

Operating Temp Range

0C to 70C

Operating Temperature Classification

Commercial

Mounting

Surface Mount

Pin Count

68

Package Type

PLCC

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Features

-

Lead Free Status / Rohs Status

Compliant

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

MC68HC000EI16

Manufacturer:

TI

Quantity:

604

Company:

Part Number:

MC68HC000EI16

Manufacturer:

FREESCALE

Quantity:

2 900

Company:

Part Number:

MC68HC000EI16

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Company:

Part Number:

MC68HC000EI16R2

Manufacturer:

FREESCAL

Quantity:

8 831

Company:

Part Number:

MC68HC000EI16R2

Manufacturer:

Freescale Semiconductor

Quantity:

10 000

Freescale Semiconductor, Inc.

bus request signal. When no acknowledge is received before the bus request signal is

negated, the processor continues the use of the bus.

5.2.2 Receiving The Bus Grant

The processor asserts BG as soon as possible. Normally, this process immediately follows

internal synchronization, except when the processor has made an internal decision to

execute the next bus cycle but has not yet asserted AS for that cycle. In this case, BG is

delayed until AS is asserted to indicate to external devices that a bus cycle is in progress.

BG can be routed through a daisy-chained network or through a specific priority-encoded

network. Any method of external arbitration that observes the protocol can be used.

5.2.3 Acknowledgment Of Mastership (3-Wire Bus Arbitration Only)

Upon receiving BG, the requesting device waits until AS, DTACK, and BGACK are negated

before asserting BGACK. The negation of AS indicates that the previous bus master has

completed its cycle. (No device is allowed to assume bus mastership while AS is

asserted.) The negation of BGACK indicates that the previous master has released the

bus. The negation of DTACK indicates that the previous slave has terminated the

connection to the previous master. (In some applications, DTACK might not be included in

this function; general-purpose devices would be connected using AS only.) When BGACK

is asserted, the asserting device is bus master until it negates BGACK. BGACK should not

be negated until after the bus cycle(s) is complete. A device relinquishes control of the bus

by negating BGACK.

The bus request from the granted device should be negated after BGACK is asserted. If

another bus request is pending, BG is reasserted within a few clocks, as described in 5.3

Bus Arbitration Control. The processor does not perform any external bus cycles before

reasserting BG.

5.3 BUS ARBITRATION CONTROL

All asynchronous bus arbitration signals to the processor are synchronized before being

used internally. As shown in Figure 5-17, synchronization requires a maximum of one

cycle of the system clock, assuming that the asynchronous input setup time (#47, defined

in Section 10 Electrical Characteristic) has been met. The input asynchronous signal is

sampled on the falling edge of the clock and is valid internally after the next falling edge.

MOTOROLA

M68000 8-/16-/32-BIT MICROPROCESSORS USER'S MANUAL

5- 15

For More Information On This Product,

Go to: www.freescale.com