CS42448-DQZ Cirrus Logic Inc, CS42448-DQZ Datasheet

CS42448-DQZ

Specifications of CS42448-DQZ

Available stocks

Related parts for CS42448-DQZ

CS42448-DQZ Summary of contents

Page 1

... An auxiliary serial input is available for an additional two channels of PCM data. The CS42448 is available in a 64-pin LQFP package in Commercial (-10°C to +70°C) and Automotive (-40°C to +105°C) grades. The CDB42448 Customer Demonstra- tion board is also available for device evaluation and implementation suggestions. Please refer to Information” ...

Page 2

... TDM ....................................................................................................................................... 33 4.5.7 I/O Channel Allocation ........................................................................................................... 34 4.6 AUX Port Digital Interface Formats ................................................................................................ 34 4.6.1 I²S .......................................................................................................................................... 34 4.6.2 Left-Justified .......................................................................................................................... 35 4.7 Control Port Description and Timing ............................................................................................... 35 4.7.1 SPI Mode ............................................................................................................................... 35 4.7.2 I²C Mode ................................................................................................................................ 36 4.8 Interrupts ........................................................................................................................................ 37 4.9 Recommended Power-Up Sequence ............................................................................................. 38 4.10 Reset and Power-Up .................................................................................................................... 38 2 ...................................................................................................................... 6 CS42448 DS648F3 ...

Page 3

... Status Control (Address 18h) ....................................................................................................... 51 6.13.1 Interrupt Pin Control (INT[1:0]) ............................................................................................ 51 6.14 Status (Address 19h) (Read Only) ............................................................................................... 51 6.14.1 DAC CLOCK ERROR (DAC_CLK ERROR) ....................................................................... 51 6.14.2 ADC CLOCK ERROR (ADC_CLK ERROR) ....................................................................... 51 6.14.3 ADC Overflow (ADCX_OVFL) ............................................................................................. 51 6.15 Status Mask (Address 1Ah) .......................................................................................................... 52 6.16 MUTEC Pin Control (Address 1Bh) .............................................................................................. 52 DS648F3 .......................................................................... 49 CS42448 3 ...

Page 4

... Figure 28.Passive Input Filter ................................................................................................................... 54 Figure 29.Passive Input Filter w/Attenuation ............................................................................................. 55 Figure 30.Active Analog Output Filter ....................................................................................................... 56 Figure 31.Passive Analog Output Filter .................................................................................................... 56 Figure 32.SSM Stopband Rejection .......................................................................................................... 57 Figure 33.SSM Transition Band ................................................................................................................ 57 Figure 34.SSM Transition Band (Detail) ................................................................................................... 57 Figure 35.SSM Passband Ripple .............................................................................................................. 57 Figure 36.DSM Stopband Rejection .......................................................................................................... 57 4 CS42448 DS648F3 ...

Page 5

... Table 10. MCLK Frequency Settings for I²S, Left and Right Justified Interface Formats .......................... 43 Table 12. DAC Digital Interface Formats .................................................................................................. 44 Table 11. MCLK Frequency Settings for TDM & OLM Interface Formats ................................................. 44 Table 13. ADC Digital Interface Formats .................................................................................................. 45 Table 14. Example AOUT Volume Settings .............................................................................................. 49 Table 15. Example AIN Volume Settings .................................................................................................. 50 DS648F3 CS42448 5 ...

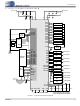

Page 6

... Master Clock (Input) - Clock source for the delta-sigma modulators and digital filters. ADC_SDOUT1 13 ADC_SDOUT2 12 Serial Audio Data Output (Output) - Outputs for two’s complement serial audio data. ADC_SDOUT3 CS42448 Pin Description 8. “Digital I/O Pin Characteristics” on page CS42448 48 AIN2+ 47 AIN2- 46 AIN1+ 45 AIN1 AGND 41 AOUT8- 40 AOUT8+ 39 AOUT7+ 38 AOUT7- 37 AOUT6- 36 AOUT6+ 35 MUTEC 34 AOUT5+ ...

Page 7

... Serial Control Port Clock (Input) - Serial clock for the control port interface. SDA/CDOUT 64 Serial Control Data I/O (Input/Output) - Input/Output for I²C data. Output for SPI data. DS648F3 8. for details). The unused leg of each input is internally connected to common CS42448 “Digital I/O Pin Charac- Sec- 7 ...

Page 8

... Digital I/O Pin Characteristics Various pins on the CS42448 are powered from separate power supply rails. The logic level for each input should adhere to the corresponding power rail and should not exceed the maximum ratings. Power Pin Name I/O Rail VLC ...

Page 9

... VLC 0.1 µF VQ FILT+_ADC FILT+_DAC AGND DGND DGND AGND DGND Connect DGND and AGND near CODEC Figure 1. Typical Connection Diagram CS42448 +3 0.01 µF 0.1 µ µF 0.01 µF 0.1 µ Analog Output Filter Analog Output Filter Analog Output Filter 29 31 ...

Page 10

... Symbol Analog VA Digital VD Serial Port Interface VLS Control Port Interface VLC (Note (Note Serial Port Interface V IND-S Control Port Interface V IND stg CS42448 Min Max Units 3.14 5.25 V 3.14 5.25 V 1.71 5.25 V 1.71 5.25 V °C -10 +70 °C -40 +105 Min Max Units -0 ...

Page 11

... VD = VLS = VLC = 3.3 V±5 V±5%; Full- A Figure 26 on page 53 Differential Min Typ Max 99 105 - 96 102 - - -98 -92 - - ±100 - 1.06*VA 1.12*VA 1.18*VA 0.53*VA 0.56*VA 0.59* CS42448 and Figure 27 on page 53; Mea- Single-Ended Min Typ Max Unit 96 102 - - ±100 - ppm/°C Vpp kΩ ...

Page 12

... VD = VLS = VLC = 3.3 V±5 V±5%; Full- A Figure 26 on page 53 Differential Min Typ Max 97 105 - 94 102 - - -98 -90 - - ±100 - 1.04*VA 1.12*VA 1.20*VA 0.52*VA 0.56*VA 0.60* CS42448 and Figure 27 on page 53; Mea- Single-Ended Min Typ Max Unit 94 102 - - ±100 - ppm/°C Vpp kΩ ...

Page 13

... Filter response is guaranteed by design. 10. Response is clock-dependent and will scale with Fs. Note that the response plots been normalized to Fs and can be de-normalized by multiplying the X-axis scale by Fs. DS648F3 (Notes 9, 10) to -0.1 dB corner to -0.1 dB corner to -0.1 dB corner CS42448 Min Typ Max Unit 0 - 0.4896 ...

Page 14

... Min Typ Max 102 108 - 99 105 - - -98 - -36 - 100 - 1.235•VA 1.300•VA 1.365•VA 0.618•VA 0.650•VA 0.683•VA - 0.1 0.25 - ±100 - - 100 - - - 100 CS42448 and active filter in Figure 32 Single-Ended Min Typ Max Unit 99 105 - dB 96 102 - - 100 - dB Vpp - 0.1 ...

Page 15

... Figure 2. R and C reflect the recommended minimum resistance and L L for a recommended output filter. CS42448 Figure 32 on page 57; Measurement Single-Ended Min Typ Max Unit 97 105 - dB 94 102 - -95 ...

Page 16

... DAC1-4 3.3 µF + AOUTxx R L AGND Figure 2. Output Test Circuit for Maximum Load 16 125 100 75 Analog Output 2 Figure 3. Maximum Loading CS42448 Safe Operating Region Ω ) Resistive Load -- R L DS648F3 ...

Page 17

... Quad-Speed Mode Measurement Bandwidth is from Stopband to 1.34 Fs. 16. De-emphasis is only available in Single-Speed Mode. DS648F3 (Notes 9, 14) to -0.05 dB corner corner (Note 15 kHz Fs = 44.1 kHz kHz to -0.1 dB corner corner (Note 15) to -0.1 dB corner corner (Note 15) CS42448 Min Typ Max 0 - 0.4780 0 - 0.4996 -0.2 - +0.08 0.5465 - - ...

Page 18

... Quad-Speed Mode (Note 20 sckh t sckl t fss t lcks t fsh t dpd dh1 t dh2 t dval All Speed Modes F t lcks t dpd t t dh1 LRCK (input) t sckl SCLK (input) MSB-1 DAC_SDIN1 MSB-1 ADC_SDOUT1 Figure 5. TDM Serial Audio Interface Timing CS42448 Min Max - 1 0.512 100 s 100 200 ...

Page 19

... Notes: 17. After powering up the CS42448, RST should be held low after the power supplies and clocks are settled. 18. See Table 10 on page 43 19. When operating in TDM interface format, VLS is limited to nominal 2 5.0 V operation only. 20. ADC - I²S, Left-Justified, Right-Justified interface formats only. DAC - I²S, Left-Justified, Right-Justified and Time Division Multiplexed interface formats only. 21. “ ...

Page 20

... AUX_SDIN Setup Time Before SCLK Rising Edge AUX_SDIN Hold Time After SCLK Rising Edge AUX_LRCK AUX_SCLK AUX_SDIN 20 Symbol All Speed Modes lcks lcks sckh MSB Figure 7. Serial Audio Interface Timing CS42448 Min Max - ADC_LRCK · ADC_LRCK sckl MSB-1 DS648F3 Units kHz kHz % ns ...

Page 21

... Figure 8. Control Port Timing - I²C Format CS42448 = 30 pF. L Min Max Unit - 100 kHz 500 - ns 4.7 - µs 4.0 - µs 4.7 - µs 4.0 - µs 4.7 - µ µ ...

Page 22

... CS t css CCLK CDIN CDOUT 22 Symbol f sck t srs t css t csh t scl t sch t dsu (Note 24 (Note 25 (Note 25 sch scl dsu MSB t pd MSB Figure 9. Control Port Timing - SPI Format CS42448 Min Max 100 - 100 f2 t csh pF. L Units MHz ns ns μ ...

Page 23

... Hz All Supplies = Symbol Serial Port VLS-1.0 Control Port V VLC-1.0 OH MUTEC Serial Port V Control Port OL MUTEC Serial Port 0.7xVLS Control Port V 0.7xVLC IH Serial Port Control Port for serial and control port power rails. CS42448 Min Typ Max Units - 60 600 850 1.25 - ...

Page 24

... In the One-Line Mode (OLM) interface format, the CS42448 will allow ADC channels on one data line and DAC channels on 2 data lines. The CS42448 features an Auxiliary Port used to accommodate an additional two channels of PCM data on the ADC_SDOUT data line in the TDM digital interface format. See for details ...

Page 25

... DS648F3 50. Full-Scale Differential Input Level = (AINx+) - (AINx RMS Figure 10. Full-Scale Input AIN5_MUX Differential Input Filter 57 VQ AIN6_MUX Differential Input Filter 59 VQ Figure 11. ADC3 Input Topology CS42448 “AINX Volume to be set to a ‘1’. 5 AINx+ AINx- ADC3 ADC3 SINGLE AIN5 - AIN6 - ...

Page 26

... DC offset will continue to be subtracted from the conversion re- sult. This feature makes it possible to perform a system DC offset calibration by: 1. Running the CS42448 with the high-pass filter enabled until the filter settles. See the Digital Filter Characteristics for filter settling time. ...

Page 27

... No Valid MCLK Applied? Yes RST = Low VA/2. 2. Aout bias = VQ. ERROR: Power removed 3. Audio signal generated per register settings. ERROR: MCLK/LRCK ratio change CS42448 Power-Down Mode Yes 2. Aout bias = VQ. PDN bit = '1' audio signal generated. 4. Control Port Registers retain settings. No ® ...

Page 28

... MUTEC is in high-impedance mode during power up or when the CS42448 enters Power-Down Mode by setting the PDN bit in the register Down Mode, the pin can be controlled by the user via the control port (see 1Bh)” ...

Page 29

... Volume Control register. The attenuation is ramped up and down at the rate specified by the SZC[1:0] bits. 4.3.7 De-Emphasis Filter The CS42448 includes on-chip digital de-emphasis optimized for a sample rate of 44.1 kHz. The filter re- sponse is shown in Figure that utilize 50/15 μs pre-emphasis equalization as a means of noise reduction. ...

Page 30

... MCLK (MHz) 192x 256x 12.2880 16.3840 16.9344 22.5792 18.4320 24.5760 MCLK (MHz) 96x 128x 16.9344 22.5792 18.4320 24.5760 CS42448 “DAC De-Emphasis Control µs Frequency “DAC Functional for setting up Tables 2 “MCLK Frequency 768x 1024x 24.5760 32.7680 33.8688 45.1584 36.8640 49.1520 384x 512x 24 ...

Page 31

... Table 7. OLM#2 Clock Ratios TDM SSM DSM 256x, 384x, 512x, 256x, 384x, 512x 768x, 1024x 256X 256X N/A N/A Table 8. TDM Clock Ratios CS42448 Figures 15-19. Data is Table 5 for Tables 5 through 8. QSM 64x, 96x, 128x, 192x, 256x 32x, 48x, 64x 64x ...

Page 32

... Left Channel LSB MSB LSB MSB AOUT3 AOUT5 AOUT2 20 clks 20 clks 20 clks AOUT8 20 clks AIN3 - AIN2 20 clks 20 clks 20 clks Figure 18. One-Line Mode #1 Format CS42448 Rig AOUT AIN Rig MSB AOUT AIN AOUT AIN clks Right Channel LSB MSB LSB MSB ...

Page 33

... AOUT5 32 clks 32 clks 32 clks LSB MSB LSB MSB LSB MSB AIN2 AIN3 AIN4 AIN5 32 clks 32 clks 32 clks Figure 20. TDM Format CS42448 128 clks Right Channel LSB MSB LSB MSB LSB MSB AOUT4 AOUT6 24 clks 24 clks AIN4 AIN6 24 clks 24 clks LSB MSB ...

Page 34

... AIN 1,2 AIN 1,2,3,4,5,6 AIN 1,2,3,4,5,6; (2 additional channels from AUX_SDIN) AIN 3,4 Not Used Not Used AIN 5,6 Not Used Not Used Table 9. Serial Audio Interface Channel Allocations Figure 21. AUX I²S Format CS42448 from/to Digital I/O “Interface Formats (Address AUX2 DS648F3 MSB ...

Page 35

... The control port has two modes: SPI and I²C, with the CS42448 acting as a slave device. SPI Mode is se- lected if there is a high-to-low transition on the AD0/CS pin, after the RST pin has been brought high. I²C Mode is selected by connecting the AD0/CS pin through a resistor to VLC or DGND, thereby permanently selecting the desired AD0 bit address state ...

Page 36

... CS42448 after a Start condition consists of a 7-bit chip address field and a R/W bit (high for a read, low for a write). The upper 5 bits of the 7-bit address field are fixed at 10010. To communicate with a CS42448, the chip address field, which is the first byte sent to the CS42448, should match 10010 followed by the settings of the AD1 and AD0 ...

Page 37

... Interrupts The CS42448 has a comprehensive interrupt capability. The INT output pin is intended to drive the interrupt input pin on the host microcontroller. The INT pin may be configured as an active low or active high CMOS driver or an open-drain driver. This last mode is used for active low, wired-OR hook-ups, with multiple pe- ripherals connected to the microcontroller interrupt input pin ...

Page 38

... The low value ceramic capacitor should be closest to the pin and should be mounted on the same side of the board as the CS42448 to minimize inductance effects. All signals, especially clocks, should be kept away from the ADC/DAC_FILT+, VQ pins in order to avoid unwanted coupling into the modulators. ...

Page 39

... AOUT6 AOUT6 AOUT6 VOL6 VOL5 VOL4 AOUT7 AOUT7 AOUT7 VOL6 VOL5 VOL4 AOUT8 AOUT8 AOUT8 VOL6 VOL5 VOL4 INV_AOUT6 INV_AOUT5 INV_AOUT4 INV_AOUT3 INV_AOUT2 INV_AOUT1 CS42448 Rev_ID3 Rev_ID2 Rev_ID1 PDN_DAC2 PDN_DAC1 MFREQ2 MFREQ1 MFREQ0 DAC_DIF0 ADC_DIF2 ADC_DIF1 ADC2 ADC3 AIN5_MUX SINGLE SINGLE ...

Page 40

... VOL5 VOL4 INV_A6 INV_A5 Reserved Reserved Reserved DAC_CLK ADC_CLK Error Reserved DAC_CLK ADC_CLK Error_M Reserved Reserved Reserved CS42448 AIN1 AIN1 AIN1 VOL3 VOL2 VOL1 AIN2 AIN2 AIN2 VOL3 VOL2 VOL1 AIN3 AIN3 AIN3 VOL3 VOL2 VOL1 AIN4 AIN4 AIN4 VOL3 VOL2 ...

Page 41

... Chip I.D. and Revision Register (Address 01h) (Read Only Chip_ID3 Chip_ID2 Chip_ID1 6.2.1 Chip I.D. (CHIP_ID[3:0]) Default = 0000 Function: I.D. code for the CS42448. Permanently set to 0000. 6.2.2 Chip Revision (REV_ID[3:0]) Default = 0001 Function: CS42448 revision level. Revision A is coded as 0001. DS648F3 ...

Page 42

... DACs are muted or the power down bit (PDN) is enabled to eliminate the possibility of audible artifacts. 6.3.3 Power Down (PDN) Default = Disable 1 - Enable Function: The entire device will enter a low-power state when this function is enabled. The contents of the control registers are retained in this mode PDN_DAC4 PDN_DAC3 CS42448 PDN_DAC2 PDN_DAC1 PDN DS648F3 ...

Page 43

... Table 10. MCLK Frequency Settings for I²S, Left and Right Justified Interface Formats DS648F3 MFreq2 ADC_FM0 MFreq0 Description 0 1.0290 MHz to 12.8000 MHz 1 1.5360 MHz to 19.2000 MHz 0 2.0480 MHz to 25.6000 MHz 1 3.0720 MHz to 38.4000 MHz X 4.0960 MHz to 51.2000 MHz CS42448 MFreq1 MFreq0 Reserved Ratio (xFs) SSM DSM QSM 256 128 64 384 192 96 512 256 ...

Page 44

... MHz to 51.2000 MHz DAC_DIF1 DAC_DIF0 DAC_DIF0 Description 0 Left Justified 24-bit data 1 I² 24-bit data 0 Right Justified, 24-bit data Table 12. DAC Digital Interface Formats CS42448 Ratio (xFs) SSM DSM QSM 256 N/A N/A 384 N/A N/A 512 256 N/A 768 ...

Page 45

... Right Justified, 24-bit data 1 Right Justified, 16-bit data 0 One-Line #1, 20-bit 1 One-Line #2, 24-bit 0 TDM Mode, 24-bit (slave only) 1 Reserved Table 13. ADC Digital Interface Formats ADC1 ADC2 SINGLE SINGLE 13. CS42448 Format Figure 3 Figure 17 4 Figure 18 5 Figure 19 6 Figure 31. Refer to Table 9, “Serial Audio Format Figure 0 Figure 16 1 ...

Page 46

... When enabled, this bit allows the user to apply a single-ended input to the positive terminal of ADC2 digital gain is automatically applied to the serial audio data of ADC2. The negative leg must be driv the common mode of the ADC. See 46 “ADC Digital Filter Characteris- Figure 27 on page 53 for a graphical description. Figure 27 on page 53 for a graphical description. CS42448 DS648F3 ...

Page 47

... AOUT1 and AIN1 Volume Control register and the other Volume Control registers are ignored. DS648F3 Figure 13 on page 29 Figure 13 on page 29 Figure 13 on page AMUTE MUTE ADC_SP CS42448 and Figure 27 on page 53 for graphical for a graphical description. for a graphical description ADC_SNGVOL ...

Page 48

... Enabled Function: The Digital-to-Analog converters of the CS42448 will mute the output following the reception of 8192 con- secutive audio samples of static 0 or -1. A single sample of non-static data will release the mute. Detection and muting is done independently for each channel. The quiescent voltage on the output will be retained and the MUTEC pin will go active during the mute period ...

Page 49

... Enabled Function: The respective Digital-to-Analog converter outputs of the CS42448 will mute when enabled. The quies- cent voltage on the outputs will be retained. The muting function is affected by the DAC Soft and Zero Cross bits (DAC_SZC[1:0]). When all channels are muted, the MUTEC pin will become active. ...

Page 50

... Table 15. Example AIN Volume Settings INV_AIN5 INV_AIN4 CS42448 INV_AOUT3 INV_AOUT2 INV_AOUT1 AINx_VOL2 AINx_VOL1 AINx_VOL0 Table INV_AIN3 INV_AIN2 ...

Page 51

... Indicates an invalid MCLK to ADC_LRCK ratio. This status flag is set to “Level Active Mode” and becomes active during the error condition. See 6.14.3 ADC Overflow (ADCX_OVFL) Default = x Function: Indicates that there is an over-range condition anywhere in the CS42448 ADC signal path of each of the associated ADC’s. These status flags become active on the arrival of the error condition. DS648F3 5 4 ...

Page 52

... MUTEC pin is not active MUTEC pin is active. Function: The MUTEC pin will go high or low (depending on the MUTEC Polarity Select bit) when this bit is enabled DAC_CLK ADC_CLK ADC3_OVFL_M Error_M Error_M Reserved Reserved CS42448 ADC2_OVFL_M ADC1_OVFL_M “Status (Address 19h Reserved MCPolarity MUTEC ACTIVE DS648F3 ...

Page 53

... VA 470 pF C0G 100 kΩ 91 Ω - 4.7 μF + 2700 pF 100 kΩ Figure 27. Single-Ended Active Input Filter CS42448 Figures 26 and 29 for low-cost, low-component- ADC1-3 AINx+ 2700 pF C0G AINx- ADC1-2 AIN1+,2+,3+,4+ C0G AIN1-,2-,3-,4- ADC3 AIN5A,6A ...

Page 54

... C0G 4.7 μF 10 μF 150 Ω 2700 pF C0G 10 μF 150 Ω 2700 pF C0G Figure 28. Passive Input Filter CS42448 ADC1-2 AIN1+,2+,3+,4+ AIN1-,2-,3-,4- ADC3 AIN5A,6A AIN5B,6B Figure 29, the input DS648F3 ...

Page 55

... Figure 29. Passive Input Filter w/Attenuation DS648F3 ADC1-2 10 μF 2.5 kΩ AIN1+,2+,3+,4+ Ω 2700 pF 2.5 k C0G AIN1-,2-,3-,4- 4.7 μF ADC3 10 μF 2.5 kΩ AIN5A,6A Ω 2700 pF 2.5 k C0G 10 μF 2.5 kΩ AIN5B,6B Ω 2700 pF 2.5 k C0G CS42448 55 ...

Page 56

... C0G 22 μF 1.87 kΩ C0G Figure 30. Active Analog Output Filter 560 Ω 3.3 µ kΩ Figure 31. Passive Analog Output Filter CS42448 22 μF 562Ω 47.5 k Ω ext R + 560 ext πF R 560 S ext DS648F3 ...

Page 57

... Figure 37. DSM Transition Band CS42448 0.1 0.15 0.2 0.25 0.3 0.35 0.4 0.45 Frequency (normalized to Fs) 0.44 0.46 0.48 0.50 0.52 0.54 0.56 0.58 0.60 Frequency (normalized to Fs) ...

Page 58

... CS42448 . que ncy (norm alize Figure 39. DSM Passband Ripple 0 0.20 0.25 0.30 0.35 0.40 0.45 0.50 0.55 0.60 0.65 0.70 0.75 0.80 0.85 Fre que ncy (norm alize Figure 41. QSM Transition Band 0 .13 0 . que ncy (norm alize Figure 43 ...

Page 59

... Figure 46. SSM Transition Band (detail) Figure 48. DSM Stopband Rejection DS648F3 Figure 45. SSM Transition Band 0.05 0 -0.05 -0. 1 -0.15 -0. 2 -0.25 0 0.05 0.1 0.15 0.2 0.25 0.3 0.35 Frequency (normalized to Fs) Figure 47. SSM Passband Ripple Figure 49. DSM Transition Band CS42448 0.4 0.45 0.5 59 ...

Page 60

... Figure 53. QSM Transition Band 0 - -1. 5 0.6 0.65 0.7 0 Figure 55. QSM Passband Ripple CS42448 0.05 0.1 0.15 0.2 0.25 0.3 0.35 0.4 0.45 Frequency (normalized to Fs) 0.4 0.45 0.5 0.55 0.6 0.65 0.7 Frequency(normalized to Fs) 0.05 ...

Page 61

... The deviation from the nominal full-scale analog output for a full-scale digital input. Gain Drift The change in gain value with temperature. Units in ppm/°C. Offset Error The deviation of the mid-scale transition (111...111 to 000...000) from the ideal. Units in mV. DS648F3 CS42448 61 ...

Page 62

... Harris. Presented at the 93rd Convention of the Audio Engineering Society, October 1992. 7. Cirrus Logic, A Fifth-Order Delta-Sigma Modulator with 110 dB Audio Dynamic Range Fujimori, K. Ha- mashita and E.J. Swanson. Paper presented at the 93rd Convention of the Audio Engineering Society, Oc- tober 1992. 8. Philips Semiconductor, The I²C-Bus Specification: Version 2.1, January 2000. http://www.semiconductors.philips.com 62 CS42448 DS648F3 ...

Page 63

... BSC 0.398 0.020 BSC 0.024 0.024 0.030 4° 7.000° * Nominal pin pitch is 0.50 mm Controlling dimension is mm. JEDEC Designation: MS026 Symbol 2 Layer Board q θ 4 Layer Board CS42448 A A1 MILLIMETERS MIN NOM MAX --- 1.40 1.60 0.05 0.10 0.15 0.17 0.20 0.27 11 ...

Page 64

... Connection Diagram” on page 9 and “Analog Input Characteristics (Automotive)” on page www.cirrus.com. CS42448 Temp Range Container Order # Rail CS42448-CQZ Tape & Reel CS42448-CQZR Rail CS42448-DQZ Tape & Reel CS42448-DQZR - - CDB42448 and cor- Pin Descriptions table on page 6. “Analog Input Characteris- 12. DS648F3 10. ...