74LVC00AD Philips Semiconductors, 74LVC00AD Datasheet

74LVC00AD

Specifications of 74LVC00AD

Available stocks

Related parts for 74LVC00AD

74LVC00AD Summary of contents

Page 1

... Philips Semiconductors Quad 2-input NAND gate FEATURES 5 V tolerant inputs for interfacing with 5 V logic Wide supply voltage range from 1.2 to 3.6 V CMOS low power consumption Direct interface with TTL levels Inputs accept voltages up to 5.5 V Complies with JEDEC standard no. 8-1A ...

Page 2

... Philips Semiconductors Quad 2-input NAND gate ORDERING INFORMATION TYPE NUMBER TEMPERATURE RANGE 74LVC00AD 40 to +125 C 74LVC00ADB 40 to +125 C 74LVC00APW 40 to +125 C 74LVC00ABQ 40 to +125 C PINNING PIN SYMBOL GND PACKAGE PINS PACKAGE 14 SO14 14 SSOP14 14 TSSOP14 14 DHVQFN14 DESCRIPTION data input data input data output ...

Page 3

... Philips Semiconductors Quad 2-input NAND gate handbook, halfpage A B Fig.5 Logic diagram (one gate). RECOMMENDED OPERATING CONDITIONS SYMBOL PARAMETER V supply voltage CC V input voltage I V output voltage O T operating ambient temperature amb input rise and fall times r f LIMITING VALUES In accordance with the Absolute Maximum Rating System (IEC 60134); voltages are referenced to GND (ground = 0 V). ...

Page 4

... Philips Semiconductors Quad 2-input NAND gate DC CHARACTERISTICS At recommended operating conditions; voltages are referenced to GND (ground = 0 V). SYMBOL PARAMETER +85 C amb V HIGH-level input voltage IH V LOW-level input voltage IL V HIGH-level output voltage OH V LOW-level output voltage OL I input leakage current LI I quiescent supply current ...

Page 5

... Philips Semiconductors Quad 2-input NAND gate SYMBOL PARAMETER +125 C amb V HIGH-level input voltage IH V LOW-level input voltage IL V HIGH-level output voltage OH V LOW-level output voltage OL I input leakage current LI I quiescent supply current CC I additional quiescent supply CC current per input pin Note 1 ...

Page 6

... Philips Semiconductors Quad 2-input NAND gate AC CHARACTERISTICS GND = 2.5 ns SYMBOL PARAMETER +85 C amb t /t propagation delay PHL PLH nA skew sk( +125 C amb t /t propagation delay PHL PLH nA skew sk(0) Notes 1. Typical value is measured Skew between any two outputs of the same package switching in the same direction. This parameter is guaranteed by design ...

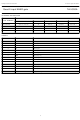

Page 7

... Philips Semiconductors Quad 2-input NAND gate PACKAGE OUTLINES SO14: plastic small outline package; 14 leads; body width 3 pin 1 index 1 e DIMENSIONS (inch dimensions are derived from the original mm dimensions) A UNIT max. 0.25 1.45 mm 1.75 0.25 0.10 1.25 0.010 0.057 inches 0.01 0.069 ...