SC16C752IB48,151 NXP Semiconductors, SC16C752IB48,151 Datasheet

SC16C752IB48,151

Specifications of SC16C752IB48,151

935270055151

SC16C752IB48-S

Available stocks

Related parts for SC16C752IB48,151

SC16C752IB48,151 Summary of contents

Page 1

SC16C752 Dual UART with 64-byte FIFO Rev. 04 — 20 June 2003 1. Description The SC16C752 is a dual universal asynchronous receiver/transmitter (UART) with 64-byte FIFOs, automatic hardware/software flow control, and data rates Mbits/s (3.3 V and ...

Page 2

Philips Semiconductors Fast databus access time Programmable sleep mode Programmable serial interface characteristics False start bit detection Complete status reporting capabilities in both normal and sleep mode Line break generation and detection Internal test and loop-back capabilities Fully prioritized interrupt ...

Page 3

Philips Semiconductors 4. Block diagram SC16C752 D0–D7 DATA BUS IOR AND IOW CONTROL LOGIC RESET A0–A2 REGISTER CSA SELECT CSB LOGIC INTA, INTB INTERRUPT TXRDYA, TXRDYB CONTROL RXRDYA, RXRDYB LOGIC Fig 1. Block diagram. 9397 750 11635 Product data TRANSMIT ...

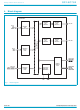

Page 4

Philips Semiconductors 5. Pinning information 5.1 Pinning Fig 2. Pin configuration. 5.2 Pin description Table 2: Pin description Symbol Pin Type CDA, CDB 40 CSA, CSB 10 ...

Page 5

Philips Semiconductors Table 2: Pin description …continued Symbol Pin Type CTSA, CTSB 38 D0-D4, 44-48, I/O D5-D7 1-3 DSRA, DSRB 39 DTRA, DTRB 34 GND 17 I INTA, INTB 30 IOR 19 ...

Page 6

Philips Semiconductors Table 2: Pin description …continued Symbol Pin Type RTSA, RTSB 33 RXA, RXB RXRDYA, 31 RXRDYB TXA, TXB TXRDYA, 43 TXRDYB XTAL1 ...

Page 7

Philips Semiconductors The SC16C752 has selectable hardware flow control and software flow control. Hardware flow control significantly reduces software overhead and increases system efficiency by automatically controlling serial data flow using the RTS output and CTS input signals. Software flow ...

Page 8

Philips Semiconductors 6.2.1 Auto-RTS Auto-RTS data flow control originates in the receiver block (see diagram.” on page trigger levels used in Auto-RTS are stored in the TCR. RTS is active if the RX FIFO level is below the halt trigger ...

Page 9

Philips Semiconductors 6.3 Software flow control Software flow control is enabled through the enhanced feature register and the modem control register. Different combinations of software flow control can be enabled by setting different combinations of EFR[3:0]. control options. Table 3: ...

Page 10

Philips Semiconductors 6.3.2 TX Xoff1/2 character is transmitted when the RX FIFO has passed the HALT trigger level programmed in TCR[3:0]. Xon1/2 character is transmitted when the RX FIFO reaches the RESUME trigger level programmed in TCR[7:4]. The transmission of ...

Page 11

Philips Semiconductors 60 characters have been sent. At this time, UART2 will transmit UART1, informing UART1 to halt transmission. UART1 will likely send the 61 UART2 is sending the Xoff character. Now UART2 is serviced and the ...

Page 12

Philips Semiconductors 6.5 Interrupts The SC16C752 has interrupt generation and prioritization (six prioritized levels of interrupts) capability. The interrupt enable register (IER) enables each of the six types of interrupts and the INT signal in response to an interrupt generation. ...

Page 13

Philips Semiconductors 6.5.1 Interrupt mode operation In interrupt mode (if any bit of IER[3: the processor is informed of the status of the receiver and transmitter by an interrupt signal, INT. Therefore not necessary to continuously ...

Page 14

Philips Semiconductors 6.6 DMA operation There are two modes of DMA operation, DMA mode 0 or DMA mode 1, selected by FCR[3]. In DMA mode 0 or FIFO disable (FCR[ DMA occurs in single character transfers. In DMA ...

Page 15

Philips Semiconductors 6.6.2 Block DMA transfers (DMA mode 1) Figure 10 wrptr TRIGGER LEVEL wrptr Fig 10. TXRDY and RXRDY in DMA mode 1. Transmitter: available. It becomes inactive when the FIFO is full. Receiver: a time-out interrupt occurs. It ...

Page 16

Philips Semiconductors 6.8 Break and time-out conditions An RX idle condition is detected when the receiver line, RX, has been HIGH for 4 character time. The receiver line is sampled midway through each bit. When a break condition occurs, the ...

Page 17

Philips Semiconductors Table 7: Desired baud rate 50 75 110 134.5 150 300 600 1200 1800 2000 2400 3600 4800 7200 9600 19200 38400 56000 Table 8: Desired baud rate 50 75 110 134.5 150 300 600 1200 1800 2000 ...

Page 18

Philips Semiconductors Fig 12. Crystal oscillator connections. 7. Register descriptions Each register is selected using address lines A0, A1, A2, and in some cases, bits from other registers. The programming combinations for register selection are shown in Table Table 9: ...

Page 19

Philips Semiconductors Table 10 Table 10: SC16C752 internal registers Shaded bits are only accessible when EFR[4] is set Register Bit 7 Bit 6 [1] General Register Set RHR bit 7 bit ...

Page 20

Philips Semiconductors [3] The Special Register set is accessible only when LCR[7] is set to a logic 1. [4] Enhanced Feature Register; Xon-1,2 and Xoff-1,2 are accessible only when LCR is set to ‘BF Remark: Refer to the notes under ...

Page 21

Philips Semiconductors 7.3 FIFO control register (FCR) This is a write-only register that is used for enabling the FIFOs, clearing the FIFOs, setting transmitter and receiver trigger levels, and selecting the type of DMA signalling. Table 11: Bit 7-6 5-4 ...

Page 22

Philips Semiconductors 7.4 Line control register (LCR) This register controls the data communication format. The word length, number of stop bits, and parity type are selected by writing the appropriate bits to the LCR. Table 12 Table 12: Bit 7 ...

Page 23

Philips Semiconductors 7.5 Line status register (LSR) Table 13 Table 13: Bit When the LSR is read, LSR[4:2] reflect the error bits (BI, FE, PE) of the character at the top of ...

Page 24

Philips Semiconductors Remark: The three error bits (parity, framing, break) may not be updated correctly in the first read of the LSR when the input clock (XTAL1) is running faster than 36 MHz. However, the second read is always correct. ...

Page 25

Philips Semiconductors 7.7 Modem status register (MSR) This 8-bit register provides information about the current state of the control lines from the mode, data set, or peripheral device to the processor. It also indicates when a control input from the ...

Page 26

Philips Semiconductors Table 16: Bit [1] IER[7:4] can only be modified if EFR[4] is set, i.e., EFR[ write enable. Re-enabling IER[1] will not cause a new interrupt if the THR is below the ...

Page 27

Philips Semiconductors Table 18: Priority level 7.10 Enhanced feature register (EFR) This 8-bit register enables or disables the enhanced features of the UART. shows the enhanced feature register bit settings. Table 19: Bit ...

Page 28

Philips Semiconductors 7.11 Divisor latches (DLL, DLH) These are two 8-bit registers which store the 16-bit divisor for generation of the baud clock in the baud rate generator. DLH stores the most significant part of the divisor. DLL stores the ...

Page 29

Philips Semiconductors 7.14 FIFO ready register The FIFO ready register provides real-time status of the transmit and receive FIFOs of both channels. Table 22: Bit 7 3 The FIFO Rdy register is a read-only register that ...

Page 30

Philips Semiconductors 8. Programmer’s guide The base set of registers that is used during high-speed data transfer have a straightforward access method. The extended function registers require special access bits to be decoded along with the address lines. The following ...

Page 31

Philips Semiconductors Table 23: Command Set TX FIFO and RX FIFO thresholds to VALUE Read FIFO Rdy register Set prescaler value to divide-by-1 Set prescaler value to divide-by-4 [1] 9397 750 11635 Product data Register programming guide sign here means ...

Page 32

Philips Semiconductors 9. Limiting values Table 24: Limiting values In accordance with the Absolute Maximum Rating System (IEC 60134). Symbol Parameter V supply voltage CC V input voltage I V output voltage O T operating ambient temperature amb T storage ...

Page 33

Philips Semiconductors [3] These junction temperatures reflect simulated conditions. Absolute maximum junction temperature is 150 C. The customer is responsible for verifying junction temperature. [4] These parameters apply for D7-D0. [5] These parameters apply for DTRA, DTRB, INIA, INTB, RTSA, ...

Page 34

Philips Semiconductors Table 26: AC electrical characteristics + 2.5 V, 3.3 V amb CC Symbol Parameter clock cycle period clock speed p3 t RESET pulse width ...

Page 35

Philips Semiconductors A0–A2 ADDRESS t su1 CSA, CSB t d5 IOW D0–D7 Fig 14. General write timing. IOW IOR t su3 XTAL1 Fig 15. Alternate read/write strobe timing. 9397 750 11635 Product data VALID t h4 ACTIVE ...

Page 36

Philips Semiconductors IOW ACTIVE RTSA, RTSB CHANGE OF STATE DTRA, DTRB CDA, CDB CTSA, CTSB DSRA, DSRB INTA, INTB IOR RIA, RIB Fig 16. Modem input/output timing. 9397 750 11635 Product data t d7 CHANGE OF STATE CHANGE OF STATE ...

Page 37

Philips Semiconductors START BIT RXA, RXB INTA, INTB IOR Fig 17. Receive timing. 9397 750 11635 Product data DATA BITS (5- DATA BITS 6 DATA BITS 7 DATA BITS 16 BAUD RATE CLOCK ...

Page 38

Philips Semiconductors START BIT RXA RXB RXRDYA RXRDYB IOR Fig 18. Receive ready timing in non-FIFO mode. START BIT RXA RXB RXRDYA RXRDYB IOR Fig 19. Receive ready timing in FIFO mode. 9397 750 11635 Product data DATA BITS (5-8) ...

Page 39

Philips Semiconductors START BIT TXA, TXB t d12 INTA, INTB t d13 ACTIVE IOW Fig 20. Transmit timing. 9397 750 11635 Product data DATA BITS (5- DATA BITS 6 DATA BITS 7 DATA ...

Page 40

Philips Semiconductors START BIT TXA, TXB ACTIVE IOW D0–D7 BYTE #1 TXRDYA, TXRDYB Fig 21. Transmit ready timing in non-FIFO mode. 9397 750 11635 Product data DATA BITS (5- d17 ACTIVE TRANSMITTER READY ...

Page 41

Philips Semiconductors START BIT TXA, TXB ACTIVE IOW D0–D7 BYTE #32 t d17 TXRDYA, TXRDYB Fig 22. Transmit ready timing in FIFO mode. 9397 750 11635 Product data DATA BITS (5- DATA BITS ...

Page 42

Philips Semiconductors 12. Package outline LQFP48: plastic low profile quad flat package; 48 leads; body 1 pin 1 index DIMENSIONS (mm are the ...

Page 43

Philips Semiconductors 13. Soldering 13.1 Introduction to soldering surface mount packages This text gives a very brief insight to a complex technology. A more in-depth account of soldering ICs can be found in our Data Handbook IC26; Integrated Circuit Packages ...

Page 44

Philips Semiconductors • For packages with leads on two sides and a pitch (e): – larger than or equal to 1.27 mm, the footprint longitudinal axis is preferred to be – smaller than 1.27 mm, the footprint longitudinal axis must ...

Page 45

Philips Semiconductors [3] These transparent plastic packages are extremely sensitive to reflow soldering conditions and must on no account be processed through more than one soldering cycle or subjected to infrared reflow soldering with peak temperature exceeding 217 C oven. ...

Page 46

Philips Semiconductors 15. Data sheet status [1] Level Data sheet status Product status I Objective data Development II Preliminary data Qualification III Product data Production [1] Please consult the most recently issued data sheet before initiating or completing a design. ...

Page 47

Philips Semiconductors Contents 1 Description . . . . . . . . . . . . . . . . . . . . . . . . . . . . . 1 2 Features . . . ...