CXA3506R Sony, CXA3506R Datasheet

CXA3506R

Specifications of CXA3506R

Available stocks

Related parts for CXA3506R

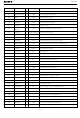

CXA3506R Summary of contents

Page 1

... A/D Converter Amplifier PLL Description The CXA3506R is a 3-channel 8-bit 120MSPS A/D converter with built-in amplifier and PLL developed for LCD projectors and LCD monitors. The CXA3506R inputs RGB graphics signals from personal computers or others. After the input levels are controlled, the A/D conversion is performed with a clock generated by PLL ...

Page 2

... AD, CC IR, 5 5.25 4.75 3.3 3 — — — 0.8 — DV PLL CC — — –0.8 DV PLL CC — — –1.6 — — 100 — — 120 — — 100 — — 100 –10 — +75 CXA3506R Unit °C W Unit MSPS MSPS MSPS MSPS °C ...

Page 3

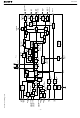

... CC R/CrIN2 141 AGNDAMPR 142 G/YOUT 143 DACTESTOUT 144 100 – 3 – CXA3506R 73 72 GA4 71 GA3 70 GA2 69 GA1 68 GA0 67 DGNDADTTL 66 DGNDAD3 65 DV ADTTL CC 64 BB7 63 BB6 62 BB5 61 BB4 60 BB3 59 GNDAD3 58 BB2 57 BB1 56 BB0 DGNDADTTL ADTTL CC 53 BA7 52 BA6 51 BA5 50 DGNDAD3 49 BA4 ...

Page 4

... VRB VRT B/CbOUT G/YOUT R/CrOUT CLPIN MODE DATA – 4 – CXA3506R EVEN/ODD XTLOAD RC2 RC1 HOLD UNLOCK C 3WIRE/I 2 SEROUT XSENABLE SCL SDA ADDRESS SAVE XPOWER SOGOUT ...

Page 5

... CXA3506R ...

Page 6

... CXA3506R ...

Page 7

... CXA3506R ...

Page 8

... CXA3506R 1/2CLK CLK ...

Page 9

... Data output for G-channel port A side O TTL Data output for G-channel port B side — 5V Digital power supply for A/D converter O 1.9V Bottom reference voltage output for A/D converter — GND Reference voltage GND for A/D converter – 9 – CXA3506R Description 2 C bus and 3-wire bus ...

Page 10

... Power supply for G/Y amplifier block — G/Y signal input 2 GND GND for G/Y amplifier block — Clamp capacitor for brightness — Clamp capacitor for brightness — Clamp capacitor for brightness 2.8V SYNC ON GREEN signal input 1 — B/Cb signal input 1 – 10 – CXA3506R Description ...

Page 11

... Power supply for R/Cr amplifier block I — R/Cr signal input 2 — GND GND for R/Cr amplifier block O 1.83V Monitor pin for amplifier output signal O 5V DAC testing output for amplifier block control register — GND GND – 11 – CXA3506R Description ...

Page 12

... AMPG CC 132 150 135 AGNDAMPG 100 – 12 – CXA3506R Description Amplifier output signal monitor. Each monitor can output either the entered signal immediately before A/D converter or the signal after switching between 2 types of input signals. The 2 types of input signals can be selected by the control register and output ...

Page 13

... FFH: 2.94V In case YCbCr is input G/YCLP is the same as above. R/Cr, B/CbCLP are as follows. CbCr Offset 00H: 3.04V 20H: 3.07V 3FH: 3.102V Clamp period: A clamp current of ±1.2mA (max.) flows. Signal period: A base current of 0.5µA flows to the IC. CXA3506R ...

Page 14

... DGNDPLLTTL DGNDPLL DV ADTTL CC 100k DGNDADTTL DGNDAD3 – 14 – CXA3506R Description Clamp pulse input for the signal of analog input clamp and brightness clamp. Both positive and negative polarity inputs are supported. The polarity is selected by the control register. The input pulse width should be 200ns or more ...

Page 15

... Top reference voltage output for A/D converter input dynamic range. 17 Connect ceramic capacitor. 20 AGNDADREF AV ADREF CC 20 Bottom reference voltage output for A/D converter input dynamic range. 93 Connect ceramic capacitor. 80 AGNDADREF – 15 – CXA3506R Description AD3 via a 1µF CC AD3 via a 1µF CC ...

Page 16

... DGNDPLL – 16 – CXA3506R Description Input SYNC signal at TTL level. The input polarity is switched by the control register. Leave this pin open when not used. Input SYNC signal at TTL level. The input polarity is switched by the control register. ...

Page 17

... AGNDIR DPGND 121 AGNDIR DPGND – 17 – CXA3506R Description This pin can output either DSYNC signal or DIVOUT signal. It can be selected by the control register. In addition, the output polarity can be selected by the control register. UNLOCK signal output. Make a discrimination between lock and unlock in the analog manner by connecting the external circuit ...

Page 18

... DGNDREG DV REG DGNDREG – 18 – CXA3506R Description TTL output GND for PLL. Analog power supply for IREF. Analog GND for IREF. Analog power supply for PLL VCO. Analog GND for PLL VCO. Input control register data. 2 Switching between the I C and ...

Page 19

... DGNDREG DV REG CC 12 100k DGNDREG DV REG DGNDREG – 19 – CXA3506R Description Inputs enable signal for 3-wire bus. High level: Control disabled Low level: Control enabled Connect this pin to GND when using Selection of input between I C bus and 3-wire bus 2/3V 3-wire bus mode ...

Page 20

... Current is output by open collector. Normally connect to AV DGNDREG This pin is connected to the die pad. Connect to the specified GND in Application Circuit. Not used. Leave this pin open or connect to GND. Not used. Leave this pin open or connect to GND. – 20 – CXA3506R Description . CC ...

Page 21

... Min. Typ. 2.0 — 0 — –2.0 — –5.0 — — 1.3 — 1.65 — — — — 300 — — 11 CXA3506R Max. Unit 240 mA 226 7 7.2 mA Max. Unit 5 µA 0 µA — V — MHz — ns — ...

Page 22

... Capacitive load of each Cb bus line Measurement conditions IH IL THHL2 THLH2 IH IL THHL3 THLH3 I = 3mA START condition: After this period, first clock is generated. – 22 – CXA3506R Min. Typ. Max. Unit 2.3 — 5 — 1.0 V –2.0 — 0 µA –5.0 — 0 µA — ...

Page 23

... MCM Vin = 0.6Vp-p RGB/YUV mode OUT Main Contrast = 255 Sub Contrast = 128 MCH Vin = 0.45Vp-p RGB/YUV mode OUT Main Contrast = 128 Sub Contrast = 0 SCL Vin = 0.85Vp-p RGB/YUV mode OUT – 23 – CXA3506R Min. Typ. Max. Unit LSB 1.388 1.588 1.788 V 1.63 1 ...

Page 24

... Vin = 0.6Vp-p Measurement conditions SYN SYN SYNC SEP V = 1000 TH TH SYNC SEP HYS SYNC SEP V = 1000 TH HYS SYNC SEP HYS – 24 – CXA3506R Min. Typ. Max. Unit 1.48 1.85 2.22 times – — 220 — MHz — –35 — ...

Page 25

... Fclk = 12.27MHz N = 780 Triggered at SYNC Fsync = 31.47kHz Fclk = 25.18MHz N = 800 Triggered at SYNC Fsync = 48.08kHz Fclk = 50.00MHz N = 1040 Triggered at SYNC Fsync = 56.48kHz Fclk = 75.00MHz N = 1328 Triggered at DSYNC – 25 – CXA3506R Min. Typ. Max. Unit — — 1 — 100 kHz 80 — 120 MHz 40 — ...

Page 26

... Maximum conversion frequency of 4:2:2 Data Fc out D2 Mode Maximum conversion frequency of 4:2:2 Data Fc out Special Mode Measurement conditions AVccAD3 as a reference AVccAD3 as a reference VRT – VRB – 26 – CXA3506R Min. Typ. Max. Unit — 8 — bit — 1.0 — LSB — ...

Page 27

... IH2 IL2 3. 0. –2mA OH1 –2mA OH2 –2mA OH3 –2mA OH4 1mA OL OL – 27 – CXA3506R Min. Typ. Max. Unit –1.15 — — V — — –1.5 V –100 — 100 µA –200 — 0 µA 2.0 — — V — — 0.8 V — 1.5 — ...

Page 28

... T F_DATA Ths Thh Td_1 Td_2 CL = 9pF Td_3 Td_4 CL = 9pF Difference between delay sync Td_5 signal and DIVOUT signal Td_6 Td_7 Td_8 – 28 – CXA3506R Min. Typ. Max. Unit 0.8 1.4 2.3 ns 1.0 1.5 2.8 ns 0.8 1.4 2.3 ns 1.0 1.5 2 ...

Page 29

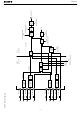

... DV VRB AD3 CC AV AGNDADREF PLLTTL CC DV DGNDPLLTTL XCLK CLK 1/2XCLK 1/2CLK DPGND DSYNC/DIVOUT UNLOCK SOGOUT HOLD XTLOAD EVEN/ODD – 29 – CXA3506R RB2 RB1 RB0 DGNDADTTL ADTTL DV CC RA7 DGNDAD3 AGNDAD3 RA6 RA5 RA4 RA3 RA2 DGNDAD3 RA1 RA0 DGNDADTTL ADTTL DV CC ...

Page 30

... CXA3506R ...

Page 31

... CXA3506R ...

Page 32

... CXA3506R ...

Page 33

... CXA3506R ...

Page 34

... PLL – 34 – CXA3506R AMP ...

Page 35

... SEP AMP SYNC – 35 – CXA3506R SAVE ADC POWER ...

Page 36

... SDA, SCL and XSENABLE pin threshold voltages Threshold voltage (Low 3-wire bus mode (High) and 2/ High) 1.95V High) 1.65V High) 1.65V – 36 – 1/2V V (5V (Low) 3-wire bus Threshold voltage (High Low) 1.6V Threshold voltage (High Low) 1.3V Threshold voltage (High Low) 1.3V CXA3506R ...

Page 37

... Set the VCO post-stage frequency divider (DIV1 and programmable counter (VCODIV) in the following order. The data is set when Register1 is sent. Register0 (SUB ADDRESS (H): 00) Register1 (SUB ADDRESS (H): 01 bus control mode MSB LSB READ/WRITE READ/WRITE 0: READ Mode 1: WRITE Mode T DH – 37 – CXA3506R T ENPW MSB DATA T ENH ...

Page 38

... AMP, ADC, PLL and SYNCSEP are all set to power save mode, and all the TTL output pins are set to high impedance mode. Therefore possible to share the same bus interface with other digital outputs having high impedance modes MSB D0 D1 LSB READ/WRITE READ/WRITE 0: READ Mode 1: WRITE Mode Function off Function on – 38 – CXA3506R T ENPW MSB DATA T ENH T D ...

Page 39

... When SCL pin is high level, the signal input to SDA pin has a rising edge, there is STOP CONDITION 1/3V 2/ 1001 1000 1001 1100 1001 1110 , 1/2V and 3/ bus mode, sub address is 5 bits, and 3 bits of MSB ACK SUB ADDRESS DATA – 39 – (5V 1001 1010 ACK ACK DATA STOP CONDITION CXA3506R S0 0 ...

Page 40

... AMP, ADC, PLL and SYNCSEP are all set to power save mode, and all the TTL output pins are set to high impedance mode. Therefore possible to share the same bus interface with other digital outputs having high impedance modes. T F_REG HD;DAT HIGH SU;DAT SU;STA – 40 – CXA3506R T HD;STA SU;STO ...

Page 41

... The clamp pulse input polarity can be selected by an internal switch. Register: CLP POL Clamp pulse polarity driver cannot be supported. In addition, 2 after the two lines of select switch, the 1 0 RGB input YCbCr input 0 1 IN2 IN1 0 1 POSITIVE NEGATIVE – 41 – CXA3506R resistor between the OUT pins 2 ...

Page 42

... CXA3506R 1 are set to 128 · · · 255 1.53 · · · 2.24 128 · · · 255 0% · ...

Page 43

... YCbCr 0 · · · 112LSB · · · 128LSB 1 YCbCr – 43 – CXA3506R 128 · · · 255 · · · +61LSB 128 · · · 255 · · · +61LSB 128 · · · 255 · ...

Page 44

... When inputting Y, Cb and Cr, be sure to input according to the table above possible for only the R/Cr IN and B/Cb IN pins to be clamped to the center of the ADC input dynamic range. Output Pin No. Symbol GA0 to GA7 78 85, 87, 88 GB0 to GB7 BA0 to BA7 BB0 to BB7 21, 22 28, 31 RA0 to RA7 RB0 to RB7 – 44 – CXA3506R ...

Page 45

... SYNC signal input pin 0000 · · · 1111 75mV 9.3mV step 215mV 2mV 20mV 45mV 0 Sync separated signal Externally input SYNC signal G/YIN1 pin SYNCIN1 pin G/YIN2 pin SYNCIN2 pin – 45 – ) and hysteresis level TH SYNC signal Pedestal level HYS 11 70mV 1 CXA3506R ...

Page 46

... When the SOGOUT pin is not used possible to turn off the TTL output using a control register. But it cannot be set to high impedance. Register: SOG Enable SOGOUT output status 0 SYNCT1, SYNCT2 SYNCP1, SYNCP2 or SYNCIN1, SYNCIN2 1 0 IN1 IN2 IN1 IN2 0 1 Negative Positive 0 1 Off On – 46 – CXA3506R 1 ...

Page 47

... HOLD signal input polarity For details, see the hold timing diagram SYNCIN1 SYNCIN2 0 1 Positive Negative LPF VCO Programmable counter 0 Held while HOLD signal is Low – 47 – B DIV Point A: VCO oscillation frequency Point B: Clock frequency 1 Held while HOLD signal is High CXA3506R ...

Page 48

... In case of using any resistors or capacitors except those given above not guaranteed. • VCO The VCO oscillation frequency range covers from 40MHz to 165MHz 100µA 200µA 300µA 400µA – 48 – CXA3506R 500µA 600µA 700µA 800µA ...

Page 49

... PLL timing diagram). Although the clock output can be turned off independently by using a control register, it cannot be set to high impedance. The operational frequency of the clock 100MHz. Register: CLK Enable, XCLK Enable Clock output status 1/1 1/2 1/4 1 Data6 Data5 Data4 Data3 Off – 49 – CXA3506R Data2 Data1 Data0 LSB ...

Page 50

... Fixed (depends on input SYNC signal width) — On/Off On/Off On/Off – 50 – DSYNC signal DIVOUT signal Register 3CLK to 6CLK COARSE DELAY FINE DELAY 8CLK DIVOUT WIDTH 4, 5CLK DIVOUT DELAY On/Off DSYNC POL On/Off DSYNC Enable On/Off DSYNC Hold CXA3506R ...

Page 51

... Negative Positive Off – 51 – CXA3506R 111111 64/32CLK 11 6CLK 11 8CLK ...

Page 52

... XTLOAD pin Programmable counter status 0 Using HOLD signal logic HOLD signal logic (When HOLD POL register = Forcible reset – 52 – 1 DSYNC signal/DIVOUT signal Delay sync output L DIVOUT signal L DSYNC signal DIVOUT signal DIVOUT signal DSYNC signal DSYNC signal H Count CXA3506R ...

Page 53

... CASE the DSYNC POL register is "1". In addition, the DSYNC signal output and DIVOUT signal output can be switched by using the DSYNC By-pass register.) CASE 1 SYNC signal (SYNC POL = 1) HOLD signal (1) DSYNC Hold = 1 DSYNC signal DIVOUT signal (2) DSYNC Hold = 0 DSYNC signal DIVOUT signal – 53 – CXA3506R ...

Page 54

... CASE 2 SYNC signal (SYNC POL = 1) HOLD signal (1) DSYNC Hold = 1 DSYNC signal DIVOUT signal (2) DSYNC Hold = 0 DSYNC signal DIVOUT signal – 54 – CXA3506R ...

Page 55

... CASE 3 SYNC signal (SYNC POL = 1) HOLD signal (1) DSYNC Hold = 1 DSYNC signal DIVOUT signal (2) DSYNC Hold = 0 DSYNC signal DIVOUT signal – 55 – CXA3506R ...

Page 56

... SYNC signal. See the diagram for details on timing. LPF PD CP VCO Programmable counter 0.5H 0.5H 0.5H 0. 0.5H 0.5H 0.5H H 8CLK Tw (min) = 100ns – 56 – DIV Clock output "HSYNC" and "XTLOAD" are synchronized CXA3506R ...

Page 57

... · 10 · 1 · 10 /(0.1 · 10 –9 – · 10 · 1 · 10 /(0.1 · 10 Thh Ths V –Q C VCO = 1nA, Thold = 1ms 0.33µF, KVCO = 2 · 55 [MHz/V], –6 – · 10 [V] – · 2 · 70 · 1050 [Hz] – 57 – Thh Ths Thold f CXA3506R ...

Page 58

... UNLOCK signal will go from low to high and the PLL will be judged as unlocked signal signal L H UNLOCK signal L IC internal IC external Vcc R3 50k 104 Q1 S1 signal UNLOCK detect – 58 – Vcc UNLOCK signal S2 signal 100 R2 = 100k C1 = 0.01 F Threshold level of the inverter Threshold level of the inverter Threshold level of the inverter CXA3506R ...

Page 59

... The CXA3506R's charge pump is a constant-current output type as shown below LPF 1/S + – 1/S The PLL closed loop transmittance is obtained by the following formula. o/N KPD · F (S) · KVCO · 1/N · 1 KPD · F (S) · KVCO · 1/N · 1/S ...

Page 60

... VCO. In addition to this, however, the loop filter also functions as an important element in determining the PLL response characteristics. Typical examples of loop filters include lag filters, lag-lead filters, active filters, etc. However, the CXA3506R's LPF is a current input type active filter as shown below, so the following calculations show an actual example of deriving the PLL closed loop transmittance when using this type of filter and then using this transmittance to create a formula for setting the filter constants ...

Page 61

... The filter transmittance is as follows · R · ( (( · C2 · R · · ( · · · C2 · Here, assuming C2 = C1/100, then: C1 · C1/100 · C1/100 · R 101 101 Vo The Bode diagram for formula ( follows. ................... (3) – 61 – CXA3506R log log 0 –45deg –90 ...

Page 62

... Next, the various parameters inside an actual CXA3506R are obtained. The CXA3506R's charge pump output block and the LPF circuit are as follows. 100 A 100 A to step 800 A 100 A 100 A to step 800 A First, KPD is as follows. KPD = 100µ/2 or 200µ/2 500µ ...

Page 63

... CXA3506R VCO oscillation frequency MHz 98.18 73.64 98.18 108.00 58.75 88.13 117.50 108.00 144.01 148.50 148.50 84.19 100 ...

Page 64

... CLK Jitter Evaluation Method The generated CLK is obtained by inputting Hsync to the CXA3506R. Apply this CLK to a digital oscilloscope and observe the CLK waveform using Hsync as the trigger. Hsync signal Pulse generator H sync Computer signal Hsync signal Clock Trigger Clock The CLK jitter is measured at peak to peak in the long-term write mode of the digital oscilloscope as shown in the figure ...

Page 65

... Data out special Mode For a description of each operational mode, see the next page Internal CLK External CLK AD3 power pin. Also, the VRB pin is set to a voltage CC Register: DATA OUT MODE – 65 – CXA3506R AD3 power supply pins for these CC ...

Page 66

... The following type of interface is possible when this IC is operated in Straight Data out Mode. CXA3506R CLK XCLK 1/2CLK 1/2XCLK RA0 to RA7 GA0 to GA7 BA0 to BA7 The hold time of the post-stage scaling IC using the interface shown above is, th (min.) = 2.2ns 99 98 101 Td_8 2.2ns (min.) to 3.8ns (max.) 100 max. min. th (min.) – 66 – CXA3506R Scaling IC ...

Page 67

... With the interface shown above, the post-stage scaling IC acquire data by using the clock signal output from the 1/2CLK pin of the ADC. In case of this interface, the setup time of the post-stage scaling IC is, ts (min – 3.2ns While the hold time is, th (min 2.3ns Td_7 2.3ns (min.) to 3.2ns (max 101 100 max. min – 67 – T Scaling IC CXA3506R ...

Page 68

... ADC, while port B data is acquired by using the clock signal output from the 1/2XCLK pin. In case of this interface, the setup time of the post-stage scaling IC is, ts (min – 3.2ns While the hold time is, th (min 2.3ns T Td max. min max. min Td_7 2.3ns (min.) to 3.2ns (max.) – 68 – CXA3506R Scaling IC ...

Page 69

... An interface of the following type is possible when this IC is run in 4:2:2 Data out D2 Mode. CXA3506R CLK XCLK 1/2CLK 1/2XCLK GA0 to GA7 BA0 to BA7 The hold time of the post-stage scaling IC using the interface shown above is, th (min.) = 2.2ns 99 98 101 Td_8 2.2ns (min.) to 3.8ns (max.) 100 max. min. – 69 – CXA3506R Scaling IC ...

Page 70

... An interface of the following type is possible when this IC is run in 4:2:2 Data out D2 Mode. CXA3506R 99 CLK 98 XCLK 101 1/2CLK 100 1/2XCLK GA0 to GA7 BA0 to BA7 The hold time of the post-stage scaling IC using the interface shown above is, th (min.) = 2.2ns Td_8 2.2ns (min.) to 3.8ns (max.) max. min. – 70 – CXA3506R Scaling IC ...

Page 71

... EVEN/ODD pin. Be sure to input signal to the EVEN/ODD pin at TTL level. EVEN/ODD pin Operational mode Example of Using the EVEN/ODD Function Analog input signal Hsync Sampling CLK Vsync Toggle signal (EVEN/ODD pin EVEN ODD EVEN field EVEN/ODD frame – 71 – CXA3506R ODD field ...

Page 72

... The blocks except the registers can also be set to power save mode by the control register. Selects according to using state. Register ADC Power Save AMP Power Save PLL Power Save SYNC SEP Power Save 2.2V 2.45V 2. Power on Power save 0 1 Power save Power on Power on Power save Power on Power save Power on Power save – 72 – CXA3506R 11 2.95V ...

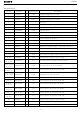

Page 73

... Signal — Signal Signal Signal Signal Signal Signal Signal Signal Signal Signal Signal Signal Signal Signal Signal Signal – 73 – CXA3506R YUV 4:2:2 YUV 4:2:2 D2 Special mode mode — — — — DATA DATA — — DATA DATA — — DSYNC ...

Page 74

... CC PLLTTL 5V (D) 41.4mA CC 5V (A) 6.8mA ADTTL 5V (D) 73.2mA CC AD3 3.3V (A) 180mA CC AMP = AV AMPR + AV AMPG + – 74 – CXA3506R CC5PS Register PS current XPS current consumption consumption 17.2mA 1.2mA 0.7mA 0.7mA 0mA 0mA 2.0mA 1.0mA 0.4mA 0.4mA 6.0mA 6.0mA 3.0mA 3.0mA AMPB CC , ...

Page 75

... CXA3506R ...

Page 76

... CXA3506R ...

Page 77

... CXA3506R ...

Page 78

... CXA3506R ...

Page 79

... Straight Data out Mode, 4:2:2 Data out D2 Mode, and 4:2:2 Data out special Mode. Td_6 min. typ. max. 0.9ns to 1.2ns to 1.6ns Td_8 min. typ. max. 2.2ns to 2.8ns to 3.8ns – 79 – CXA3506R 2.0V 0.8V min. typ. max. T 0.8ns 1.4ns 2.3ns R_CLK T 1.0ns 1 ...

Page 80

... The output delay time in this mode is the same as that in DMUX Interleaved Data out Mode. T Td_6 min. typ. max. 0.9ns to 1.2ns to 1.6ns T – 2.2ns T + 1.3ns min. min. Td_7 min. typ. max. 2.3ns to 2.6ns to 3.2ns – 80 – CXA3506R 2.0V 0.8V min. typ. max. T 0.8ns 1.4ns 2.3ns R_CLK T 1.0ns 1.5ns 2.8ns F_CLK 2.0V 0.8V min ...

Page 81

... BIN1 (133 pin) BIN2 (136 pin) SYNCIN1 (111 pin) SYNCIN2 (112 pin) DSYNC (103 pin) CLK (99 pin) XCLK (98 pin) 1/2CLK (101 pin) 1/2XCLK (100 pin) Data out RA7 to RA0 GA7 to GA0 BA7 to BA0 RB7 to RB0 GB7 to GB0 BB7 to BB0 – 81 – CXA3506R N10 N7 ...

Page 82

... BIN2 (136 pin) SYNCIN1 (111 pin) SYNCIN2 (112 pin) DSYNC (103 pin) CLK (99 pin) XCLK (98 pin) 1/2CLK (101 pin) 1/2XCLK (100 pin) Data out RA7 to RA0 GA7 to GA0 BA7 to BA0 RB7 to RB0 GB7 to GB0 BB7 to BB0 – 82 – CXA3506R N10 N6 N7 ...

Page 83

... BIN1 (133 pin) BIN2 (136 pin) SYNCIN1 (111 pin) SYNCIN2 (112 pin) DSYNC (103 pin) CLK (99 pin) XCLK (98 pin) 1/2CLK (101 pin) 1/2XCLK (100 pin) Data out RA7 to RA0 GA7 to GA0 BA7 to BA0 RB7 to RB0 GB7 to GB0 BB7 to BB0 – 83 – CXA3506R N10 N7 ...

Page 84

... SYNCIN2 (112 pin) DSYNC (103 pin) CLK (99 pin) XCLK (98 pin) 1/2CLK (101 pin) 1/2XCLK (100 pin) Data out GA7 to GA0 BA7 to BA0 Cb3 Cb5 Cr3 Cr5 Y2 Y3 Cb3 (U3) Cr3 (V3) Cb5 (U5) Cr5 (V5) Cb7 (U7) Cr7 (V7) – 84 – Cb9 Cb7 Cr9 Cr7 CXA3506R Y10 Y8 ...

Page 85

... SYNCIN2 (112 pin) DSYNC (103 pin) CLK (99 pin) XCLK (98 pin) 1/2CLK (101 pin) 1/2XCLK (100 pin) Data out GA7 to GA0 BA7 to BA0 Cb3 Cb5 Cr2 Cr4 Y2 Y3 Cr2 (V3) Cb3 (U3) – 85 – Cb9 Cb7 Cr8 Cr6 Cr4 (V4) Cb5 (U5) Cr6 (V6) Cb7 (U7) Cr8 (V8) CXA3506R Y10 Cr10 Y8 ...

Page 86

... GA7 to GA0 BA7 to BA0 RB7 to RB0 GB7 to GB0 BB7 to BB0 N10 N10 – 86 – N18 N11 N12 N17 N13 N16 N15 N14 N10 N18 N11 N12 N17 N13 N16 N15 N14 N11 CXA3506R N19 N20 N21 N12 N14 N19 N20 N21 N13 ...

Page 87

... BA7 to BA0 RB7 to RB0 GB7 to GB0 BB7 to BB0 N10 N10 – 87 – N18 N11 N12 N17 N13 N16 N15 N14 N10 N18 N11 N12 N17 N13 N16 N15 N14 N11 CXA3506R N19 N20 N21 N12 N14 N19 N20 N21 N13 N15 ...

Page 88

... BA7 to BA0 RB7 to RB0 GB7 to GB0 BB7 to BB0 N10 N11 N10 N11 – 88 – N18 N19 N12 N17 N13 N16 N15 N14 N6 N10 N8 N12 N18 N19 N12 N17 N13 N16 N15 N14 N7 N11 N9 N13 CXA3506R N20 N21 N14 N20 N21 N15 ...

Page 89

... CbCr Clamp Level Control Characteristics 150 145 140 135 130 125 120 115 110 105 100 200 250 0 SYNC SEP – 89 – CXA3506R Main contrast = 128 OUT 50 100 150 200 250 Sub Contrast register CbCr offset register Control Characteristics HYS register HYS 3 ...

Page 90

... Brightness Level Temperature Characteristics 0.6 0.5 0.4 0.3 0.2 0.1 0 –0.1 –0.2 –0.3 5.25 –10 0 CbCr Clamp Level Temperature Characteristics 0.6 0.4 0.2 0 –0.2 –0.4 –0.6 5.25 –10 0 – 90 – CXA3506R – Ambient temperature [ C] Brightness = 128 – Ambient temperature [ C] CbCr offset register = ...

Page 91

... NTSC, DIV = 1/8, VGA, DIV = 1/4, SVGA, DIV = 1/4, 1/ 010, 100, 101 XGA, DIV = 1/2, 100 120 – 91 – CXA3506R KVCO Characteristics DIV = 1/1 DIV = 1/2 DIV = 1/4 DIV = 1/8 2.0 2.5 3.0 3.5 4.0 4.5 VCO control voltage [ 010, 100 ...

Page 92

... Operational mode: DMUX parallel Data out Load capacitance 10pF L 240 220 200 180 160 FCLK – Clock frequency [MHz] Current Consumption vs. Supply Voltage Fluctuation 200 180 CLK = DC 160 50 75 3.0 4. 100 120 – 92 – CXA3506R CLK = DC 3.3 3 5.0 5. Supply voltage [ ...

Page 93

... CC VRB AD3 AGNDADREF PLLTTL DV CC DGNDPLLTTL XCLK CLK 1/2XCLK 1/2CLK DPGND DSYNC/DIVOUT UNLOCK SOGOUT HOLD XTLOAD EVEN/ODD – 93 – CXA3506R RB2 RB1 RB0 DGNDADTTL ADTTL CC DV RA7 DGNDAD3 AGNDAD3 RA6 RA5 RA4 RA3 RA2 DGNDAD3 RA1 RA0 DGNDADTTL ADTTL DV CC AD3 ...

Page 94

... CC VRB AD3 AGNDADREF PLLTTL CC DV DGNDPLLTTL XCLK CLK 1/2XCLK 1/2CLK DPGND DSYNC/DIVOUT UNLOCK SOGOUT HOLD XTLOAD EVEN/ODD – 94 – CXA3506R RB2 RB1 RB0 DGNDADTTL ADTTL DV CC RA7 DGNDAD3 AGNDAD3 RA6 RA5 RA4 RA3 RA2 DGNDAD3 RA1 RA0 DGNDADTTL ADTTL DV CC AD3 ...

Page 95

... Put this IC into power save mode when making a connection between data output and another IC. (High impedance cannot be set when pins are disabled separately.) AD3 as 3.3V power supply, use the same 3.3V analog power supply CC AD3 and DV AD3, respectively. Use the same ground CC CC – 95 – CXA3506R ...

Page 96

... LCD projector and monitor so that performance can be maximized. The DSUB 15-pin connector is used as the input connector that allows the direct input of a video signal from a PC. The input video signal is A/D converted by the CXA3506R and a pin for monitoring is designed onto the board so that output data can be checked directly. ...

Page 97

... CXA3506R ...

Page 98

... Do not apply power supply in this state. 2. Check the direction of SW1. SW1 is the power save control switch. The CXA3506R is put into power save mode when SW1 is set to the rear position ( ). Set SW1 to the forward ( ) position when using the CXA3506R. SW1 is connected to the XPOWER SAVE pin. ...

Page 99

... The following control window will open when the A3506.exe file starts. Use this window to make board settings in response to the printer port address of the PC. Be sure to set the address for the PC from the pull-down menu port at the top-left of the control screen. There are two types of addresses: 378 and 3BC. – 99 – CXA3506R ...

Page 100

... Use this window to make board settings in response to the printer port address of the PC. Be sure to set the address for the PC from the pull-down menu port at the top-left of the control screen. There are two types of addresses: 378 and 3BC. – 100 – CXA3506R ...

Page 101

... When the program is accurately installed on the PC, be sure to re-check items 2 and 3 of the operational procedures above when the IC does not move the CXA3506R does not move even after item 1 above is checked possible that the control signals of the control register are not output from the PC printer board. In this case, be sure to re-check the board settings listed for item 4 under " ...

Page 102

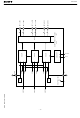

... CXA3506R Evaluation Board Parts List Parts No. IC1 CXA3506R IC2 CXA2016S IC3 CXA3197R IC6 SN74LS04N IC7 SN74LS32N IC8 SN74LS08N IC9 LT1086CM-3.3 CON1 D02-N15SAG-13L9 CON4 53053-0510 CON5 53053-0610 SW1 G-12AP SW2 G-13AP SW3 G-22AP L1, 2 ZBF503D-00 R1, 2 620 Chip resistor R3, 4 200 Chip resistor R5 3 ...

Page 103

... UNLOCK UNLOCK 104 SOGOUT SOGOUT 105 DGND HOLD 106 XTLOAD XTLOAD 107 EVEN/ODD EVEN/ODD 108 CLAMP AVcc VSYNC1 VSYNC2 AGND AGND – 103 – CXA3506R DGND RB2 BB2 36 RB1 35 BB1 RB0 BB0 34 0.1 DGNDADTTL 33 C38 DVccADTTL 32 RA7 BA7 31 DGNDAD3 30 AGNDAD3 ...

Page 104

... R30 VREF 34 AGND2 33 AOUTP 32 AOUTN 31 0.1 C69 75 R29 AVccO 30 DVcc2 DGND2 25 AVcc2 0.1 C58 36 VSET 35 620 R28 1K R27 VREF 34 AGND2 33 AOUTP 32 AOUTN 31 0.1 C68 75 R26 AVccO 30 DVcc2 DGND2 25 DSYNC Vsync IN2 Video VSYNC2 S6 VSYNC1 S5 Vsync IN1 Video – 104 – CXA3506R ...

Page 105

... Vin 3 Vout 2 GND 1 SDA SCL SENABLE SEROUT – 105 – CXA3506R ...

Page 106

... CXA3506R ...

Page 107

... CXA3506R ...

Page 108

... CXA3506R ...

Page 109

... CXA3506R ...

Page 110

... LQFP (PLASTIC) 22.0 0.2 20.0 0 0. 0.20 0˚ to 10˚ DETAIL B PACKAGE STRUCTURE PACKAGE MATERIAL LEAD TREATMENT LQFP-144P-L01 LEAD MATERIAL LQFP144-P-2020 PACKAGE MASS – 110 – 1.7 MAX 1 0.03 EPOXY RESIN PALLADIUM PLATING COPPER ALLOY 1.3 g CXA3506R Sony Corporation ...