HDMP-1536A Agilent Technologies, Inc., HDMP-1536A Datasheet

HDMP-1536A

Available stocks

Related parts for HDMP-1536A

HDMP-1536A Summary of contents

Page 1

... Low Power Consumption, 630 mW • Transmitter and Receiver Functions Incorporated onto a Single IC • Auto Frequency Lock • Small Package Profile HDMP-1536A, 10x10 mm QFP HDMP-1546A, 14x14 mm QFP • 10-Bit Wide Parallel TTL Compatible I/Os • Single +3.3 V Power Supply • 5 Volt Tolerant I/Os • ...

Page 2

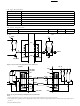

... PROTOCOL DEVICE RBC0 RBC1 BYTSYNC REFCLK ENBYTSYNC Figure 1. Typical Application Using the HDMP-15x6A. DATA BYTE TX[0-9] TX TXCAP0 PLL/CLOCK TXCAP1 GENERATOR REFCLK RXCAP0 RXCAP1 RBC0 RBC1 DATA BYTE RX[0-9] BYTE SYNC BYTSYNC Figure 2. HDMP-15x6A Transceiver Block Diagram. HDMP-15x6A TRANSMITTER SECTION PLL PLL ...

Page 3

... This may be useful in proprietary ap- plications which use alternative methods to align the parallel data. HDMP-1536/46A Block Diagram The HDMP-1536/46A was designed to transmit and receive 10-bit wide parallel data over a single high-speed line, as specified for the FC-0 layer of the Fibre Channel standard. The ...

Page 4

MHz for the input sampler, and recovers the two 53.125 MHz receiver byte clocks (RBC1/RBC0). These clocks are 180 degrees out of phase with each other, and are alternately used to clock the 10-bit parallel output ...

Page 5

... HDMP-1536/46A (Transmitter Section) Timing Characteristics Symbol Parameter t Setup Time setup t Hold Time hold [2] t_txlat Transmitter Latency Notes: 1. Device tested and characterized under T 2. The transmitter latency, as shown in Figure 4, is defined as the time between the latching in of the parallel data word (as triggered by the rising edge of the transmit byte clock, REFCLK) and the transmission of the first serial bit of that parallel word (defined by the rising edge of the first bit transmitted) ...

Page 6

... HDMP-1536/46A (Receiver Section) Timing Characteristics Symbol [2,3] b_sync Bit Sync Time t Time Data Valid Before Rising Edge of RBC valid_before t Time Data Valid After Rising Edge of RBC valid_after t RBC Duty Cycle duty A-B [4] t Rising Edge Time Difference between RBC0 and RBC1. ...

Page 7

Absolute Maximum Ratings except as specified. Operation in excess of any one of these conditions may result in permanent A damage to this device. Symbol V Supply Voltage CC V TTL Input Voltage IN,TTL V HS_IN ...

Page 8

... Differential HS_OUT Output (Dout+ Minus Dout-). 200.0 ps/div b. Single-Ended HS_OUT Output (Dout+). Eye Diagrams of the High-Speed Serial Outputs from the HDMP-1536/46A as Captured on the HP 83480A Digital Communications Analyzer. Tested with PRBS = 2 Figure 7. Transmitter DOUT Eye Diagrams. Parameter conditions specified, with T ...

Page 9

... the max I and subtracting the power dissipated outside the chip at the high speed 3.45 volts. CC resistors and receiver TTL outputs driving 10 pF loads. for these devices is 56 C/Watt for the HDMP-1536A and Pd), where the power being dissipated. 9 Units Typ. ...

Page 10

I/O Type Definitions I/O Type I-TTL Input TTL, Floats High When Left Open O-TTL Output TTL HS_OUT High Speed Output, ECL Compatible HS_IN High Speed Input C External Circuit Node S Power Supply or Ground Pin Input Capacitance Symbol C ...

Page 11

... S = SUPPLIER CODE YYWW = DATE CODE (YY = YEAR WORK WEEK) COUNTRY = COUNTRY OF MANUFACTURE Figure 11. HDMP-1536/46A (TRx) Package Layout and Marking, Top View. *N/C: This pin is connected to an isolated pad and has no functionality. It can be left open, however, TTL levels can also be applied to this pin. ...

Page 12

TRx I/O Definition Name Pin Type BYTSYNC 47 O-TTL Byte Sync Output: An active high output. Used to indicate detection of a comma character (0011111XXX only active when ENBYTSYNC is enabled. -DIN 52 HS_IN Serial Data Inputs: High-speed ...

Page 13

TRx I/O Definition (cont’d.) Name Pin Type RX[0] 45 O-TTL RX[1] 44 RX[2] 43 RX[3] 41 RX[4] 40 RX[5] 39 RX[6] 38 RX[7] 36 RX[8] 35 RX[9] 34 RXCAP0 48 C RXCAP1 49 SIG_DET 26 O-TTL TX[0] 2 I-TTL TX[1] ...

Page 14

... Transceiver Power Supply Bypass and Loop Filter Capacitors Bypass capacitors should be used and placed as close as possible to the appropriate power supply pins of the HDMP-1536/46A as shown on the schematic of Figure 12. All bypass chip capacitors are 0.1 F. The V _RXA and CC V _TXA pins are the analog ...

Page 15

... HDMP-15x6A TOP VIEW Part Number A1 A2 HDMP-1536A 10.00 13.20 HDMP-1546A 14.00 17.20 Tolerance 0.10 0.25 Figure 13. Mechanical Dimensions of HDMP-1536/46A. Details Plastic 85% Tin, 15% Lead 300-800 m HDMP-1536A: 0.08 mm max. HDMP-1546A: 0.10 mm max 0.22 0.50 0.60 0.17 0.25 0.35 0.80 0.88 0.17 0.25 0.05 Basic +0 ...

Page 16

... Data subject to change. Copyright © 1999 Agilent Technologies, Inc. Obsoletes 5966-0232E 5966-2717E (11/99) ...