VSC8062QH Vitesse Semiconductor Corp., VSC8062QH Datasheet

VSC8062QH

Specifications of VSC8062QH

Available stocks

Related parts for VSC8062QH

VSC8062QH Summary of contents

Page 1

Data Sheet VSC8061/VSC8062 Features • Serial Data Rate up to 2.5Gb/s • 16-Bit Wide ECL 100K Compatible Parallel Data Interface • Differential High-Speed Data Outputs • Differential or Single-Ended High-Speed Data and Clock Inputs • On-Chip Phase Detector (VSC8061 Multiplexer) ...

Page 2

Multiplexer/Demultiplexer Chipset Parallel Data Receivers D 15 Input Registers CLK CLKN DCLK DCLKN DI DIN Register CLK CLKN Page 2 © VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012 Tel: (800) ...

Page 3

Data Sheet VSC8061/VSC8062 VSC8061 Multiplexer AC Characteristics CLK (CLKN) High-speed differential clock input CLK16 (CLK16N) Parallel data clock output D[0:15] Parallel data inputs DCLK (DCLKN) Parallel data clock input DO (DON) High-speed differential serial data output =Don’t care NOTE: Table ...

Page 4

Multiplexer/Demultiplexer Chipset VSC8061 Phase Detector Logic Diagram The internal phase detector of the VSC8061 compares the phase difference between the internally gener- ated divide-by-16 clock and the DCLK input. If both inputs (CLK16 and DCLK) to the phase ...

Page 5

Data Sheet VSC8061/VSC8062 VSC8062 Demultiplexer AC Characteristics CLK (CLKN) High-speed differential clock input DI (DIN) High-speed serial data input CLK16 Parallel data clock output D0 D1 D15 Table 2: VSC8062 AC Characteristics Parameter Description (1) t Clock period CLK t ...

Page 6

Multiplexer/Demultiplexer Chipset DC Characteristics Table 3: ECL Inputs and Outputs (Over recommended operating conditions with internal V Parameter Description V Output HIGH voltage OH V Output LOW voltage OL V Input HIGH voltage IH V Input LOW voltage ...

Page 7

Data Sheet VSC8061/VSC8062 Absolute Maximum Ratings Power Supply Voltage (V ) ............................................................................................................ -3.0V to 0.5V TT Power Supply Voltage (V ) ................................................................................................. V EE (2) Input Voltage Applied (V ECLIN High-Speed Input Voltage Applied Output Current, I (DC, output HI) ...

Page 8

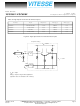

Multiplexer/Demultiplexer Chipset Coupling for Inputs Figure 7: AC-Coupling for DCLK, DCLKN Inputs typ = 0 typ = 0.1 F for single-ended applications SE (Capacitor values ...

Page 9

Data Sheet VSC8061/VSC8062 Table 6: High-Speed Clock and Serial Data Inputs Product VSC8061 DCLK, DCLKN VSC8061 VSC8062 VSC8062 Figure 8: High-Speed Clock and Serial Data Inputs ...

Page 10

Multiplexer/Demultiplexer Chipset Package Pin Descriptions Figure 9: VSC8061/8062 F (52-Pin LDCC) Pin Diagrams Heat Sink Up Top View VCC D5 D6 VTT D7 D8 VCC D9 D10 NC D10 VCC VTT VCC NC *Heat sink ...

Page 11

... VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012 Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com 05/11/01 VITESSE SEMICONDUCTOR CORPORATION 52 1 VITESSE U D VSC8061QH VITESSE VSC8062QH Internet: www.vitesse.com 2.5Gb/s 16-Bit Multiplexer/Demultiplexer Chipset VCC CLK CLKN VEE VTT CLK16 CLK16N D15 D14 D13 D12 ...

Page 12

Multiplexer/Demultiplexer Chipset Table 7: VSC8061 Pin Identifications Pin Number Pin number QH Package F Package 1- 11, 15-20, 22- 8-42, 44, 45, 25, 28-32 ...

Page 13

Data Sheet VSC8061/VSC8062 Table 8: VSC8062 Pin Identifications Pin Number Pin Number QH Package F Package 31, 32, 8-11, 15-20, 34, 35, 39-42, 22-25, 28, 29 ...

Page 14

Multiplexer/Demultiplexer Chipset Package Information B HEAT SINK SIDE PACKAGE IS CAVITY DOWN Item mm (Min/Max) A 18.54/19.56 B 1.02/1.52 (1) C 15.49/16.51 (1) D 15.24 TYP E 1.27 TYP NOTE: (1) At ...

Page 15

Data Sheet VSC8061/VSC8062 TYP TYP 0.30 RAD. TYP. 0.20 RAD. TYP. 0.17 MAX. NOTES: Drawing not to scale. Heat spreader up. All units in mm unless otherwise noted. G52069-0, Rev 4.3 ...

Page 16

Multiplexer/Demultiplexer Chipset Thermal Considerations The VSC8061 and VSC8062 are available in ceramic LDCC and thermally enhanced plastic quad flat- packs. These packages have been enhanced to improve thermal dissipation through low thermal resistance paths from the die to ...

Page 17

Data Sheet VSC8061/VSC8062 The worst-case temperature rise from case to ambient is given by the equation: where: = Theta sink-to-ambient SA = Theta case-to-sink CS = Air temperature, user supplied (typically +55 A(MAX) = Case temperature (+85 C(MAX ...

Page 18

Multiplexer/Demultiplexer Chipset Figure 12: Data Eye From Serial Output of VSC8061 in QH Package (D0/D0N) Amplitude: 200 mV/div Time Scale: 50 ps/div Data Rate: 2.5 Gb/s 2.5Gb PRB Data 1:16 De-serializer Page 18 © ...

Page 19

Data Sheet VSC8061/VSC8062 Ordering Information The order number for this product is formed by a combination of the device number, package type, and the operating temperature range. Device Type VSC8061: 2.5Gb/s 16-bit Multiplexer VSC8062: 2.5Gb/s 16-bit Demultiplexer Notice Vitesse Semiconductor ...

Page 20

Multiplexer/Demultiplexer Chipset Page 20 © VITESSE SEMICONDUCTOR CORPORATION • 741 Calle Plano • Camarillo, CA 93012 Tel: (800) VITESSE • FAX: (805) 987-5896 • Email: prodinfo@vitesse.com VITESSE SEMICONDUCTOR CORPORATION Internet: www.vitesse.com Data Sheet VSC8061/VSC8062 G52069-0, Rev 4.3 05/11/01 ...