CY37128VP84-125JC Cypress Semiconductor Corporation., CY37128VP84-125JC Datasheet

CY37128VP84-125JC

Specifications of CY37128VP84-125JC

Available stocks

Related parts for CY37128VP84-125JC

CY37128VP84-125JC Summary of contents

Page 1

Features • In-System Reprogrammable™ (ISR™) CMOS CPLDs — JTAG interface for reconfigurability — Design changes do not cause pinout changes — Design changes do not cause timing changes • High density — 512 macrocells — 264 ...

Page 2

Selection Guide 5.0V Selection Guide General Information Device Macrocells CY37032 32 CY37064 64 CY37128 128 CY37192 192 CY37256 256 CY37384 384 CY37512 512 Speed Bins Device 200 167 CY37032 X CY37064 X CY37128 X CY37192 CY37256 CY37384 CY37512 Device-Package Offering ...

Page 3

Speed Bins Device 200 167 CY37032V CY37064V CY37128V CY37192V CY37256V CY37384V CY37512V Shaded areas indicate preliminary speed bins. Device-Package Offering & I/O Count Device CY37032V 37 37 CY37064V CY37128V CY37192V CY37256V CY37384V CY37512V Architecture Overview of Ultra37000 ...

Page 4

FROM PIM PRODUCT TERM ARRAY TO PIM Low-Power Option Each logic block can operate in high-speed mode for critical path performance low-power mode for power conser- vation. The logic block mode is set by ...

Page 5

I/O pin associated with the neighboring macrocell. The output of all buried macrocells is sent directly to the PIM regardless of its configuration. I/O Macrocell Figure 2 illustrates the architecture of ...

Page 6

FROM PTM 0 16 PRODUCT TERMS FROM PTM 0 16 PRODUCT TERMS ASYNCHRONOUS BLOCK RESET 4 SYNCHRONOUS CLOCKS (CLK0,CLK1,CLK2,CLK3) ASYNCHRONOUS 1 ASYNCHRONOUS CLOCK(PTCLK) BLOCK PRESET FROM CLOCK POLARITY MUXES Document #: 38-03007 Rev. *B I/O MACROCELL 0 1 C25 ...

Page 7

INPUT/CLOCK PIN 0 FROM CLOCK 1 O POLARITY INPUT 2 CLOCK PINS Clocking Each I/O and buried macrocell has access to four synchronous clocks (CLK0, CLK1, CLK2 and CLK3) as well as an asynchronous product term clock ...

Page 8

IEEE 1149.1-compliant JTAG The Ultra37000 family has an IEEE 1149.1 JTAG interface for both Boundary Scan and ISR. Boundary Scan The Ultra37000 family supports Bypass, Sample/Preload, Extest, Idcode, and Usercode boundary scan instructions. The JTAG interface is shown in Figure ...

Page 9

Logic Block Diagrams CY37032/CY37032V 16 I/Os I/O I CY37064/CY37064V (100-Lead TQFP) 16 I/Os I/O -I I/Os I/O -I TDI JTAG Tap TCK TDO Controller TMS Document #: 38-03007 Rev. *B Clock/ Input Input ...

Page 10

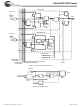

Logic Block Diagrams (continued) CY37128/CY37128V (160-lead TQFP) 16 I/Os I/O –I I/Os I/O –I I/Os I/O –I I/Os I/O –I CY37192/CY37192V (160-lead TQFP) 10 I/Os I/O –I ...

Page 11

Logic Block Diagrams (continued) CY37256/CY37256V (256-lead BGA) 12 I/Os I/O I I/Os I/O I I/Os I/O I I/Os I/O I I/Os I/O I I/Os I/O ...

Page 12

Logic Block Diagrams (continued) CY37384/CY37384V (256-Lead BGA) 12 I/Os I/O I I/Os I/O I I/Os I/O I I/Os I/O I I/Os I/O I I/Os I/O ...

Page 13

Logic Block Diagrams (continued) CY37512/CY37512V (352-Lead BGA) 12 I/Os I/O I I/Os I/O I I/Os I/O I I/Os I/O I I/Os I/O I I/Os I/O ...

Page 14

Device Characteristics Maximum Ratings (Above which the useful life may be impaired. For user guide- lines, not tested.) Storage Temperature .................................–65°C to +150°C Ambient Temperature with Power Applied............................................. –55°C to +125°C Supply Voltage to Ground Potential ............... –0.5V to ...

Page 15

Inductance Parameter Description Conditions L Maximum Pin V IN Inductance MHz [5] Capacitance Parameter Description C Input/Output Capacitance I/O C Clock Signal Capacitance CLK C Dual Function Pins DP [5] Endurance Characteristics Parameter Description N ...

Page 16

Device Electrical Characteristics Parameter Description I Input Bus-Hold HIGH Sustaining BHH Current I Input Bus-Hold LOW Overdrive BHLO Current I Input Bus-Hold HIGH Overdrive BHHO Current [5] Inductance Parameter Description Conditions L Maximum Pin V = 3.3V IN Inductance ...

Page 17

AC Characteristics 3.3V AC Test Loads and Waveforms 295 (COM’L) 393 (MIL) 3.3V OUTPUT 340 (COM’ 453 (MIL) INCLUDING JIG AND SCOPE (a) Equivalent to: THÉVENIN EQUIVALENT 158 (COM’L) 270 (MIL) OUTPUT [11] Parameter ...

Page 18

Switching Characteristics Over the Operating Range Parameter t Clock or Latch Enable Input HIGH Time WH t Input Register or Latch Set-up Time IS t Input Register or Latch Hold Time IH [13, 14, 15] t Input Register Clock or ...

Page 19

Switching Characteristics Over the Operating Range Parameter JTAG Timing Parameters t Set-up Time from TDI and TMS to TCK S JTAG t Hold Time on TDI and TMS H JTAG t Falling Edge of TCK to TDO CO JTAG f ...

Page 20

Switching Characteristics Over the Operating Range 200 MHz 167 MHz 154 MHz Parameter Operating Frequency Parameters f 200 167 MAX1 f 200 200 MAX2 f 125 125 MAX3 f 167 167 MAX4 Reset/Preset Parameters [13] t ...

Page 21

Switching Waveforms (continued) Registered Output with Synchronous Clocking INPUT SYNCHRONOUS CLOCK REGISTERED OUTPUT REGISTERED OUTPUT SYNCHRONOUS CLOCK Registered Output with Product Term Clocking Input Going Through the Array INPUT PRODUCT TERM CLOCK REGISTERED OUTPUT Registered Output with Product Term Clocking ...

Page 22

Switching Waveforms (continued) Latched Output INPUT LATCH ENABLE LATCHED OUTPUT Registered Input REGISTERED INPUT INPUT REGISTER CLOCK COMBINATORIAL OUTPUT CLOCK Clock to Clock INPUT REGISTER CLOCK OUTPUT REGISTER CLOCK Document #: 38-03007 Rev PDL ...

Page 23

Switching Waveforms (continued) Latched Input LATCHED INPUT LATCH ENABLE COMBINATORIAL OUTPUT LATCH ENABLE Latched Input and Output LATCHED INPUT LATCHED OUTPUT INPUT LATCH ENABLE OUTPUT LATCH ENABLE LATCH ENABLE Document #: 38-03007 Rev PDL ...

Page 24

Switching Waveforms (continued) Asynchronous Reset INPUT REGISTERED OUTPUT CLOCK Asynchronous Preset INPUT REGISTERED OUTPUT CLOCK Output Enable/Disable INPUT OUTPUTS Document #: 38-03007 Rev. *B Ultra37000 CPLD Family ...

Page 25

Power Consumption Typical 5.0V Power Consumption CY37032 The typical pattern is a 16-bit up counter, per logic block, with outputs disabled. CY37064 ...

Page 26

Typical 5.0V Power Consumption (continued) CY37128 The typical pattern is a 16-bit up counter, per logic ...

Page 27

Typical 5.0V Power Consumption (continued) CY37256 The typical pattern is a 16-bit up counter, per logic block, with outputs ...

Page 28

Typical 5.0V Power Consumption (continued) CY37512 Typical 3.3V Power Consumption CY37032V ...

Page 29

Typical 3.3V Power Consumption (continued) CY37064V The typical pattern is a 16-bit up counter, per logic block, with outputs disabled. CY37128V ...

Page 30

Typical 3.3V Power Consumption (continued) CY37192V The typical pattern is a 16-bit up counter, per logic block, with outputs disabled. CY37256V ...

Page 31

Typical 3.3V Power Consumption (continued) CY37384V The typical pattern is ...

Page 32

Pin Configurations I/O JTAG CLK Note: 20. For 3.3V versions (Ultra37000V CCO Document #: 38-03007 Rev. *B 44-pin TQFP (A44) Top View /TCK 5 I/O 2 ...

Page 33

Pin Configurations (continued /TCK I I I CLK / CCO GND 22 ...

Page 34

Pin Configurations (continued) 100 99 98 TCK 1 GND CLK / ...

Page 35

Pin Configurations (continued I/O C I/O D I/O E I/O F I/O G I I/O C I/O D I/O E I/O F I/O G I/O H I/O J I/O K ...

Page 36

Pin Configurations (continued) GND I I/O /TCK I GND I/O 25 I/O ...

Page 37

Pin Configurations (continued) GND I I TCK 6 I I GND I ...

Page 38

Pin Configurations (continued) GND I/O 24 TCK 7 8 I GND ...

Page 39

Pin Configurations (continued GND I/O NC I/O I/O I I/O I/O I/O I/O I/O I I/O NC I/O I ...

Page 40

Pin Configurations (continued GND GND I/O I GND I/O I/O I I/O I I/O I/O I I/O I/O I/O I/O 35 ...

Page 41

Pin Configurations (continued GND GND I/O I/O I/O I/O I GND NC I/O I/O I/O I/O I I/O I/O ...

Page 42

Pin Configurations (continued) A GND GND NC I/O I GND GND GND NC I GND GND GND I I/O NC GND I/O I I/O I/O I/O I/O ...

Page 43

Ordering Information Cypress Semiconductor ID Family Type 37 = Ultra37000 Family Macrocell Density Macrocells 256 = 256 Macrocells 64 ...

Page 44

Ordering Information (continued) Macro- Speed cells (MHz) Ordering Code 64 154 CY37064P44-154AC CY37064P44-154JC CY37064P84-154JC CY37064P100-154AC CY37064P44-154AI CY37064P44-154JI CY37064P84-154JI CY37064P100-154AI 5962-9951902QYA 125 CY37064P44-125AC CY37064P44-125JC CY37064P84-125JC CY37064P100-125AC CY37064P44-125AI CY37064P44-125JI CY37064P84-125JI CY37064P100-125AI 5962-9951901QYA 128 167 CY37128P84-167JC CY37128P100-167AC CY37128P160-167AC 125 CY37128P84-125JC CY37128P100-125AC CY37128P160-125AC ...

Page 45

Ordering Information (continued) Macro- Speed cells (MHz) Ordering Code 256 154 CY37256P160-154AC CY37256P208-154NC CY37256P256-154BGC 125 CY37256P160-125AC CY37256P208-125NC CY37256P256-125BGC CY37256P160-125AI CY37256P208-125NI CY37256P256-125BGI 5962-9952302QZC 83 CY37256P160-83AC CY37256P208-83NC CY37256P256-83BGC CY37256P160-83AI CY37256P208-83NI CY37256P256-83BGI 5962-9952301QZC 384 125 CY37384P208-125NC CY37384P256-125BGC 83 CY37384P208-83NC CY37384P256-83BGC CY37384P208-83NI CY37384P256-83BGI ...

Page 46

... CY37064VP100-143AC CY37064VP100-143BBC 100 CY37064VP44-100AC CY37064VP44-100JC CY37064VP48-100BAC CY37064VP84-100JC CY37064VP100-100AC CY37064VP100-100BBC CY37064VP44-100AI CY37064VP44-100JI CY37064VP48-100BAI CY37064VP84-100JI CY37064VP100-100BBI CY37064VP100-100AI 5962-9952001QYA 128 125 CY37128VP84-125JC CY37128VP100-125AC CY37128VP100-125BBC CY37128VP160-125AC 83 CY37128VP84-83JC CY37128VP100-83AC CY37128VP100-83BBC CY37128VP160-83AC CY37128VP84-83JI CY37128VP100-83AI CY37128VP100-83BBI CY37128VP160-83AI 5962-9952201QYA Document #: 38-03007 Rev. *B Ultra37000 CPLD Family Package Name Package Type ...

Page 47

Ordering Information (continued) Macro- Speed cells (MHz) Ordering Code 192 100 CY37192VP160-100AC 66 CY37192VP160-66AC CY37192VP160-66AI 256 100 CY37256VP160-100AC CY37256VP208-100NC CY37256VP256-100BGC CY37256VP256-100BBC 66 CY37256VP160-66AC CY37256VP208-66NC CY37256VP256-66BGC CY37256VP256-66BBC CY37256VP160-66AI CY37256VP256-66BGI CY37256VP256-66BBI 5962-9952401QZC 384 83 CY37384VP208-83NC CY37384VP256-83BGC 66 CY37384VP208-66NC CY37384VP256-66BGC CY37384VP208-66NI CY37384VP256-66BGI ...

Page 48

Package Diagrams Document #: 38-03007 Rev. *B 44-lead Thin Plastic Quad Flat Pack A44 44-Lead Plastic Leaded Chip Carrier J67 Ultra37000 CPLD Family 51-85064-*B 51-85003-*A Page ...

Page 49

Package Diagrams (continued) Document #: 38-03007 Rev. *B 44-Pin Ceramic Leaded Chip Carrier Y67 Ultra37000 CPLD Family 51-80014-** Page ...

Page 50

Package Diagrams (continued) 48-Ball (7 7 1.2 mm, 0.80 pitch) Thin BGA BA48D Document #: 38-03007 Rev. *B Ultra37000 CPLD Family 51-85109-*C Page ...

Page 51

Package Diagrams (continued) Document #: 38-03007 Rev. *B 84-Lead Plastic Leaded Chip Carrier J83 Ultra37000 CPLD Family 51-85006-*A Page ...

Page 52

Package Diagrams (continued) Document #: 38-03007 Rev. *B 84-Pin Ceramic Leaded Chip Carrier Y84 Ultra37000 CPLD Family 51-80095-*A Page ...

Page 53

Package Diagrams (continued) Document #: 38-03007 Rev. *B 100-Pin Thin Plastic Quad Flat Pack (TQFP) A100 Ultra37000 CPLD Family 51-85048-*B Page ...

Page 54

Package Diagrams (continued) 100-Ball Thin Ball Grid Array ( 1.4 mm) BB100 Document #: 38-03007 Rev. *B Ultra37000 CPLD Family 51-8 510 7-*B Page ...

Page 55

Package Diagrams (continued) 160-Pin Thin Plastic Quad Flat Pack ( 1.4 mm) (TQFP) A160 Document #: 38-03007 Rev. *B Ultra37000 CPLD Family 51-85049-*B Page ...

Page 56

Package Diagrams (continued) Document #: 38-03007 Rev. *B 160-Lead Ceramic Quad Flatpack (Cavity Up) U162 Ultra37000 CPLD Family 51-80106-** Page ...

Page 57

Package Diagrams (continued) Document #: 38-03007 Rev. *B 208-Lead Plastic Quad Flatpack N208 Ultra37000 CPLD Family 51-85069-*B Page ...

Page 58

Package Diagrams (continued) 208-Lead Ceramic Quad Flatpack (Cavity Up) U208 Document #: 38-03007 Rev. *B Ultra37000 CPLD Family 51-80105-*A Page ...

Page 59

Package Diagrams (continued) Document #: 38-03007 Rev. *B 256-Ball FBGA ( mm) BB256 Ultra37000 CPLD Family 5 1-85 108 -*C Page ...

Page 60

Package Diagrams (continued) Document #: 38-03007 Rev. *B 388-Lead PBGA ( 2.33 mm) BG388 Ultra37000 CPLD Family 5 1-85 103 -*C Page ...

Page 61

Package Diagrams (continued) Warp is a registered trademark, and In-System Reprogrammable, ISR, Warp Professional, Warp Enterprise, and Ultra37000 are trademarks, of Cypress Semiconductor.ViewDraw and SpeedWave are trademarks of ViewLogic. Windows is a registered trade- mark of Microsoft Corporation. All product ...

Page 62

Addendum 3.3V Operating Range (CY37064VP100-143AC, CY37064VP100-143BBC, CY37064VP44-143AC, CY37064VP48-143B Range Commercial Document #: 38-03007 Rev. *B © Cypress Semiconductor Corporation, 2003. The information contained herein is subject to change without notice. Cypress Semiconductor Corporation assumes no responsibility for the use of ...

Page 63

Document History Page Document Title: Ultra37000 CPLD Family 5V, 3.3V, ISR™ High-Performance CPLDs Document Number: 38-03007 Issue REV. ECN NO. Date ** 106272 04/18/01 *A 124942 03/21/03 *B 126262 05/09/03 Document #: 38-03007 Rev. *B Orig. of Change SZV Change ...