ADP3110KRZ ON Semiconductor, ADP3110KRZ Datasheet

ADP3110KRZ

Available stocks

Related parts for ADP3110KRZ

ADP3110KRZ Summary of contents

Page 1

FEATURES All-in-one synchronous buck driver Bootstrapped high-side drive One PWM signal generates both drives Anticross-conduction protection circuitry Output disable control turns off both MOSFETs to float output per Intel® VRM 10 specification APPLICATIONS Multiphase desktop CPU supplies Single-supply synchronous buck ...

Page 2

... Absolute Maximum Ratings ............................................................4 ESD Caution ..................................................................................4 Pin Configuration and Function Descriptions .............................5 Timing Characteristics .....................................................................6 Theory of Operation.........................................................................7 Low-Side Driver ............................................................................7 High-Side Driver...........................................................................7 REVISION HISTORY 01/08 - Rev 1: Conversion to ON Semiconductor 6/05—Revision 0: Initial Version Overlap Protection Circuit .......................................................... 7 Application Information .................................................................. 8 Supply Capacitor Selection.......................................................... 8 Bootstrap Circuit .......................................................................... 8 MOSFET Selection ....................................................................... 8 PC Board Layout Considerations ............................................... 9 Outline Dimensions ...

Page 3

SPECIFICATIONS BST = 25°C, unless otherwise noted Table 1. Parameter PWM INPUT 2 Input Voltage High Input Voltage Low 2 2 Input Current 2 Hysteresis OD ...

Page 4

ADP3110 ABSOLUTE MAXIMUM RATINGS Table 2. Parameter Rating VCC –0 +15 V BST –0 VCC + 15 V BST to SW –0 + – +15 V <200 ns –10 ...

Page 5

PIN CONFIGURATION AND FUNCTION DESCRIPTIONS Table 3. Pin Function Descriptions Pin No. Mnemonic Description 1 BST Upper MOSFET Floating Bootstrap Supply. A capacitor connected between the BST and SW pins holds this bootstrapped voltage for the high-side MOSFET as it ...

Page 6

ADP3110 TIMING CHARACTERISTICS OD tpdl DRVH OR DRVL IN tpdl DRVL DRVL DRVH-SW SW (Timing is Referenced to the 90% and 10% Points Unless Otherwise Noted) OD 90% Figure 3. Output Disable Timing Diagram tf DRVL tpdh tr DRVH DRVH ...

Page 7

THEORY OF OPERATION The ADP3110 is a dual MOSFET driver optimized for driving two N-channel MOSFETs in a synchronous buck converter topology. A single PWM input signal is all that is required to properly drive the high-side and the low-side ...

Page 8

ADP3110 APPLICATION INFORMATION SUPPLY CAPACITOR SELECTION For the supply input (VCC) of the ADP3110, a local bypass capacitor is recommended to reduce the noise and to supply some of the peak currents drawn. Use a 4.7 μF, low ESR capacitor. ...

Page 9

The MOSFET vendor should provide a maximum voltage slew rate at drain current rating such that this can be designed around. The next step is to determine the expected maximum current in the MOSFET. This can be done by ( ...

Page 10

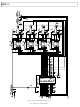

ADP3110 Figure 6. VRD 10.x Compliant Power Supply Circuit Rev Page www.onsemi.com ...

Page 11

... Model Temperature Range 1 ADP3110KRZ 0°C to 85°C 1 ADP3110KRZ-RL 0°C to 85° Pb-free part. ON Semiconductor and are registered trademarks of Semiconductor Components Industries, LLC (SCILLC). SCILLC reserves the right to make changes without further notice to any products herein. SCILLC makes no warranty, representation or guarantee regarding the suitability of its products for any particular purpose, nor does SCILLC assume any liability arising out of the application or use of any product or circuit, and specifically disclaims any and all liability, including without limitation special, consequential or incidental damages. “ ...