M5M4V16169DTP-10 MITSUBISHI, M5M4V16169DTP-10 Datasheet

M5M4V16169DTP-10

Related parts for M5M4V16169DTP-10

M5M4V16169DTP-10 Summary of contents

Page 1

... Preliminary This document is a preliminary Target Spec. and some of the contents are subject to change without notice. DESCRIPTION The M5M4V16169DTP/ 16M-bit Cached DRAM which integrates input 1. registers, a 1,048,576-word by 16-bit dynamic memory array and a 1024- word by 16-bit static RAM array as a Cache memory (block size 8x16) onto a single monolithic circuit ...

Page 2

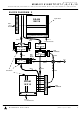

... Mask As9 64 As8 63 As3-9 As7 62 SRAM As6 61 Address input As5 44 As4 43 As3 42 As2 28 As0-2 As1 27 As0 26 MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,-15 Vcc Vss Column Block Decoder 1M bit DRAM Array Sense Amplifier and I/O control Read Buffer1 RB1 ...

Page 3

... Upper Byte DQ0-7 8X16 WB1 Lower Byte Upper Byte 8X16 Block SRAM 1KX16 SRAM Row Decoder As3 - 128 Decode MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,-15 DRAM 1MX16 DRAM Row Decoder Ad0-11 8X16 1 of 4096 Decode RB1 Lower Byte Upper Byte DQ8-15 RB2 As0-2 ...

Page 4

... The unused addresses must be set to Low. 3) Use New BWT or BWTW is initiated the same cycle as DWT1 or DWT1R, new data is loaded into the buffer and transferred to DRAM. 4) Clear Transfer Mask Bits (as addressed by As0-2 and DQCU/L). MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,-15 (SRAM SRAM As address) DQC ...

Page 5

... Data Transferred (max) Din --> SRAM 8/16 bits (5) Din --> WB1 8/16bits (5) SRAM --> WB1 128 bits (8X16bit-block) WB1 --> WB2 128 bits (8X16bit-block) WB2 --> DRAM 128 bits (8X16bit-block) MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,-15 DQ pin Function Din Dout Hi-Z No Operation - SRAM Power Down& Suspend Data retention Byte DRAM Power Down Hi-Z ...

Page 6

... When CMs# is asserted at a rising edge of K, the internal SRAM master clock for CMs# Input the following cycle is suspended, resulting in the power down of the SRAM portion of the circuit, including the Sense Amps. CMs# can also be used to retain output data during SRAM power-down. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,-15 MITSUBISHI LSIs Ad0-Ad11 (@ (REV 1.0) Jul. 1998 6 ...

Page 7

... VccQ is the DQ power supply and allows the device to operate in a mixed voltage system (e.g., 5V data bus). As specified in the Table: Recommended Operating VccQ Supply Conditions, VccQ must be greater-than or equal-to the highest voltage experienced by the data bus. For 3.3V system operation, VccQ may be tied to Vcc. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,-15 MITSUBISHI LSIs (REV 1.0) Jul. 1998 7 ...

Page 8

... Data is written from the I/O pins to the SRAM. Addresses As0-As9 are used to select the location to be written. As3-As9 decode the SRAM Row (=Block), and As0-As2 decode (1of8) the 16-bit word to be written. DQCUu and DQCl control Upper and Lower byte writes, respectively. SRAM Write MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,-15 DRAM 1MX16 Ad3-7 1of32 Decode ...

Page 9

... SRAM Row (=8X16 bit block transferred. Addresses As0-As2 must be set low. The Buffer Write Transfer cycle "clears" all transfer mask bits in the WB1 Mask (allowing all data to be transferred in a successive DRAM Write Transfer cycle). Buffer Write Transfer MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,-15 DRAM Ad3 Decode ...

Page 10

... DRAM Write Transfer cycle). DQCu and DQCl control Upper and Lower byte writes respectively, however all transfer mask bits in the WB1 are cleared. Buffer Write Transfer & SRAM Write 8X16Block MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,-15 DRAM Ad3-7 1of32 Decode DRAM RowDecoder ...

Page 11

... The transfer mask bits associated with the Upper and Lower bytes are cleared in the WB1 Mask. DQCu and DQCl control Upper and Lower byte writes (and associated tranfer mask bits), respectively. Buffer Write 8X16Block MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,-15 DRAM Ad3-7 1of32 Decode ...

Page 12

... Addresses Ad3-Ad7. Addresses Ad8-Ad11 and Ad0-Ad2 must be set to Low. After the Latency Period (specified in the Access Latency Table) new data will be present in the Read Buffer2. Prior to the Latency timeout, old data will be present in the RB2. (Notes 1,2,4) DRAM Read Transfer 8X16Block MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,-15 DRAM Ad3-7 1of32 Decode DRAM RowDecoder ...

Page 13

... WB1 is also transferred to WB2 and controls the data written to the DRAM. The block to which the data is written in DRAM is simultaneously transferred to the Read Buffer.(Notes 2,3,4) DRAM Write Transfer1 & Read 8X16Block MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,-15 DRAM Ad3-7 1of32 Decode DRAM RowDecoder 8X16 ...

Page 14

... DRAM. With the DWT2 function, the WB2 data and WB2 transfer mask remain unchanged. The block to which the data is written in DRAM is simultaneously transferred to the Read Buffer1 and 2. (Notes 1,2,4) DRAM Write Transfer2 & Read 8X16Block MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,-15 DRAM Ad3-7 1of32 Decode DRAM RowDecoder 8X16 ...

Page 15

... Addresses Ad3-Ad7. Addresses Ad8-Ad9 must be set to Low. The Mask present in Byte MaskRegister controls the data written to the DRAM. The block to which the data is written in DRAM is simultaneously transferred to the Read Buffer.(Notes 1,2,4,5) DRAM Write Transfer3 & Read 8X16Block MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,-15 DRAM 256KX16 Ad3-7 1of32 Decode DRAM RowDecoder 8X16 ...

Page 16

... The block to which the data is written in DRAM is simultaneously transferred to the Read Buffer. (Notes 1,2,4,5) Ad3-7 1of32 Decode DRAM Write Transfer4 & Read 8X16Block MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,-15 DRAM 256KX16 DRAM RowDecoder 8X16 8X16 RB1 WB2 Lower Byte DQ0-7 DQ8-15 ...

Page 17

... Note that DNOP / DPD and DES / SPD or NOP command will be the stand-by command for the above power sequence. Vcc must be powered-on at the same time or before VccQ is on. And Vcc must be powered-off at the same time or after VccQ is off. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,-15 MITSUBISHI LSIs (REV 1.0) Jul. 1998 17 ...

Page 18

... DES SR K This outputmode DQC tKHA G# tKLA tKLQX DQ0-15 Registered Output appears from the rising edge of K clock. DES DQC tK tKHAR G# tKHQX DQ0-15 MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- DQC G# tKHQZ Q DQ0-15 SR DES K DQC was deleted. G# tKLQZ Q DQ0-15 DES SR K DQC G# tKHQZ ...

Page 19

... BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM K,K# CMd# CS# RAS# CAS# DTD# CMs# CC0# CC1# WE# DQC ADF# Ad0-11 As0-9 DQ0-15 (Input) MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- CMDS t CSS DTS t CMSS t C0S t C1S DQCS t SADF ...

Page 20

... DQ0 DQ1 DQ2 DQ3 DQ4 DQ5 DQ6 DQ7 DQ8 DQ9 DQ10 DQ11 DQ12 DQ13 DQ14 DQ15 Lower Upper Block address Column Block (16 byte mask, no write 1 : unmask, write enable MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- MITSUBISHI LSIs Upper DQs (REV 1.0) Jul. 1998 20 ...

Page 21

... Lower 8bit Upper8 bit SRAM Byte mask bit DQ0-> Write / Mask logic As0-2 DQCl DQCu WM1 WB1 SRAM MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,-15 DRAM column byte 0 mask Byte WB1/WB2 mask lower byte upper byte ...

Page 22

... Color data is transferred from WB1 through WB2 to DRAM column block with byte mask, which is loaded by Load Byte Mask cycle(LBM). The byte mask data is valid from the LBM cycle immediately and lasts until the next LBM cycle is initiated. Color data is loaded from SRAM cache to WB1.(BWT) MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,-15 DWT4 DNOP DWT4 DNOP ...

Page 23

... K CMs# ADF# CC0# CC1# WE# DQC As0-2 C1 As3- DQ0-15 Q1 DES SR SR SRAM address and DRAM address can be multiplexed using this duration for DRAM control MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- Q1+1 Q1+3 Q1+2 Q2+1 SR DES MITSUBISHI LSIs Accept interrupt for inputting new address w/o gap ...

Page 24

... As3- DQ0-15 Q1 DES SR Burst address is not incremented by DES, SPD. "Insert wait" is possible. M5M4V16169D keeps compatibility setting ADF# low or setting Burst length=1 by SCR cycle. (Ad7, Ad8 and Ad9=0) MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- Q1+1 D1+2 DES SR SPD SPD DES SW SW MITSUBISHI LSIs ...

Page 25

... Vdd=3.3±0.3V for -8,and -10, Vdd=3.3±0.15V for -7 Vss=0V, unless otherwise noted) Symbol Parameter Input Capacitance, Address pin I(A) C Input Capacitance, Clock pin I( Input Capacitance, I/O pin I/O MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,-15 **-15 spec is the same as M5M4V16169TP/RT-15 Conditions With respect to Vss Parameter Supply Voltage Supply Voltage Test Condition V I f=1MHz =25mVrms V I ...

Page 26

... OZ Input Current VOH(AC) and VOL(AC) are the reference levels for AC measurements. VOH(DC) and VOL(DC) are the final levels the outputs reach. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,-15 **-15 spec is the same as M5M4V16169TP/RT-15 Condition data input output open data input output open data input ...

Page 27

... Clock High Pulse Width tKL Clock Low Pulse Width tS Setup Time for Inputs tH Hold Time for Inputs MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,-15 **-15 spec is the same as M5M4V16169TP/RT-15 (CLK pulse, input signals setup / hold time to CLK edge) VIH=3.0V,VIL=0.0V (LVTTL) 1.5V (LVTTL) Limits -7 -8 Max Min ...

Page 28

... Page mode Activate Time tRWL Write to Precharge Lead Time tRSH Read to Precharge Hold Time *Note: When tRP and tRAS = Min. values, tRC and tWC = tRP + tRAS. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,-15 **-15 spec is the same as M5M4V16169TP/RT-15 (Read, Write, Refresh) VIH=3.0V,VIL=0.0V (LVTTL) 1.5V (LVTTL Min. ...

Page 29

... Output Active Time from K-High Edge Output Disable Time from K-High Edge tKHQZR tGLA Access Time from G#-Low Edge tGLQ Output Active Time from G#-Low Edge tGHQ Output Disable Time from G#-High Edge MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,-15 **-15 spec is the same as M5M4V16169TP/RT- Min. Max Min. Max 20 5 ...

Page 30

... SRAM Read/Deselect SRAM/SRAM Write/SRAM Power-down ) CMs# CS# CC0# CC1# WE# DQC As0 As3 DQ0-15 D1 DES SW SR Note : Output is transparent. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- DES SW DES SW SR DRAM operation can be freely performed. MITSUBISHI LSIs ...

Page 31

... K H CMs# L CS# CC0# CC1# WE# DQC As0-2 As3 DQ0-15 DES SR SW Note : Output is transparent. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- SPD SPD DES SPD SR DRAM operation can be freely performed. MITSUBISHI LSIs ...

Page 32

... K CMs# CS# CC0# CC1# WE# DQCu DQCl As0 As3 DQ8- DQ0-7 DES SW SR (u/l) (u/l) Note : Output is transparent. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- DES SW DES SW SR (l) (u) (l) DRAM operation can be freely performed. MITSUBISHI LSIs 10 12 ...

Page 33

... Registered Output control ( SRAM Read/Deselect SRAM/SRAM Write/SRAM Power-down ) CMs# CS# CC0# CC1# WE# DQC As0 As3 DQ0-15 D1 DES SW SR Note : Output is registered. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- DRAM operation can be freely performed. ...

Page 34

... Buffer Read Transfer & SRAM Read (RB2 -> SRAM -> Output CMs# L CS# CC0# CC1# WE# DQC As0-2 As3-9 (C1) (C1 DQ0-15 DES SR BRT Note : Output is transparent. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- (C1) (C1) (C1) (C5) (C5 BRTR DRAM operation can be freely performed. ...

Page 35

... K H CMs# L CS# CC0# CC1# WE# DQC As0-2 As3 WB1(0-7) old DQ0-15 DES BWT DES DES Note : Output is transparent. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- DES BWTW DES DES DRAM operation can be freely performed. MITSUBISHI LSIs ...

Page 36

... K H CMs# L CS# CC0# CC1# WE# DQC As0 As3 WB1(0-7) D1 WB1 Mask(0- DQ0- Note : Output is transparent. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- DES DES DES BW DRAM operation can be freely performed. MITSUBISHI LSIs ...

Page 37

... CS# CC0# CC1# WE# DQC AS0-9 NOP NOP NOP NOP NOP NOP NOP NOP NOP NOP NOP NOP CMd# RAS# DRAM operation can be freely performed. CAS# DTD# Ad0-11 MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- NO-Operation Mode MITSUBISHI LSIs (REV 1.0) Jul. 1998 ...

Page 38

... CAS# DTD# Ad0-11 NOP NOP NOP NOP NOP NOP NOP NOP NOP NOP NOP NOP CMs# CC0# CC1# WE# SRAM operation can be freely performed. DQC(u/l) G# As0-9 DQ0-15 MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- NO-Operation Mode MITSUBISHI LSIs (REV 1.0) Jul. 1998 ...

Page 39

... CAS# DTD# Ad0-11 DPD DPD DPD ACT CMs# CC0# CC1# WE# SRAM operation can be freely performed. DQC(u/l) G# As0-9 DQ0-15 DPD is recommended during no operation to save power. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- Row DNOP DNOP DNOP DNOP MITSUBISHI LSIs PCG DPD DPD DPD DPD (REV 1 ...

Page 40

... RAS# CAS# DTD# Ad0-11 DPD PCG DPD DPD ACT CMs# CC0# CC1# WE# SRAM operation can be freely performed. DQC(u/l) G# As0-9 DQ0-15 MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- tRC tRAS Row DNOP DNOP DNOP DNOP MITSUBISHI LSIs PCG DPD DPD DPD (REV 1 ...

Page 41

... CMs# CC0# CC1# WE# SRAM operation can be freely performed. DQC(u/l) G# As0-9 DQ0-15 MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- tRC DNOP DPD DPD DPD DPD DPD DPD ARF DRAM new commands except for NOP,DNOP and DPD can be set after tRC later from ARF command input. ...

Page 42

... Previous CMd#=H, Present CMd#=L, CS#=RAS#=CAS#=L, DTD#=H (CMd# must remain low to maintain Self Refresh). Self Refresh Exit (in order): a) resume K clock b) CMd#=H c) Wait tRC for recovery d) Resume normal operation MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,-15 4 Inhibit falling edge. H Halt Halt Self Refresh Mode SRAM Power Down Mode Self Refresh ...

Page 43

... CMd# CS# RAS# CAS# DTD# Ad0-2 Ad3-11 RB1 RB2 DRAM DPD DPD SRAM BR BR DQ0-15 Old Old SRAM operation can be freely performed. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- tRC tRP tRCD Row Row Old Data Old Data PCG DPD DPD DPD ACT BR BR ...

Page 44

... RAS# CAS# DTD# Ad0-2 Ad3-9 RB1 RB2 DRAM DPD DPD PCG SRAM DQ0-15 Old Old SRAM operation can be freely performed. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- tRC tRAS tRP tRCD Row Row Old Data Old Data DPD DPD DPD DNOP ACT BR ...

Page 45

... RAS# CAS# DTD# Ad0-2 Ad3-11 RB1 RB2 DRAM DPD DPD PCG SRAM DQ0-15 Old Old SRAM operation can be freely performed. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- tRC tRAS tRP tRCD Row Row Old Data Old Data DPD DPD DPD ACT DNOP BR ...

Page 46

... CMd# CS# RAS# CAS# DTD# Ad0-2 Ad3-11 RB1 RB2 DRAM DPD DPD SRAM BR BR DQ0-15 Old Old SRAM operation can be freely performed. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- tRC tRP tRCD Row Row Old Data Old Data PCG DPD DPD DPD ACT DNOP BR ...

Page 47

... DTD# Row Ad0-2 Row Ad3-11 RB1 Old Data RB2 Old Data DRAM DPD ACT SRAM BR BR DQ0-15 Old Old SRAM operation can be freely performed. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- tRASP tPC tPC Ad0-Ad2=Low **C1 **C2 **C3 tCBF tCBF C2 C1 Latency x t Latency ...

Page 48

... CAS# DTD# Ad0-2 Row Row Ad3-11 RB1 Old Data Old Data RB DRAM DPD ACT SRAM BR BR DQ0-15 Old Old SRAM operation can be freely performed. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- tRASP tPC tPC Ad0-Ad2=Low **C1 **C2 **C3 tCBF tCBF C1 C2 tCBF tCBF C1 DNOP DNOP ...

Page 49

... Row Ad0-2 Row Ad3-11 RB1 Old Data RB2 Old Data DRAM DPD ACT SRAM BR BR DQ0-15 Old Old SRAM operation can be freely performed. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- tRASP tPC Ad0-Ad2=Low **C1 **C2 tCBF tCBF C1 Latency x t Latency DNOP DNOP ...

Page 50

... Row Ad0-2 Row Ad3-11 Old Data RB RB Old Data DRAM DPD ACT DNOP SRAM BR BR Old DQ0-15 Old SRAM operation can be freely performed. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- tRASP tPC Ad0-Ad2=Low **C1 **C2 tCBF tCBF C1 Latency DRT DNOP DNOP DNOP DRT ...

Page 51

... RAS# CAS# DTD# Ad0-2 Ad3-11 WB2 WB1 C0 DRAM DPD DPD SRAM DES BW D0 DQ0-15 D1 Please refer to next page in detail. SRAM operation can be freely performed. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- tRC tRP tRCD Row Row Old Data PCG DPD DPD ...

Page 52

... WB1 mask[2] WB1[3] WB1 masl[3] WB1[4] WB1 mask[4] WB1[5] WB1 mask[5] WB1[6] WB1 mask[6] WB1[7] WB1 mask[7] DPD DPD DRAM DES SRAM BW DQ0- MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- tRC tRP tRCD Row Row Old Data PCG DPD DPD DPD ...

Page 53

... Ad3-11 WB2 WB1 DRAM DPD DPD PCG SRAM DQ0- Please refer to next page in detail. SRAM operation can be freely performed. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- tRC tRP tRAS tRCD Row Row Old Data Old Data DNOP DPD DPD DPD ACT ...

Page 54

... WB1[3] WB1 masl[3] WB1[4] WB1 mask[4] WB1[5] WB1 mask[5] WB1[6] WB1 mask[6] WB1[7] WB1 mask[7] DPD DPD DRAM SRAM SW SW DQ0- MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- tRC tRP tRCD Row Row Old Data PCG DPD DPD DPD ACT ...

Page 55

... RAS# CAS# DTD# Ad0-2 Ad3-11 WB2 WB1 C0 DRAM DPD DPD SRAM DES BW DQ0- Please refer to next page in detail. SRAM operation can be freely performed. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- tRP tRCD Row Row Old Data PCG DPD DPD DPD ...

Page 56

... WB1 mask[2] WB1[3] WB1 masl[3] WB1[4] WB1 mask[4] WB1[5] WB1 mask[5] WB1[6] WB1 mask[6] WB1[7] WB1 mask[7] DPD DPD DRAM DES SRAM BW DQ0- MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- tRP tRCD Row Row Old Data DPD DPD ACT PCG DPD ...

Page 57

... RB1 RB2 Old Data DPD DPD DRAM SRAM DES BW DQ0- New Data on RB appears as to latency set count. See DRT timing chart. SRAM operation can be freely performed. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- tRC tRP tRCD Row Row Old Data ...

Page 58

... K CMd# CS# RAS# CAS# DTD# Ad0-2 Ad3-11 WB2 WB1 0 DRAM DPD DPD PCG SRAM BW DES BW DQ0- SRAM operation can be freely performed. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- tRP tRCD Row Row Old Data DPD DPD DPD ACT DNOP ...

Page 59

... RB1 Old Data DPD DPD DRAM PCG SRAM BW DES BW DQ0- New Data on RB appears as to latency set count. See DRT timing chart. SRAM operation can be freely performed. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- tRP tRCD Row Row Old Data ...

Page 60

... BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM This page is left blank, so that the Set Command Register Timing Diagram on the next spread can be seen conveniently. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,-15 MITSUBISHI LSIs 60 (REV 1.0) Jul. 1998 ...

Page 61

... Set Command Register ( CMd# CS# RAS# CAS# DTD# Ad0-11 DPD DPD DPD DPD DPD DPD MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- CMD SCR DPD DPD DPD ACT *Set Command Reg. Inhibit new command except for DNOP,DPD DES,SPD and NOP. MITSUBISHI LSIs 10 ...

Page 62

... CMd# CS# RAS# CAS# DTD# Ad0~11 Command SCR MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,-15 Ad5 Ad4 Ad3 Ad2 Inhibit new read or write function during these 4 clocks ...

Page 63

... Note: When SRAM command is executed more than burst length, the Address repeats with the same sequence. MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,-15 Sequential ...

Page 64

... BY 16-BIT) CACHED DRAM WITH 16K (1024-WORD BY 16-BIT) SRAM 70P3S Package Dimension 70 70P3S 70P3S 0.65+-0.1 (0.026+-0.004) *2 MITSUBISHI ELECTRIC M5M4V16169DTP/RT-7,-8,-10,- +0.1 0.3 -0.05 +0.004 (0.012 ) -0.05 23.49+-0.1 (0.925+-0.004) 0.1 (0.004) Note) Dimension * not include mold flash. Dimension *3 does not include tie - bar cut remain ...