HYB514265BJ-45 Infineon Technologies AG, HYB514265BJ-45 Datasheet

HYB514265BJ-45

Related parts for HYB514265BJ-45

HYB514265BJ-45 Summary of contents

Page 1

EDO-Dynamic RAM Preliminary Information 262 144 words by 16-bit organization • operating temperature • EDO - Hyper Page Mode • Performance: • -400 -40 - ...

Page 2

Ordering Information Type Ordering Code 5 V versions: HYB 514265BJ-400 Q67100-3033 P-SOJ-40-3 HYB 514265BJ-40 Q67100-3039 P-SOJ-40-3 HYB 514265BJ-45 Q67100-3035 P-SOJ-40-3 HYB 514265BJ-50 Q67100-3036 P-SOJ-40-3 3.3 V versions: HYB 314265BJ-45 on request HYB 314265BJ-50 on request HYB 314265BJL-45 on request HYB ...

Page 3

Pin Configuration (top view) Semiconductor Group HYB 5(3)14265BJ(L)-400/-40/-45/-50 256K x 16 EDO-DRAM P-SOJ-40-3 3 ...

Page 4

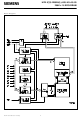

Block Diagram Semiconductor Group HYB 5(3)14265BJ(L)-400/-40/-45/-50 256K x 16 EDO-DRAM 4 ...

Page 5

Absolute Maximum Ratings Operating temperature range ........................................................................................ Storage temperature range..................................................................................... – 150 C Input/output voltage for HYB 514265................................................ – 0.5 to min. ( Power supply voltage for HYB 514265 ........................................................................... – 1 ...

Page 6

Parameter V Average supply current during CC hyper page mode (EDO) operation: -400 version Standby V supply current CC (RAS = LCAS = UCAS = Standby supply current (L-version only) CC (RAS = LCAS = UCAS ...

Page 7

Parameter V Average supply current during CC RAS-only refresh cycles: Average V supply current during hyper page CC mode (EDO) operation: V Standby supply current CC (RAS = LCAS = UCAS = Standby V supply current (L-version ...

Page 8

AC Characteristics Parameter Common Parameters Random read or write cycle time RAS precharge time RAS pulse width CAS pulse width CAS precharge time Row address setup ...

Page 9

Parameter Output buffer turn-off delay from OE Data to OE low delay CAS high to data delay OE high to data delay Data to CAS low delay Write Cycle Write command hold time Write command pulse width Write command setup ...

Page 10

Parameter Hyper Page Mode (EDO) Read-Modify-Write Cycle Hyper page mode read/write cycle time CAS precharge to WE delay time CAS before RAS Refresh Cycle CAS setup time CAS hold time RAS to CAS precharge time Write to RAS precharge time ...

Page 11

AC Characteristics ˚ Parameter Common Parameters Random read or write cycle time RAS precharge time RAS pulse width CAS pulse width CAS precharge time Row address setup time ...

Page 12

AC Characteristics (cont’ ˚ Parameter Output buffer turn-off delay Output turn-off delay from OE Data to CAS low delay Data to OE low delay CAS high to data delay ...

Page 13

AC Characteristics (cont’ ˚ Parameter Hyper Page Mode (EDO) Read-modify-Write Cycle Hyper page mode (EDO) read-write cycle time CAS precharge to WE CAS-before-RAS Refresh Cycle CAS setup time CAS ...

Page 14

and are reference levels for measuring timing of input signals. Transition times are also (min (max measured between and IH 8) Measured with the specified current load and ...

Page 15

Read Cycle Semiconductor Group HYB 5(3)14265BJ(L)-400/-40/-45/-50 256K x 16 EDO-DRAM 15 ...

Page 16

Write Cycle (Early Write) Semiconductor Group HYB 5(3)14265BJ(L)-400/-40/-45/-50 256K x 16 EDO-DRAM 16 ...

Page 17

Write Cycle (OE Controlled Write) Semiconductor Group HYB 5(3)14265BJ(L)-400/-40/-45/-50 256K x 16 EDO-DRAM 17 ...

Page 18

Read-Write (Read-Modify-Write) Cycle Semiconductor Group HYB 5(3)14265BJ(L)-400/-40/-45/-50 256K x 16 EDO-DRAM 18 ...

Page 19

Hyper Page Mode (EDO) Read Cycle Semiconductor Group HYB 5(3)14265BJ(L)-400/-40/-45/-50 256K x 16 EDO-DRAM 19 ...

Page 20

Hyper Page Mode (EDO) Early Write Cycle Semiconductor Group HYB 5(3)14265BJ(L)-400/-40/-45/-50 256K x 16 EDO-DRAM 20 ...

Page 21

Hyper Page Mode (EDO) Late Write and Read-Modify-Write Cycles Semiconductor Group HYB 5(3)14265BJ(L)-400/-40/-45/-50 256K x 16 EDO-DRAM 21 ...

Page 22

RAS-Only Refresh Cycle Semiconductor Group HYB 5(3)14265BJ(L)-400/-40/-45/-50 256K x 16 EDO-DRAM 22 ...

Page 23

CAS-Before-RAS Refresh Cycle Semiconductor Group HYB 5(3)14265BJ(L)-400/-40/-45/-50 256K x 16 EDO-DRAM 23 ...

Page 24

CAS before RAS Self Refresh Cycle Semiconductor Group HYB 5(3)14265BJ(L)-400/-40/-45/-50 256K x 16 EDO-DRAM 24 ...

Page 25

Hidden Refresh Cycle (Read) Semiconductor Group HYB 5(3)14265BJ(L)-400/-40/-45/-50 256K x 16 EDO-DRAM 25 ...

Page 26

Hidden Refresh Cycle (Early Write) Semiconductor Group HYB 5(3)14265BJ(L)-400/-40/-45/-50 256K x 16 EDO-DRAM 26 ...

Page 27

CAS-Before-RAS Refresh Counter Test Cycle Semiconductor Group HYB 5(3)14265BJ(L)-400/-40/-45/-50 256K x 16 EDO-DRAM 27 ...

Page 28

Package Outlines P-SOJ-40-3 (Small Outline J-Leaded Package) Sorts of Packing Package outlines for tubes, trays etc. are contained in our Data Book “Package Information”. SMD = Surface Mounted Device Semiconductor Group HYB 5(3)14265BJ(L)-400/-40/-45/-50 256K x 16 EDO-DRAM 28 Dimensions in ...