SDA5273P Siemens Semiconductor Group, SDA5273P Datasheet

SDA5273P

Specifications of SDA5273P

Available stocks

Related parts for SDA5273P

SDA5273P Summary of contents

Page 1

ICs for Consumer Electronics MEGATEXT and MEGATEXT PLUS ICs SDA 5273 / SDA 5275 SDA 5273-2 / SDA 5275-2 Data Sheet 1997-09-01 ...

Page 2

MEGATEXT and MEGATEXT PLUS ICs SDA 5273 / SDA 5275 SDA 5273-2 / SDA 5275-2 Revision History: Previous Releases: Page Subjects (changes since last revision) 20 Now also covers SDA 5275-2 and SDA 5273-2 versions; Reset/chip initialization update Data Classification ...

Page 3

Contents 1 Features . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . . ...

Page 4

MEGATEXT and MEGATEXT PLUS ICs Preliminary Data 1 Features Single chip teletext IC Analog CVBS-input with onchip clamping circuitry Slicer Supports level 1, 2.5 and 3.5 ETSI teletext standard Stores teletext pages on chip Stores up to ...

Page 5

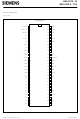

Pin Configuration (top view) CLK- TCSQ/FLD VS/VCS X CVBS V Semiconductor Group P-SDIP-52 OUT 5 XIN 6 GPO SSA 1 V ...

Page 6

Pin Definitions and Functions Pin No. Symbol P-SDIP-52-1 1 CLK-IO 2 TCSQ/FLD 3 VS/VCS XOUT 6 XIN 7 GPO CVBS 10 V DD1 V 11 DDA V 12 SSA1 13 V DD2 14 ...

Page 7

Pin Definitions and Functions (cont’d) Pin No. Symbol P-SDIP-52 SS4 37 CASQ V 38 SS3 SS2 V 41 SSA2 42 RGB-GND V 43 SS1 44 R ...

Page 8

Pin Configuration (top view CVBS DD1 V 12 DDA V 13 SSA1 N. DD2 RES 17 N.C. 18 N. DD3 N. REF ...

Page 9

Pin Definitions and Functions Pin No. Symbol P-LCC-68-1 1 INTQ 2 CLK-IO 3 TCSQ/FLD 4 VS/VCS XOUT 7 XIN 8 GPO CVBS V 11 DD1 V 12 DDA 13 V SSA1 14 N.C. ...

Page 10

Pin Definitions and Functions (cont’d) Pin No. Symbol P-LCC-68 A10 37 A11 38 RASQ 39 WEQ SS4 45 CASQ 46 N.C. 47 ...

Page 11

Pin Definitions and Functions (cont’d) Pin No. Symbol P-LCC-68-1 64 BLAN 65 CORQ 66 SCL 67 SDA CEN Semiconductor Group Function Blanking signal open drain output Contrast reduction open drain output Bidirectional Bus ...

Page 12

Electrical Characteristics Absolute Maximum Ratings Parameter Supply voltage Ambient temperature Storage temperature Power consumption Electrostatic discharge Characteristics Parameter Supply Voltages Supply Currents Inputs Tristate of Outputs CEN, HS, VS, GPO, ...

Page 13

Characteristics (cont‘ Parameter Outputs TTL-Outputs: A0-A11, D0-D3, RASQ, CASQ, WEQ, HS, VS, GPO, INTQ, TCSQ H-output voltage L-output voltage Load capacitance Transition period Open Drain Outputs: BLAN, CORQ Sink current L-output voltage H-output ...

Page 14

Characteristics (cont’ Parameter Output Timing: HS, VS, TCSQ Hold and delay time with respect to 24-MHz system clock output: Delay time Hold time Hold and delay time with respect to 24-MHz external system ...

Page 15

Characteristics (cont’ Parameter RGB-Outputs Pin capacitance Output voltage range RGB-amplitude DC-offset voltage Clamp level DAC-resolution Diff. non-linearity Int. non-linearity Output tracking Output resistance 3-dB bandwidth Bus Connection: SDA, SCL, I Inputs: SDA, SCL ...

Page 16

Characteristics (cont’ Parameter Open Drain Outputs: SDA, SCL L-output voltage Sink current I 2 C-Mode Timing I MEGATEXT C-slave transmitter/receiver. I The Siemens 2 C Bus specification applies. SCL-frequency Transition ...

Page 17

Characteristics (cont’ Parameter M3L-Mode Timing (cont’d) 2 Set-up time SDA to I CEN- rising edge Set up time I 2 CEN to SDA- falling edge I 2 CEN-high time Delay from SCL-falling edge ...

Page 18

Characteristics (cont’ Parameter CVBS-Input and ADC ( V REF Input leakage current Input capacitance Ext. coupling capacitance Sensitivity of clamp level to current leakage/injection ADC-range CVBS-sync amplitude Crystal Oscillator: XIN, XOUT Bias resistance ...

Page 19

Characteristics (cont’ Parameter DRAM-Interface (see diagram 5) The external DRAM is operated in page mode. The timing of the DRAM-interface signals are specified below. Cycle time Address hold time from RAS Address hold ...

Page 20

Characteristics (cont’ Parameter Reset/Chip Initialization A power-on reset or a reset pulse at pin RES lead to a hardware reset and a software initialization of registers and internal DRAM. During initialization bus transfers ...

Page 21

Diagrams t CR CLK Timing Diagram 1 CLK_OUT HS VS Timing Diagram 2 Semiconductor Group SDA 5273 / 75 SDA 5273-2 / 75-2 ...

Page 22

CEN SCL t BUF t SUSTA SDA Timing Diagram C-Bus Mode Semiconductor Group HIGH LOW t SUDAT t HDDAT 22 SDA 5273 / 75 SDA 5273 ...

Page 23

CEN t BUF t IS SCL t DS SDA Wait Condition t SCL Timing Diagram 3b M3L-Bus Mode Semiconductor Group HIGH LOW t DSL DHH DHH t RWAIT DWAIT ...

Page 24

A0... Row Address A11 t WE WEQ D0... RASQ t ASR t CASQ Timing Diagram 4a DRAM-Page Mode Write Cycle Semiconductor Group t WC Column Address t Data from SDA 527x RAH DH ...

Page 25

A0... Row Address A11 t OE WEQ D0... RASQ t ASB t CASQ Timing Diagram 4b DRAM-Page Mode Read Cycle Semiconductor Group t RC Column Address Data from RAM t OFF t CAC t RAH t RASP ...

Page 26

Line Sync Pulse b) Equalizing Pulse 0 4.7 0 2.35 c) Main Pulse 0 VCS 622 623 624 (309) (310) (311) VCS 310 311 312 TCS 622 623 624 (309) (310) (311) TCS 310 311 312 TCS 309 310 ...

Page 27

Line Sync Pulse 0 4.7 b) Equalizing Pulse 0 2.3 c) Main Pulse 0 VCS 522 523 524 (259) (260) (261) VCS 260 261 262 TCS 522 523 524 (259) (260) (261) TCS 260 261 262 TCS 259 260 ...

Page 28

TTL 20.48 MHz 100 nF CVBS 2 Vpp CVBS 11 V DD1 DDA SSA1 DD2 17 RESET ...

Page 29

Package Outlines P-LCC-68-1 (SMD) (Plastic Leaded Chip Carrier) 1.27 0.81 max 0.43 ±0.1 0.18 M A-B D 20. 0.5 x 45˚ 1.1 x 45˚ 24.21 ±0.07 25.28 -0.26 1) Does not include ...

Page 30

Plastic Package, P-SDIP-52-1 (Plastic Dual In-Line Package) 1.78 1.3 max 52 1 Index Marking Sorts of Packing Package outlines for tubes, trays etc. are contained in our Data Book “Package Information”. SMD = Surface Mounted Device Semiconductor Group 0.25 52x ...