MPC9772 Motorola, MPC9772 Datasheet

MPC9772

Available stocks

Related parts for MPC9772

MPC9772 Summary of contents

Page 1

... The MPC9772 also supports the 180° phase shift of one of its output banks with respect to the other output banks. The QSYNC outputs reflects the phase relationship between the QA and QC outputs and can be used for the generation of system baseline timing signals. ...

Page 2

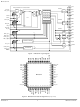

... FB_IN VCO_SEL PLL_EN V CC FSEL_A[0:1] FSEL_B[0:1] FSEL_C[0:1] FSEL_FB[0: INV_CLK STOP_DATA STOP_CLK MR/OE FSEL_B1 FSEL_B0 FSEL_A1 FSEL_A0 VCO_SEL Figure 2. MPC9772 52-Lead Package Pinout (Top View) MOTOROLA 0 Ref ÷2 VCO ÷1 PLL POWER-ON RESET 12 CLOCK STOP Figure 1. MPC9772 Logic Diagram ...

Page 3

... Outputs disabled (high-impedance state) and device is reset. During reset/ output disable the PLL feedback loop is open and the internal VCO is tied to its lowest frequency. The MPC9772 requires reset after any loss of PLL lock. Loss of PLL lock may occur when the external feedback path is interrupted. ...

Page 4

... MPC9772 Table 3. Output Divider Bank A (N VCO_SEL FSEL_A1 FSEL_A0 Table 4. Output Divider Bank B (N VCO_SEL FSEL_B1 FSEL_B0 Table 6. Output Divider PLL Feedback (M) ...

Page 5

... CC_PLL I Maximum Quiescent Supply Current CCQ 1. The MPC9772 is capable of driving 50Ω transmission lines on the incident edge. Each output drives one 50Ω parallel terminated transmission line to a termination voltage Alternatively, the device drives up to two 50Ω series terminated transmission lines Inputs have pull-down resistors affecting the input current. ...

Page 6

... MPC9772 Table 10. AC Characteristics (V CC Symbol Characteristics f Input reference frequency REF Input reference frequency in PLL bypass mode f 4 VCO frequency range VCO f Crystal interface frequency range XTAL f Output Frequency MAX f Serial interface clock frequency STOP_CLK t Input Reference Pulse Width PW,MIN CCLKx Input Rise/Fall Time ...

Page 7

... VCO_SEL) and 10 MHz ≤ XTAL(min, max) VCO(min, max) 5. Calculation of reference duty cycle limits The MPC9772 will operate with input rise/fall times up to 3.0 ns, but the A.C. characteristics, specifically t guaranteed are within the specified range Static phase offset depends on the reference frequency Excluding QSYNC output. See application section for part-to-part skew calculation. 9. Output duty cycle (0.5 ± ...

Page 8

... Table 11 shows the various PLL feedback and output dividers and Figure 3 and Figure 4 display example configurations for the MPC9772: 33.3 MHz MHz ref 100 MHz 200 MHz MPC9772 example configuration (feedback of QFB = 25 MHz, =12, N =4, N =2). f =250 MHz, VCO_SEL=÷1, M=10 VCO = – ...

Page 9

... NRZ disable/enable bits. The period of each STOP_DATA bit equals the period of the free-running STOP_CLK signal. The STOP_DATA serial transmission should be timed so the MPC9772 can sample each STOP_DATA bit with the rising edge of the free-running STOP_CLK signal. (See Figure 5.) ...

Page 10

... QSYNC. In configurations with the output frequency relationships are not integer multiples of each other QSYNC provides a signal for system synchronization purposes. The MPC9772 monitors the relationship between the A bank and the B bank of outputs. The QSYNC output is asserted (logic low) one period in duration and one period prior to the ...

Page 11

... The MPC9772 zero delay buffer supports applications where critical clock signal timing can be maintained across several pin. CC_PLL devices. If the reference clock inputs of two or more MPC9772 are connected together, the maximum overall timing uncertainty from the common CCLKx input to any output is: t ...

Page 12

... Figure 12. “Single versus Dual Transmission Lines” illustrates an output driving a single series terminated line versus two series terminated lines in parallel. When taken to its extreme the fanout of the MPC9772 clock driver is effectively doubled due to its capability to drive multiple lines. ...

Page 13

... Termination Waveforms” show the simulation results of an output driving a single line versus two lines. In both cases the drive capability of the MPC9772 output buffer is more than sufficient to drive 50Ω transmission lines on the incident edge. Note from the delay measurements in the simulations a delta of only 43ps exists between the two differently loaded outputs ...

Page 14

... MPC9772 t SK(O) The pin-to-pin skew is defined as the worst case difference in propagation delay between any similar delay path within a single device Figure 16. Output-to-Output Skew The time from the PLL controlled edge to the non controlled edge, divided by the time between PLL controlled edges, expressed as a percentage Figure 18 ...

Page 15

... S 12.00 BSC 0.472 BSC S1 6.00 BSC 0.236 BSC U 0.09 0.16 0.004 0.006 V 12.00 BSC 0.472 BSC V1 6.00 BSC 0.236 BSC W 0.20 REF 0.008 REF Z 1.00 REF 0.039 REF θ 0˚ 7˚ 0˚ 7˚ θ1 --- --- 0˚ 0˚ θ2 12˚ REF 12˚ REF θ3 12˚ REF 12˚ REF MPC9772 MOTOROLA ...

Page 16

... P.O. Box 5405, Denver, Colorado 80217 1-800-521-6274 or 480-768-2130 JAPAN: Motorola Japan Ltd.; SPS, Technical Information Center 3-20-1 Minami-Azabu. Minato-ku, Tokyo 106-8573, Japan ASIA/PACIFIC: Motorola Semiconductors H.K. Ltd.; Silicon Harbour Centre 2 Dai King Street, Tai Po Industrial Estate, Tai Po, N.T., Hong Kong HOME PAGE: http://motorola.com/semiconductors 81-3-3440-3569 852-26668334 MPC9772 ...