S-93C56BD0H-J8T2G Seiko, S-93C56BD0H-J8T2G Datasheet

S-93C56BD0H-J8T2G

Available stocks

Related parts for S-93C56BD0H-J8T2G

S-93C56BD0H-J8T2G Summary of contents

Page 1

... SOP(JEDEC) 8-Pin TSSOP SNT-8A Caution This product is intended to use in general electronic devices such as consumer electronics, office equipment, and communications devices. Before using the product in medical equipment or automobile equipment including car audio, keyless entry and engine control unit, contact to SII is indispensable. ...

Page 2

... DO Figure 1 S-93C46BD0I-D8S1G S-93C56BD0I-D8S1G S-93C66BD0I-D8S1G 8-Pin SOP(JEDEC) Top view VCC TEST GND Figure 2 S-93C46BD0I-J8T1G S-93C46BD0H-J8T2G S-93C56BD0I-J8T1G S-93C56BD0H-J8T2G S-93C66BD0I-J8T1G S-93C66BD0H-J8T2G 2 Table 1 Pin No. Symbol GND *1 6 TEST VCC *1. Connect to GND Even if this pin is not connected, performance is not affected so long as the absolute maximum rating is not exceeded ...

Page 3

... S-93C56BD0H-T8T2G S-93C66BD0I-T8T1G S-93C66BD0H-T8T2G Pin No. Symbol *1. Connect to GND or V Even if this pin is not connected, performance is not affected so long as the absolute maximum rating is not exceeded. Remark See Dimensions for details of the package drawings. Pin No. Symbol 1 VCC NC 2 TEST 3 GND 4 5 ...

Page 4

... TEST VCC *1. Connect to GND Even if this pin is not connected, performance is not affected so long as the absolute maximum rating is not exceeded. Remark See Dimensions for details of the package drawings. Seiko Instruments Inc. Rev.4.3 Table 5 Description Chip select input Serial clock input ...

Page 5

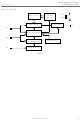

... Rev.4.3 _00 Block Diagram Address Memory array decoder Data register Mode decode logic Clock pulse Voltage detector monitoring circuit Clock generator Figure 6 Seiko Instruments Inc. 2 CMOS SERIAL E PROM S-93C46B/56B/66B VCC GND Output buffer DO 5 ...

Page 6

... WRITE (Write data) ERASE (Erase data) WRAL (Write all) ERAL (Erase all) EWEN (Write enable) EWDS (Write disable) *1. When the 16-bit data in the specified address has been output, the data in the next address is output. Remark x: Don’t care 6 Table 6 Operation Code ...

Page 7

... WRITE (Write data) ERASE (Erase data) WRAL (Write all) ERAL (Erase all) EWEN (Write enable) EWDS (Write disable) *1. When the 16-bit data in the specified address has been output, the data in the next address is output. Remark x: Don’t care Table 8 Operation Start Bit Code ...

Page 8

... Power supply voltage Input voltage Output voltage Operating ambient temperature Storage temperature Caution The absolute maximum ratings are rated values exceeding which the product could suffer physical damage. These values must therefore not be exceeded under any conditions. Recommended Operating Conditions Item ...

Page 9

... DC Electrical Characteristics Item Symbol Conditions Current consumption load CC1 (READ) Item Symbol Current consumption I CC2 (WRITE) Item Symbol Conditions CS = GND Open, Standby current Other inputs to I consumption GND CC Input leakage = GND current LI Output leakage = GND ...

Page 10

... SKH Output disable time HZ1 HZ2 Output enable time t SV *1. The clock cycle of the SK clock (frequency several AC characteristics aware that even if the SK clock cycle time is minimized, the clock cycle (1/f ) cannot be made equal Item Symbol Write time Table 16 Measurement Conditions 0.1 × ...

Page 11

... Hi (READ) Hi-Z DO (VERIFY) *1. Indicates high impedance. *2. 1/f is the SK clock cycle. This clock cycle is determined by a combination of several AC SK characteristics aware that even if the SK clock cycle time is minimized, the clock cycle (1/f ) cannot be made equal 1 SKH SKL ...

Page 12

... CDS inputs are invalid and no instructions are allowed. Start Bit A start bit is recognized when the DI pin goes high at the rise of SK after CS goes high. After CS goes high, a start bit is not recognized even if the SK pulse is input as long as the DI pin is low. 1. Dummy clock SK clocks input while the DI pin is low before a start bit is input are called dummy clocks ...

Page 13

... After CS has gone high, input an instruction in the order of the start bit, read instruction, and address. Since the last input address (A impedance (Hi-Z) to low, which is held until the next rise of SK. 16-bit data starts to be output in synchronization with the next rise of SK Sequential read ...

Page 14

... Caution 1. Input a low level to the DI pin during a verify operation high level is input to the DI pin at the rise of SK when the output status of the DO pin is high, the S-93C46B/56B/66B latches the instruction assuming that a start bit has been input. In this case, note that the DO pin immediately enters a high-impedance (Hi-Z) state ...

Page 15

... The write operation starts when CS goes low. There is no need to set the data to 1 before writing. If the clocks more than the specified number have been input, the clock pulse monitoring circuit cancels the WRITE instruction. For details of the clock pulse monitoring circuit, refer to “ ...

Page 16

... S-93C46B/56B/66B 4. 3 Erasing data (ERASE) To erase 16-bit data at a specified address, set all 16 bits of the data to 1, change CS to high, and then input the ERASE instruction and address following the start bit. There is no need to input data. The data erase operation starts when CS goes low. If the clocks more than the specified number have been input, the clock pulse monitoring circuit cancels the ERASE instruction. For details of the clock pulse monitoring circuit, refer to “ ...

Page 17

... WRAL instruction, an address, and 16-bit data following the start bit. Any address can be input. The write operation starts when CS goes low. There is no need to set the data to 1 before writing. If the clocks more than the specified number have been input, the clock pulse monitoring circuit cancels the WRAL instruction. For details of the clock pulse monitoring circuit, refer to “ ...

Page 18

... S-93C46B/56B/66B 4. 5 Erasing chip (ERAL) To erase the data of the entire memory address space, set all the data to 1, change CS to high, and then input the ERAL instruction and an address following the start bit. Any address can be input. There is no need to input data. The chips erase operation starts when CS goes low. If the clocks more than the specified number have been input, the clock pulse monitoring circuit cancels the ERAL instruction. For details of the clock pulse monitoring circuit, refer to “ ...

Page 19

... The EWDS instruction is an instruction that disables a write operation. The status in which a write operation is disabled is called the program disable mode. After CS goes high, input an instruction in the order of the start bit, EWEN or EWDS instruction, and address (optional). Each mode becomes valid by inputting a low level to CS after the last address (optional) has been input ...

Page 20

... ERASE, WRAL, and ERAL) are cancelled, and the write disable state (EWDS) is automatically set. The detection voltage is 1.75 V typ., the release voltage is 2.05 V typ., and there is a hysteresis of about 0.3 V (refer to Figure 20 ). Therefore, when a write operation is performed after the power supply voltage has dropped and then risen again up to the level at which writing is possible, a write enable instruction (EWEN) must be sent before a write instruction (WRITE, ERASE, WRAL, or ERAL) is executed ...

Page 21

... The S-93C46B/56B/66B provides a built-in clock pulse monitoring circuit which is used to prevent an erroneous write operation by canceling write instructions (WRITE, ERASE, WRAL, and ERAL) recognized erroneously due to an erroneous clock count caused by the application of noise pulses or double counting of clocks. Instructions are cancelled if a clock pulse more or less than specified number decided by each write operation (WRITE, ERASE, WRAL, or ERAL) is detected. < ...

Page 22

... To prevent such a malfunction, connect the DI and DO pins of the S-93C46B/56B/66B via a resistor (10 to 100 kΩ) so that the data output from the CPU takes precedence in being input to the DI pin (refer to “ Figure 22 Connection of 3-Wire Interface ”). ...

Page 23

... Rev.4.3 _00 2. 1 Input pin CS SK, DI TEST Figure 23 CS Pin Figure 24 SK, DI Pin Figure 25 TEST Pin Seiko Instruments Inc. 2 CMOS SERIAL E PROM S-93C46B/56B/66B 23 ...

Page 24

... Input pin noise elimination time The S-93C46B/56B/66B include a built-in low-pass filter to eliminate noise at the SK, DI, and CS pins. This means that if the supply voltage is 5.0 V (at room temperature), noise with a pulse width less can be eliminated. Note, therefore, the noise with a pulse width of more than 20 ns will be recognized as a pulse if the ...

Page 25

... Ta (° Current consumption (READ) I vs. ambient temperature 1 kHz f SK DATA = 0101 0.4 I CC1 (mA) 0.2 0 − (° Current consumption (READ) I vs. power supply voltage 25°C = 100 kHz, 10 kHz f SK DATA = 0101 0.4 I CC1 (mA) 100 kHz 0.2 10 kHz ...

Page 26

... Ta (° Current consumption (WRITE) I vs. ambient temperature 1.0 I CC2 (mA) 0.5 0 − (° Current consumption in standby mode I vs. ambient temperature GND 1 (µA) 0.5 0 − (° Current consumption (WRITE) I CC2 vs. ambient temperature ...

Page 27

... Ta (° Input leakage current Output leakage current High-level output voltage Seiko Instruments Inc. CMOS SERIAL E S-93C46B/56B/66B LI vs. ambient temperature CS, SK, DI, TEST = 5 (µA) 0.5 0 − (°C) LO vs. ambient temperature 5 5 (µ ...

Page 28

... −20 (mA) −10.0 0 − (° High-level output voltage V OH vs. ambient temperature Low-level output voltage V OL vs. ambient temperature High-level output current I OH vs. ambient temperature Ta 85 Seiko Instruments Inc. Rev.4 1 −10 µA OH 1.9 V 1.8 OH (V) 1.7 − ...

Page 29

... Low-level output current I vs. ambient temperature (mA − (° Input inverted voltage V vs. power supply voltage 25°C CS, SK, DI 3.0 V INV ( High-level output current Low-level output current I ...

Page 30

... CMOS SERIAL E PROM S-93C46B/56B/66B 1. 31 Low supply voltage detection voltage −V vs. ambient temperature Ta 2.0 −V DET (V) 1.0 0 − (° Low supply voltage release voltage +V DET vs. ambient temperature Ta 85 Seiko Instruments Inc. Rev.4.3 2.0 +V DET (V) 1.0 0 − (°C) _00 DET ...

Page 31

... Ta (° Write time t MAX ( Write time Data output delay time t 85 Seiko Instruments Inc. CMOS SERIAL E S-93C46B/56B/66B PR vs. power supply voltage 25° (ms ( vs. ambient temperature ...

Page 32

... CMOS SERIAL E PROM S-93C46B/56B/66B 2. 7 Data output delay time t vs. ambient temperature (µs) 0.4 0.2 − (° Data output delay time Seiko Instruments Inc. PD vs. ambient temperature (µs) 1.0 0.5 − (°C) Rev.4.3 _00 ...

Page 33

... T8T1: 8-Pin TSSOP, Tape T8T2: 8-Pin TSSOP, Tape, +105°C Max. supported I8T1: SNT-8A, Tape Operation temperature I: −40 to +85°C H: −40 to +105°C (Only 8-Pin SOP(JEDEC) , 8-Pin TSSOP) Fixed Pin assignment D: 8-Pin DIP 8-Pin SOP(JEDEC) 8-Pin TSSOP SNT-8A R: 8-Pin SOP(JEDEC) (Rotated) ...

Page 34

...

Page 35

...

Page 36

...

Page 37

...

Page 38

...

Page 39

...

Page 40

...

Page 41

...

Page 42

...

Page 43

...

Page 44

...

Page 45

... Use of the information described herein for other purposes and/or reproduction or copying without the express permission of Seiko Instruments Inc. is strictly prohibited. The products described herein cannot be used as part of any device or equipment affecting the human body, such as exercise equipment, medical equipment, security systems, gas equipment, or any apparatus installed in airplanes and other vehicles, without prior written permission of Seiko Instruments Inc ...