CS6422-CSZ Cirrus Logic Inc, CS6422-CSZ Datasheet

CS6422-CSZ

Specifications of CS6422-CSZ

Available stocks

Related parts for CS6422-CSZ

CS6422-CSZ Summary of contents

Page 1

... The CS6422 enables full-duplex conversation using echo cancellation and suppression in a single-chip solu- tion. The CS6422 can easily replace existing half-duplex speakerphone ICs with a huge increase in conversation quality. The CS6422 consists of telephone & audio interfaces, two codecs and an echo-cancelling DSP ...

Page 2

... Cirrus Logic, Inc. The names of products of Cirrus Logic, Inc. or other vendors and suppliers appearing in this document may be trademarks or service marks of their respective owners which may be registered in some jurisdictions. A list of Cirrus Logic, Inc. trade- marks and service marks can be found at http://www.cirrus.com CS6422 CS6422 DS295F1 ...

Page 3

... Algorithmic Considerations .............................................................................................. 31 4.1.1 Full-Duplex Mode ................................................................................................ 31 4.1.1.1 Theory of Operation ........................................................................... 31 4.1.1.2 Adaptive Filter ..................................................................................... 32 4.1.1.2.1 Pre-Emphasis ............................................................................ 32 4.1.1.2.2 Graded Beta .............................................................................. 33 4.1.1.3 Update Control .................................................................................... 33 4.1.1.4 Speech Detection ................................................................................ 33 4.1.2 Half-Duplex Mode ............................................................................................... 34 4.1.2.1 Idle Return to Transmit ....................................................................... 34 4.1.3 AGC .................................................................................................................... 34 4.1.4 Suppression ........................................................................................................ 35 4.1.4.1 Transmit Suppression ......................................................................... 36 4.1.4.2 Receive Suppression .......................................................................... 36 DS295F1 CS6422 CS6422 3 3 ...

Page 4

... LIST OF TABLES Table 1. Full scale voltages for each gain stage ........................................................................... 11 Table 2. MCR Control Register Mapping ...................................................................................... 12 Table 3. Register 0 Bit Definitions................................................................................................. 13 Table 4. Register 1 Bit Definitions................................................................................................. 16 Table 5. Register 2 Bit Definitions................................................................................................. 18 Table 6. Register 3 Bit Definitions................................................................................................. 21 Table 7. Register 4 Bit Definitions................................................................................................. 23 Table 8. Register 5 Bit Definitions................................................................................................. CS6422 CS6422 DS295F1 ...

Page 5

... Commercial T AOp Industrial (T = 25°C, DVDD = AVDD = Symbol P DA0 DD0 25°C, DVDD = AVDD = Symbol (Note 2) (Note load CS6422 CS6422 Min Max Units -0.3 6.0 V -10 +10 mA -0.3 AVDD+0.3 V -0.3 DVDD+0.3 -40 85 °C -65 150 °C Min Typ Max Units 4.5 5.0 5.5 ...

Page 6

... SNR THD RGain/TGain = 00 RGain/TGain = 01 RGain/TGain = 10 RGain/TGain = 25°C, DVDD = AVDD = Symbol A mic SNRm Z inm V offm (T = 25°C, DVDD = AVDD = 5 V,f A Symbol leak C IN CS6422 CS6422 = 25°C, DVDD = AVDD = XTAL Min Typ Max Units -80 -73 dBV 11 dBrnC0 -78 dBm0p 0.030 0 9 0.9 1.0 V rms 1 ...

Page 7

... SNR THD RGain/TGain = 00 RGain/TGain = 01 RGain/TGain = 10 RGain/TGain = 25°C, DVDD = AVDD = Symbol A mic SNRm Z inm V offm (T = 25°C, DVDD = AVDD = 5 V,f A Symbol leak C IN CS6422 CS6422 o = -40° DVDD = AVDD = 5 V, Min Typ Max Units -80 -72 dBV 11 dBrnC0 -78 dBm0p 0.030 0 9 0.9 1.0 ...

Page 8

... Figure 1. CLKI Timing t cRST t wRST Bit15 Bit14 Bit2 Bit1 Bit0 Figure 2. Reset Timing t DRDY t sDRDY t hDRDY t sDATA t hDATA Bit15 Bit14 Bit0 Figure 3. Microcontroller Interface Timing CS6422 CS6422 Min Typ Max 1.0 1.0 20.480 19.5 125 110 100 four extra strobe pulses ...

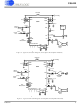

Page 9

... STROBE 12.1 kΩ DRDY AO 5 RST 3300pF NC4 NC3 NC2 NC1 CLKI CLKO 20.480 MHz 22pF 22pF CS6422 CS6422 +5V Analog 0.1 µ µ 0.1 µF 10 µ Mic Bias 18 0.022 µ F 0.47 µF 20 12.1 kΩ 3 3300pF Speaker Driver +5V Analog 0.1 µ µ F 0.47 µ ...

Page 10

... Full-duplex for hands-free communications is achieved in the CS6422 using a digital signal pro- cessing technique called “Echo Cancellation.” The end result is a more natural conversation than half- duplex, with no awkward breaks and pauses, allow- ing both parties to speak simultaneously ...

Page 11

... APO should be driven directly. In this case, the signal into APO must be low-pass filtered by a single-pole RC filter with a corner frequency at 8 kHz (see Figure 5). Following the pre-amplifier is a programmable an- alog gain stage, called TGain, which is controlled CS6422 CS6422 AO 3 NEAR-END API Mic 1kΩ ...

Page 12

... Interface. The details of the Network Inter- face are shown in Figure the input from the telephone network into the CS6422. The signal into NI must be low pass fil- tered by a single-pole RC filter with a corner fre- quency of 8 kHz. RGain, a programmable analog gain stage accessi- ble through the Microcontroller Interface, ampli- fies signals received at NI ...

Page 13

... STROBE pulses must be applied to latch the data into the CS6422. Since the MCR is a shift register, the STROBE can be run arbitrarily slowly with a duty cycle limited only by the minimum high and low time specified in “Switching Characteristics”. The Microcontrol- ler Interface is polled at 125 µs intervals, so regis- ter writes must be spaced at least 125 µ ...

Page 14

... Table 3. Register 0 Bit Definitions CS6422 CS6422 TSMde Operation disable mic preamp enable mic preamp enable half-duplex disable half-duplex 0.00 dB/ms 0.75 dB/ms 0.38 dB/ms 0.19 dB/ms +30 dB +27 dB --- +18 dB --- + --- ...

Page 15

... HDD - HALF-DUPLEX DISABLE In normal operation, the CS6422 will half-duplex mode if the echo canceller is not providing enough loop gain reduction to prevent howling. This half-duplex mode is active at power-up while the adaptive filter begins to train. Half-duplex mode prevents howling and also masks the convergence process. In some cases, such as when measuring convergence speed (see Section 4.3.2, “ ...

Page 16

... ACC - ACOUSTIC COEFFICIENT CONTROL The coefficients of the AEC adaptive filters in the CS6422 are controlled by ACC. The default position (00) yields normal operation, which means the coefficients are free to adjust themselves to the echo path in order to cancel echo. When set to the clear position (01), the adaptive filter coefficients are all held at zero, so the echo canceller is effectively disabled ...

Page 17

... A Function Word 00* threshold 10* 11 0000 0001 --- 0100 --- 1010* 1011 --- 1101 1110 1111 Table 4. Register 1 Bit Definitions CS6422 CS6422 AuNECD Operation reserved 444/64 (55.5 ms/8 ms) 380/128 (47.5 ms/16 ms) 316/192 (39.5 ms/24 ms) 252/256 (31.5 ms/32 ms) +30 dB +27 dB --- +18 dB --- + --- -9 dB -12 dB mute enable Rx suppression ...

Page 18

... TAPS - AEC/NEC TAP ALLOCATION The CS6422 has a total of 63 echo canceller taps that it can partition for use by the network and acoustic echo cancellers. By default, the CS6422 allocates 39.5 ms for the AEC and 24 ms for the NEC. See NErle, NFNse, AErle, and AFNse in Register 4, and AECD and NECD in Register 5 for more options when an echo path is nonexistent ...

Page 19

... Rx Double-talk Suppression Ramp rate 4 IdlTx * Denotes reset value DS295F1 b10 HDly HHold TDSRmp RDSRmp Function Rx Half-duplex Detection threshold Rx Suppression Threshold Noise estimator Ramp rate half-duplex Holdover Delay Hold in half-duplex on Howl half-duplex Idle return-to-Transmit Table 5. Register 2 Bit Definitions CS6422 CS6422 IdlTx Word Operation 00 reserved 00 ...

Page 20

... This is a control flag which, if enabled, holds the system in half-duplex when a howl event is detected. The system may transition to full-duplex if the flag is subsequently cleared. The default state of HHold is ‘disabled’, thus when a howl is detected, the CS6422 will temporarily drop into half-duplex, retrain, and transition back into full-duplex on its own. ...

Page 21

... RDSRMP - RX DOUBLE-TALK SUPPRESSION RAMP RATE When “Rx Double-talk Suppression attenuation” (RDbtS, Register 3) is set to a non-zero value, the CS6422 will introduce a programmable amount of attenuation into the receive path during a double- talk event. RDSRmp controls the decay rate of the receive double-talk attenuation (the attack rate is ~40 ms). The ‘ ...

Page 22

... TSThd 5-4 TSBias * Denotes reset value 22 22 b10 RDbtS TSThd Function Tx Suppression Attenuation Path Change Sensitivity Tx Double-talk Suppression attenuation Rx Double-talk Suppression attenuation Tx Suppression Threshold Tx Suppression Bias Table 6. Register 3 Bit Definitions CS6422 CS6422 TSBias Word Operation 00 reserved 0* high sensitivity 1 low sensitivity 000* ...

Page 23

... When PCSen is set to ‘1’ for low sensitivity, the CS6422 will tend to remain in full-duplex during the path change, and the far-end listener may hear some residual echo as the adaptive filter adjusts to the new path ...

Page 24

... NFNse NEC Full-duplex Noise threshold 7-6 RGain 5-4 TGain * Denotes reset value 24 24 b10 NErle NFNse RGain Function AEC Erle threshold NEC Erle threshold Rx analog Gain Tx analog Gain Table 7. Register 4 Bit Definitions CS6422 CS6422 TGain Word Operation 00 reserved 00* zero 01 - -54 dB ...

Page 25

... NFNse works in conjunction with NErle to determine when the CS6422 should transition into full-du- plex operation. If the noise level at the far-end input is greater than NFNse, then NErle is used to de- termine if full-duplex is allowed. If the noise level is below the level of NFNse, the CS6422 uses an internal estimate of asymptotic performance to determine whether or not to transition to full-duplex. If NFNse is zero, NErle is always used as the exclusive full-duplex criterion ...

Page 26

... NSdt * Denotes reset value 26 26 b11 b10 Function Howl detector Disable Tone detector Disable Acoustic Sidetone level Network Sidetone level Table 8. Register 5 Bit Definitions CS6422 CS6422 ASdt NSdt Word Operation 0* enable howl detector 1 disable howl detector 0* enable tone detector 1 disable tone detector ...

Page 27

... CS6422 is in half-duplex mode, the tone detector will clear the AEC coefficients and force the half- duplex engine into <Receive> mode to allow the tone to pass through, independent of the presence of signals at the near-end microphone. If the CS6422 is in full-dulpex mode when a tone is detected, the tone detector will momentarily freeze the AEC coefficients to prevent false training. 3.8.3 APCD - ACOUSTIC PATH CHANGE DETECTOR DISABLE This diagnostic bit is normally set to ‘ ...

Page 28

... This control allows the introduction of a linear coupling path for the NEC to train on. The real network path is superimposed on this path and both are cancelled by the NEC. The use of a network sidetone is beneficial in environments where the real network path is faint or distorted. This control is usually set to ‘none’ CS6422 CS6422 DS295F1 ...

Page 29

... Warm reset is like cold reset except that the echo canceller coefficients and certain key variables are not cleared, but instead keep their pre-reset value. This gives the CS6422 a headstart in adapting to its environment if the echo environment is relatively stable, assuming a cold reset occurred at least once since power up ...

Page 30

... The three best methods to reduce noise when using the CS6422 are to properly decouple the power supplies, to separate the system analog and digital power and ground (all power and ground pins of the CS6422 should tie to the analog power supply), and to route signals on the board carefully. AGND MB ...

Page 31

... F DS295F1 from digital, as shown in Figure 9. The ferrite bead serves as a low-pass filter to remove CS6422 digi- tal switching noise from the analog power supply. The ground is separated by isolating all the digital components of the system board on one ground plane and all the analog and linear components on a different ground plane ...

Page 32

... DESIGN CONSIDERATIONS When designing the CS6422 into a system im- portant to keep several considerations in mind. These concerns can be loosely grouped into three categories: algorithmic considerations, circuit de- sign considerations, and system design consider- ations. 4.1 Algorithmic Considerations The CS6422 facilitates full-duplex hands-free communication via many algorithms running on the Digital Signal Processor that is the core of the CS6422 ...

Page 33

... Since this does not work for the CS6422, an AGC mechanism has been introduced to provide equiva- lent behavior without clipping. See Section 4.1.3, “ ...

Page 34

... The CS6422 works very well with a speech training signal because of the pre-emphasis filter. White noise training signals, however, result in sub-opti- mal performance, so when testing with white noise recommended that the pre-emphasis filters be disabled ...

Page 35

... This duration is dependent upon the power difference between the signal and the ambient noise power, as well as NseRmp. It should be noted that the CS6422 has a tone detector to prevent updates when tones are present and allow tones to persist regardless of the speech detectors. ...

Page 36

... The CS6422 employs supplementary echo suppres- sion which adds attenuation on top of the cancella- tion to remove the residual echo. For example, the CS6422 will engage extra attenuation in the trans- mit path whenever only the far-end talker is speak- ing. However, if the near-end talker starts speaking, this attenuation is removed and the system relies on the near-end talker’ ...

Page 37

... As a result, it may be desirable to limit the suppression attenuation to the minimum necessary. The CS6422 provides TSAtt (Register 3, bits 15 and 14) to control the amount of attenua- tion introduced by suppression in the transmit channel. Receive suppression attenuates by 24 dB. ...

Page 38

... Microcontroller Interface The Microcontroller Interface is the only asynchro- nous digital connection to the CS6422 the most likely place for digital noise coupling problem. The interface itself is fairly straightfor- ward and requires only three pins from a microcon- troller. ...

Page 39

... The decoupling capacitors for the power supplies of the CS6422 should be placed as close as possible to the power pins for best performance. There are two capacitors per pin: the 0.1 µF capacitor needs ...

Page 40

... ERLE of the Acoustic Canceller, the NO output should be disconnected from the rest of the net- work. This will prevent feedback which could oc- cur when all of the CS6422’s failsafes are disabled. The following example outlines the steps necessary to measure the ERLE of the acoustic echo cancel- ler ...

Page 41

... Set the CS6422 Microcontroller Interface to the nominal register values for the system, but clear the acoustic and network echo canceller coefficients. This will force the CS6422 to remain in half-duplex mode. The most useful test of practical performance found at Crystal has been the “alternating counting test.” ...

Page 42

... TGain Microphone Bias Voltage Output, Pin 19 Output of 3.5 VDC provides the internal voltage reference for the CS6422. MB must be decoupled with a 10 µF and 0.1 µF capacitor to prevent noise from affecting the on-chip voltage reference. MB must not be connected to any load. ...

Page 43

... Microcontroller Interface RST - Active Low Reset Input, Pin 5 When RST is held low, the CS6422 is put into a low power mode with all functional blocks idle. When RST goes high, the CS6422 is started in a known state. DRDY - Active Low Microcontroller Interface Data Ready Input, Pin 6 DRDY is a low pulse used to gate valid input data into the Microcontroller Interface ...

Page 44

... Miscellaneous NC1 - No Connect, Pin 9 Must be floating for normal operation. NC2 - No Connect, Pin 10 Must be floating for normal operation. NC3 - No Connect, Pin 11 Must be floating for normal operation. NC4 - No Connect, Pin 12 Must be floating for normal operation CS6422 CS6422 DS295F1 ...

Page 45

... This happens when the coupling between the speaker and microphone is strong enough to increase the system's closed loop gain above unity. Acoustic Coupling The strength of the output signal from the speaker that is received at the microphone input. DS295F1 CS6422 CS6422 45 45 ...

Page 46

... The larger the value for ERLE, the better the echo cancellation. Coverage Time The CS6422 echo canceller has 508 taps and it can sample an analog signal kHz rate. 512 x 1/8 kHz = 63.5 ms. Sound travels through air at a rate of around 1 ft/ms. Thus the echo canceller can be used in a room with walls 32 feet away, discounting multiple reflections ...

Page 47

... JEDEC #: MS-013 Controlling Dimension is Inches/Chip Pac Controlling Dimension is Millimeters/Jedec CS6422 CS6422 MILLIMETERS MIN NOM MAX 2.35 2.50 2.65 0.10 0.20 0.30 0.33 0.43 0.51 0.23 ...

Page 48

... ORDERING INFORMATION Model CS6422-CS CS6422-CSZ (Lead Free) CS6422-IS CS6422-ISZ (Lead Free) ENVIRONMENTAL, MANUFACTURING, & HANDLING INFORMATION Model Number CS6422-CS CS6422-CSZ (Lead Free) CS6422-IS CS6422-ISZ (Lead Free) * MSL (Moisture Sensitivity Level) as specified by IPC/JEDEC J-STD-020. REVISION HISTORY Revision Date PP4 JUL 2001 Preliminary Release ...