STM32F103ZC STMicroelectronics, STM32F103ZC Datasheet - Page 98

STM32F103ZC

Manufacturer Part Number

STM32F103ZC

Description

Mainstream Performance line, ARM Cortex-M3 MCU with 256 Kbytes Flash, 72 MHz CPU, motor control, USB and CAN

Manufacturer

STMicroelectronics

Datasheet

1.STM32F103RC.pdf

(130 pages)

Specifications of STM32F103ZC

Core

ARM 32-bit Cortex™-M3 CPU

Conversion Range

0 to 3.6 V

Dma

12-channel DMA controller

Supported Peripherals

timers, ADCs, DAC, SDIO, I2Ss, SPIs, I2Cs and USARTs

Systick Timer

a 24-bit downcounter

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

STM32F103ZCH6

Manufacturer:

STMicroelectronics

Quantity:

10 000

Company:

Part Number:

STM32F103ZCT6

Manufacturer:

STMicroelectronics

Quantity:

20 000

Company:

Part Number:

STM32F103ZCT6

Manufacturer:

STMicroelectronics

Quantity:

10 000

Part Number:

STM32F103ZCT6

Manufacturer:

ST

Quantity:

20 000

Electrical characteristics

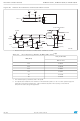

Table 54.

1. Based on design simulation and/or characterization results, not tested in production.

2. Depends on f

98/130

DuCy(SCK)

f

1/t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

t

CK

r(CK)

f(CK)

v(WS)

h(WS)

su(WS)

h(WS)

w(CKH)

w(CKL)

su(SD_MR)

su(SD_SR)

h(SD_MR)

h(SD_SR)

v(SD_ST)

h(SD_ST)

v(SD_MT)

h(SD_MT)

c(CK)

Symbol

(1)

(1)

(1)

(1)

(1)

(1)

(1)(2)

(1)(2)

(1)

(1)(2)

(1)(2)

(1)

(1)

(1)

I

2

PCLK

S characteristics

I2S slave input clock duty

cycle

I

I

WS valid time

WS hold time

WS setup time

WS hold time

CK high and low time

Data input setup time

Data input setup time

Data input hold time

Data output valid time

Data output hold time

Data output valid time

Data output hold time

2

2

S clock frequency

S clock rise and fall time

. For example, if f

Parameter

PCLK

=8 MHz, then T

Slave mode

Master mode (data: 16 bits,

Audio frequency = 48 kHz)

Slave mode

Capacitive load C

Master mode

Master mode

Slave mode

Slave mode

Master f

frequency = 48 kHz

Master receiver

Slave receiver

Master receiver

Slave receiver

Slave transmitter (after enable

edge)

Slave transmitter (after enable

edge)

Master transmitter (after enable

edge)

Master transmitter (after enable

edge)

Doc ID 14611 Rev 8

PCLK

PCLK

Conditions

= 1/f

= 16 MHz, audio

STM32F103xC, STM32F103xD, STM32F103xE

PLCLK

L

= 50 pF

=125 ns.

I2S2

I2S3

I2S2

I2S3

1.522

312.5

Min

345

6.5

1.5

0.5

30

11

0

3

2

0

4

0

2

0

0

1.525

Max

70

6.5

18

8

3

MHz

Unit

ns

%