LMH0031VS/NOPB National Semiconductor, LMH0031VS/NOPB Datasheet - Page 15

LMH0031VS/NOPB

Manufacturer Part Number

LMH0031VS/NOPB

Description

IC DESER/DESCRAM DGTL VID 64TQFP

Manufacturer

National Semiconductor

Type

Descrambler/Deserializerr

Datasheet

1.LMH0031VSNOPB.pdf

(31 pages)

Specifications of LMH0031VS/NOPB

Applications

SDTV/HDTV

Mounting Type

Surface Mount

Package / Case

64-TQFP, 64-VQFP

Input Voltage

3.3 V

Supply Voltage (max)

3.45 V

Supply Voltage (min)

3.15 V

Maximum Operating Temperature

+ 70 C

Minimum Operating Temperature

0 C

Mounting Style

SMD/SMT

For Use With

SD131EVK - BOARD EVALUATION LMH0031

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

*LMH0031VS

*LMH0031VS/NOPB

LMH0031VS

*LMH0031VS/NOPB

LMH0031VS

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LMH0031VS/NOPB

Manufacturer:

Texas Instruments

Quantity:

10 000

Device Operation

cally. EDH errors are reported in the EDH0, EDH1, and

EDH2 register sets of the configuration and control registers.

Updated or new EDH check words and flags may be gener-

ated and inserted in the data. EDH check words are gener-

ated using the polynomial X

RP165. Generation and automatic insertion of new or cor-

rected EDH check words is controlled by EDH Force and

EDH Enable bits in the control registers. EDH check words

and status flags are inserted in the parallel data at the

correct positions in the Ancillary Data space and formatted

per SMPTE 291M. After a reset, the initial state of all EDH

and CRC check characters is 00h.

The SMPTE 292M high definition video standard employs

CRC (cyclic redundancy check codes) error checking in-

stead of EDH. The CRC consists of two 18-bit words gener-

ated using the polynomial X

292M. One CRC is used for luminance and one for chromi-

nance data. The CRCs appear in the data stream following

the EAV and line number characters. The CRCs are checked

and errors are reported in the EDH0, EDH1, and EDH2

register sets of the configuration and control registers.

PHASE-LOCKED LOOP / CLOCK-DATA RECOVERY

SYSTEM

The phase-locked loop and clock-data recovery (PLL/

CDR) system generates all internal timing and data rate

clocks for the LMH0031. The PLL/CDR system consists of

five main functional blocks: 1) the input buffer which receives

the incoming data, 2) input data samplers which oversample

the data coming from the input buffer, 3) a PLL (VCO, divider

chain, phase-frequency detector and internal loop filter)

which generates sampling and other system clocks, 4) a

digital CDR system to recover the oversampled serial input

data from the samplers and the digital system control and 5)

a rate detect controller which sequences the PLL to find the

data rate.

Using an oversampling technique, the timing information

encoded in the serial data is extracted and used to synchro-

nize the recovered clock and data. The parallel data rate and

other clock signals are derived from the regenerated serial

clock. The parallel data rate clock is 1/10th of the serial data

rate clock for standard definition or 1/20th of the serial data

clock frequency for high definition. The data interface be-

tween the CDR and the digital processing block uses 10-bit

data plus the required clocks.

The PLL is held in coarse frequency lock by an external

27MHz clock signal, EXT CLK, or by an external 27MHz

crystal and internal oscillator. Upon power-on, EXT CLK is

the default reference. The internal oscillator and an external

crystal may be used as the reference by setting the OSCEN

bit in the CDR register. The reference clock reduces lock

latency and enhances format and auto-rate detection robust-

16

18

+ X

(Continued)

+ X

12

5

+ X

+ X

4

6

+ 1 per SMPTE

+ 1 per SMPTE

15

ness. PLL acquisition, data phase alignment and format

detection time is 20ms or less at 1.485Mbps. The VCO has

separate V

and 52, which may be supplied power via an external low-

pass filter, if desired.

A 27MHz crystal and load circuit may be used to provide the

reference clock. A fundamental mode crystal with the follow-

ing parameters is used: frequency 27MHz, frequency toler-

ance

100µW, equivalent series resistance

perature range 0˚C to 70˚C. Refer to Figure 6 for a typical

load circuit and connection information.

The LMH0031 indicates that the PLL is locked to the incom-

ing data rate and that the CDR has acquired a phase of the

serial data by setting the Lock Detect bit in the Video Info 0

control register. Indication of the standard being processed

is retained in the FORMAT[4:0] bits in the FORMAT 1 con-

trol data register. Format data from this register can be

programmed for output on the multi-function I/O port. The

power-on default assigns Lock Detect as I/O Port bit 4.

POWER SUPPLIES, POWER-ON-RESET AND RESET

INPUT

The LMH0031 requires two power supplies, 2.5V for the core

logic functions and 3.3V for the I/O functions. The supplies

must be applied to the device in proper sequence. The 3.3V

supply must be applied prior to or coincident with the 2.5V

supply. Application of the 2.5V supply must not precede the

3.3V supply. It is recommended that the 3.3V supply be

configured or designed so as to control application of the

2.5V supply in order to satisfy this sequencing requirement.

The LMH0031 has an automatic, power-on-reset circuit.

Reset initializes the device and clears TRS detection cir-

cuitry, all latches, registers, counters and polynomial

generators/checkers and resets the EDH/CRC characters to

00h. An active-HIGH-true, manual reset input is available at

pin 49. The reset input has an internal pull-down device and

may be considered inactive when unconnected.

Important: When power is first applied to the device or

following a reset, the ancillary and Control Data Port must

be initialized to receive data. This is done by toggling A

three times.

±

30ppm, load capacitance 18pF, maximum drive level

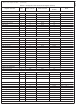

FIGURE 6. Crystal and Load Circuit

DDPLL

and V

SSPLL

power supply feeds, pins 51

20179605

<

50Ω, operating tem-

www.national.com

CLK