LMH0031VS/NOPB National Semiconductor, LMH0031VS/NOPB Datasheet - Page 24

LMH0031VS/NOPB

Manufacturer Part Number

LMH0031VS/NOPB

Description

IC DESER/DESCRAM DGTL VID 64TQFP

Manufacturer

National Semiconductor

Type

Descrambler/Deserializerr

Datasheet

1.LMH0031VSNOPB.pdf

(31 pages)

Specifications of LMH0031VS/NOPB

Applications

SDTV/HDTV

Mounting Type

Surface Mount

Package / Case

64-TQFP, 64-VQFP

Input Voltage

3.3 V

Supply Voltage (max)

3.45 V

Supply Voltage (min)

3.15 V

Maximum Operating Temperature

+ 70 C

Minimum Operating Temperature

0 C

Mounting Style

SMD/SMT

For Use With

SD131EVK - BOARD EVALUATION LMH0031

Lead Free Status / RoHS Status

Lead free / RoHS Compliant

Other names

*LMH0031VS

*LMH0031VS/NOPB

LMH0031VS

*LMH0031VS/NOPB

LMH0031VS

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LMH0031VS/NOPB

Manufacturer:

Texas Instruments

Quantity:

10 000

www.national.com

525 Line, 30 Frame, 27 MHz, NTSC 4x3 (SMPTE 125M)

625 Line, 25 Frame, 27 MHz, PAL 4x3 (ITU-T BT.601)

525 Line, 30 Frame, 36 MHz, NTSC 16x9 (SMPTE 125M)

625 Line, 25 Frame, 36 MHz, PAL 16x9 (ITU-T BT.601)

525 Line, 30 Frame, 54 MHz (NTSC)

625 Line, 25 Frame, 54 MHz (PAL)

Device Operation

Note: BIST test patterns for SD are: NTSC 4x3 Colour Bars and PAL 4x3 PLL Pathological.

VIDEO INFO 0 REGISTER (Address 0Eh)

Re-synchronization of the parallel video output data with the

parallel rate clock is controlled by the functions Framing

Enable, Framing Mode and NSP. For operating details

about these control bits, refer to the preceeding section

about Format Registers 0 and 1 and the Format Mode bit.

Framing Enable may be assigned as an input on the multi-

function I/O port.

The NSP (New Sync Position) bit indicates that a new or

out-of-place TRS character has been detected in the input

data. This bit is set to a logic-1 and remains set for at least

one horizontal line period or unless re-activated by a subse-

quent new or out-of-place TRS. It is reset by an EAV TRS

character.

The EAV (end of active video) and SAV (start of active video)

bits track the occurrence of the corresponding TRS charac-

ters.

The Lock Detect is a logic-1 when the loop is locked and the

CDR has acquired a phase of the incoming serial data. This

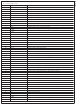

Test Pattern Select Word Bits

Colour Bars (SD BIST)

PLL Path. (SD BIST)

Colour Bars

Colour Bars

Colour Bars

Colour Bars

Colour Bars

Ref. Black

Ref. Black

Ref. Black

Ref. Black

Ref. Black

Ref. Black

PLL Path.

PLL Path.

PLL Path.

PLL Path.

PLL Path.

EQ Path.

EQ Path.

EQ Path.

EQ Path.

EQ Path.

EQ Path.

(Continued)

>

TABLE 5. Test Pattern Selection Codes (Continued)

Bit 5

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

Bit 4

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

0

0

0

0

1

1

1

1

24

bit may be programmed as an output on the multi-function

I/O bus. This bit is mapped to I/O port bit 4 in the default

condition.

The VPG Filter Enable bit when set enables operation of the

Video Pattern Generator filter. Operation of this filter causes

the insertion of transition codes in the chroma and luma data

of colour bar test patterns where these patterns change from

one bar to the next. This filter reduces the magnitude of

out-of-band frequency products which are produced by

abrupt transitions in the chroma and luma data when fed to

D-to-A converters and picture monitors.

The LMH0031 incorporates circuitry that implements a

method for handling data that has been subjected to LSB

dithering. Data from the de-scrambler is routed for de-

dithering. Control of this circuitry is via the De-Dither Enable

bit in the VIDEO INFO 0 control register. Recovery of data

that has been dithered during the vertical blanking interval

can be selectively enabled by use of the V De-Dither Enable

bit in the VIDEO INFO 0 control register. The initial condition

of De-Dither Enable and V De-Dither Enable is OFF.

Bit 3

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

Bit 2

0

0

0

0

0

0

0

0

1

1

1

1

1

1

1

1

0

0

0

0

0

0

0

0

Bit 1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

0

0

1

1

Bit 0

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1

0

1