CXD2463R Sony, CXD2463R Datasheet

CXD2463R

Available stocks

Related parts for CXD2463R

CXD2463R Summary of contents

Page 1

... Timing Controller for CCD Camera Description The CXD2463R generates the sync signals for timing control and back end signal processing in a CCD camera system using a 510H or 760H black- and-white CCD image sensor. Features • Built-in sync signal generation function • Built-in electronic iris (electronic shutter) function • ...

Page 2

... TEST EIA HD VD HVDET EXT EHD/SYNC EVD COMP DECODER DRIVER – 2 – CXD2463R V ...

Page 3

... Iris signal input/shutter speed setting 14 CV — GND (for comparator Description – 3 – CLP2 23 CLP1 22 TEST ESHUT1 21 20 ESHUT2 BLCW2 17 BLCW1 BLC IRIN/ED1 CXD2463R ...

Page 4

... Power supply (for H1, H2, and RG clock output for CCD horizontal register drive clock output for CCD horizontal register drive 47 AV — GND (for H1, H2, and RG Reset gate pulse output Description – 4 – CXD2463R ...

Page 5

... –8. 15V VH H – 5 – CXD2463R = 5V ± 0.25V, Topr = –20 to +75°C) DD Min. Typ. Max. 4.75 5.0 5.25 0.7V DD 0.3V DD 0.8V DD 0. – 0.8 DD 0.4 V – 0.8 DD 0.4 V – 0 ...

Page 6

... Power-on reset period t WRST ( 0V 1MHz Min. Typ. Max ± 0.25V, Topr = –20 to +75°C) DD Min. Typ. Max. ±70 0. WRST Min. Typ. Max. 35 – 6 – Unit Unit mV Pins 11 and 12 (SPUPV, SPDNV) Indefinite region Unit ns CXD2463R ...

Page 7

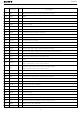

... Shutter speed up reference voltage 2) Electronic Shutter Mode Symbol Pin No. SPUPV/ED0 11 IRIN/ED1 13 SPDNV/ED2 12 EIA: Shutter speed CCIR: Operating Mode Function 1/100 1/250 1/500 1/1000 1/120 – 7 – Mode 1/2000 1/5000 1/10000 CXD2463R 1/100000 ...

Page 8

... Backlighting Correction Function The CXD2463R has a function to output the window pulse for backlight compensation. The backlight compensation pulse is output from BLC (Pin 15) in the following range according to the high/low combination of BLCW1 (Pin 17) and BLCW2 (Pin 18). Window Type for Different Pin Combinations ...

Page 9

... Window Pulse Timing Charts • EIA Mode/Vertical Direction Timing (1) Full-screen photometry VD HD 20HD BLC (2) Center emphasis photometry VD HD 101HD BLC (3) Bottom emphasis photometry VD HD BLC 0.5HD 181HD 0.5HD 181HD – 9 – CXD2463R 20.5HD 101.5HD 181.5HD 181.5HD ...

Page 10

... EIA Mode/Horizontal Direction Timing (1) Bottom emphasis photometry and full-screen photometry HD MCK BLC (2) Center emphasis photometry HD MCK BLC X1 X1 – 10 – CXD2463R X2 510H 104MCK X1 760H 154MCK 510H 3MCK X2 760H 22MCK X2 510H 272MCK X1 760H 407MCK 510H 167MCK X2 760H 252MCK ...

Page 11

... CCIR Mode/Vertical Direction Timing (1) Full-screen photometry VD HD 25HD BLC (2) Center emphasis photometry VD HD 121HD BLC (3) Bottom emphasis photometry VD HD BLC 0.5HD 216HD 0.5HD 216HD – 11 – CXD2463R 25.5HD 121.5HD 216.5HD 216.5HD ...

Page 12

... CCIR Mode/Horizontal Direction Timing (1) Bottom emphasis photometry and full-screen photometry HD MCK BLC (2) Center emphasis photometry HD MCK BLC X1 X1 – 12 – CXD2463R X2 510H 114MCK X1 760H 169MCK 510H 3MCK X2 760H 22MCK X2 510H 279MCK X1 760H 416MCK 510H 164MCK X2 760H 246MCK ...

Page 13

... External Sync Function The CXD2463R supports the three modes of Line-Lock, VReset + HPLL (VD and HD inputs), and VReset + HPLL (Sync input) as the external sync functions. Each mode is automatically switched according to the combination of signals input to EHD/SYNC (Pin 38) and EVD (Pin 37). 1) Automatic External Sync Discrimination ...

Page 14

... Similar to Line-Lock mode, the result of comparing the phase of the falling edges of the HD cycle clock input to Pin 38 and the CXD2463R internal HD is output from COMP (Pin 39). The PLL is applied using this signal. Similar to Line-Lock mode, the polarity of the COMP (Pin 39) output is compatible with the active filter. The phase of the HD falling edge can be shifted up to ± ...

Page 15

... EXT-VD and EXT-HD have the same phase. 1/4H 1/4H EXT-VD (Pin 37 input) EXT-HD (Pin 38 input) VD (Pin 35 output) HD (Pin 36 output) SYNC (Pin 25 output) (2) EXT-VD and EXT-HD have the same phase to +1/4H. EXT-VD EXT- SYNC (3) EXT-VD and EXT-HD have the same phase to –1/4H. EXT-VD EXT- SYNC – 15 – CXD2463R ...

Page 16

... EXT-VD and EXT-HD have the same phase. 1/4H 1/4H EXT-VD (Pin 37 input) EXT-HD (Pin 38 input) VD (Pin 35 output) HD (Pin 36 output) SYNC (Pin 25 output) (2) EXT-VD and EXT-HD have the same phase to +1/4H. EXT-VD EXT- SYNC (3) EXT-VD and EXT-HD have the same phase to –1/4H. EXT-VD EXT- SYNC – 16 – CXD2463R ...

Page 17

... EXT-VD and EXT-HD have the same phase. 1/4H 1/4H EXT-VD (Pin 37 input) EXT-HD (Pin 38 input) VD (Pin 35 output) HD (Pin 36 output) SYNC (Pin 25 output) (2) EXT-VD and EXT-HD have the same phase to +1/4H. EXT-VD EXT- SYNC (3) EXT-VD and EXT-HD have the same phase to –1/4H. EXT-VD EXT- SYNC – 17 – CXD2463R ...

Page 18

... EXT-HD.) COMP (Pin 39) outputs the result of comparing the phase of the falling edge of the shifted EXT-HD (signal input to Pin 37) and the falling edge of the CXD2463R internal HD. The polarity is compatible with the active filter. ...

Page 19

... EIA/EVEN EXT-SYNC (Pin 38 input) EXT-VD (Generated inside the CXD2463R) EXT-HD (Pin 36 output) (1) Same phase SFT-HD (1) (Pin 37 input) VD (Pin 35 output) HD (Generated inside the CXD2463R) SYNC (Pin 25 output) (2) Delayed phase SFT-HD ( SYNC (3) Advanced phase SFT-HD ( SYNC 1/2H 1/2H – 19 – CXD2463R ...

Page 20

... CCIR/ODD EXT-SYNC (Pin 38 input) EXT-VD (Generated inside the CXD2463R) EXT-HD (Pin 36 output) (1) Same phase SFT-HD (1) (Pin 37 input) VD (Pin 35 output) HD (Generated inside the CXD2463R) SYNC (Pin 25 output) (2) Delayed phase SFT-HD ( SYNC (3) Advanced phase SFT-HD ( SYNC 1/2H 1/2H – 20 – CXD2463R ...

Page 21

... CCIR/EVEN EXT-SYNC (Pin 38 input) EXT-VD (Generated inside the CXD2463R) EXT-HD (Pin 36 output) (1) Same phase SFT-HD (1) (Pin 37 input) VD (Pin 35 output) HD (Generated inside the CXD2463R) SYNC (Pin 25 output) (2) Delayed phase SFT-HD ( SYNC (3) Advanced phase SFT-HD ( SYNC 1/2H 1/2H – 21 – CXD2463R ...

Page 22

... CXD2463R ...

Page 23

... CXD2463R ...

Page 24

... CXD2463R ...

Page 25

... CXD2463R ...

Page 26

... CXD2463R ...

Page 27

... CXD2463R ...

Page 28

... CXD2463R ...

Page 29

... CXD2463R ...

Page 30

... CXD2463R ...

Page 31

... CXD2463R ...

Page 32

... CXD2463R ...

Page 33

... CXD2463R ...

Page 34

... CXD2463R ...

Page 35

... High-Speed Phase Timing Chart for the Timing Generator Block MCK (Internal clock CCD OUT SHP SHD – 35 – CXD2463R ...

Page 36

... CXD2463R ...

Page 37

... LQFP (PLASTIC) 0.2 0 (0.22 0.2 1.5 – 0.1 0.13 M 0.1 0.1 0.18 – 0.03 DETAIL B: SOLDER NOTE: Dimension “ ” does not include mold protrusion. PACKAGE STRUCTURE PACKAGE MATERIAL LEAD TREATMENT LQFP-48P-L01 LEAD MATERIAL P-LQFP48-7x7-0.5 PACKAGE MASS – 37 – 0.05 0.127 – 0.02 0 0.08 (0.18) EPOXY RESIN SOLDER PLATING 42/COPPER ALLOY 0.2g CXD2463R ...

Page 38

... SONY CODE EIAJ CODE JEDEC CODE 48PIN LQFP (PLASTIC) 9.0 0.2 7 0.05 b=0.18 (0.16) DETAIL B DETAIL A PACKAGE STRUCTURE PACKAGE MATERIAL LEAD TREATMENT LQFP-48P-L281 LEAD MATERIAL P-LQFP48-7X7-0.5 PACKAGE MASS – 38 – 1.7MAX 1.4 0. 0.08 0.05 EPOXY RESIN SOLDER PLATING COPPER ALLOY 0.2g CXD2463R ...

Page 39

... LQFP (PLASTIC) 9.0 0.2 7 0.05 b=0.21 (0.2) DETAIL B 0˚ to 7˚ DETAIL A PACKAGE STRUCTURE PACKAGE MATERIAL LEAD TREATMENT LQFP-48P-L282 LEAD MATERIAL P-LQFP48-7X7-0.5 PACKAGE MASS SPEC. COPPER ALLOY Sn-Bi 2.5% 5-18 m – 39 – 1.7MAX 1.4 0. 0.08 S 0.05 EPOXY RESIN SOLDER PLATING COPPER ALLOY 0.2g Sony Corporation CXD2463R ...