LM1872 National Semiconductor, LM1872 Datasheet - Page 16

LM1872

Manufacturer Part Number

LM1872

Description

Radio Control Receiver/Decoder

Manufacturer

National Semiconductor

Datasheet

1.LM1872.pdf

(20 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

LM1872N

Manufacturer:

MIT

Quantity:

5 510

Applications

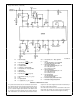

EXPANSION TO SIX ANALOG CHANNELS

Still greater analog capacity can be obtained with an out-

board auxiliary decoder The LM1872 a simple comparator

and an 8-bit parallel-out serial shift register comprise a six

analog channel receiver decoder (Figure 12) The one tran-

sistor comparator reconstructs the detector output of the

LM1872 from the sync timer waveform and feeds it to the

clock input of the shift register The channel 1 output then

loads a ‘‘one’’ into the register and the clock shifts the

‘‘one’’ down the line of analog channel outputs in accord-

ance with the time information from the detector output

Note that the reconstructed detector waveform lags the

channel 1 output very slightly ( j 10

slope of the sync capacitor discharge edge This delay is

very important as it insures that channel 1 is high when the

clock strikes initially (thus loading a ‘‘1’’) and low for each

subsequent positive clock edge (thus preventing the loading

of extraneous ‘‘1’s’’)

(Continued)

s) due to the finite

FIGURE 12 Deriving Six Analog Channels

b) Six Channel Auxiliary Decoder

a) Six Channel Timing Diagram

16

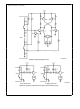

CONVERTING AN ANALOG CHANNEL

TO A DIGITAL CHANNEL

Either analog channel can be converted to a digital channel

with the aid of a low cost CMOS hex inverter (Figure 13)

The internal 10k resistor and external capacitor C1 set a

time constant (1 ms) that falls between a short (0 5 ms) and

a long (2 ms) transmitted pulse option For pulses longer

than 1 ms the first inverter will pull low momentarily once

each frame Repetitive discharges of C2 prevent it from ever

reaching threshold (V

stant is set longer (70 ms) than the frame period With the

inverter input below threshold Q1 will energize the load For

analog output pulses shorter than 1 ms the first inverter will

back bias D1 allowing C2 to ramp past threshold and Q1 to

go off For extra output drive the remaining inverters in the

package can be paralleled to drive Q1 Alternatively for light

loads Q1 can be eliminated altogether

a

2) because the R1 C2 time con-

TL H 7912 – 24

TL H 7912– 23