WM8978 Wolfson Microelectronics Ltd., WM8978 Datasheet - Page 68

WM8978

Manufacturer Part Number

WM8978

Description

The WM8978 is a low power, high quality stereo codec designed for portable applications such as Digital still camera or Digital Camcorde

Manufacturer

Wolfson Microelectronics Ltd.

Datasheet

1.WM8978.pdf

(108 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

WM8978CGEFL/RV

Manufacturer:

WOLFSON

Quantity:

10 000

Part Number:

WM8978CGEFL/RV

Manufacturer:

WOLFSON

Quantity:

20 000

Company:

Part Number:

WM8978G

Manufacturer:

SANYO

Quantity:

87 018

Part Number:

WM8978G

Manufacturer:

WM

Quantity:

20 000

Part Number:

WM8978GEFL

Manufacturer:

WOLFSON

Quantity:

20 000

Company:

Part Number:

WM8978GEFL/RV

Manufacturer:

WOLFSON

Quantity:

9 870

WM8978

w

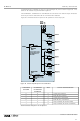

Table 49 Audio Interface Control

Note: Right Justified Mode will only operate with a maximum of 24 bits. If 32-bit mode is selected,

the device will operate in 24-bit mode.

AUDIO INTERFACE CONTROL

The register bits controlling audio format, word length and master / slave mode are summarised

below. The audio interfaces can be controlled individually.

Register bit MS selects audio interface operation in master or slave mode. In Master mode BCLK,

and LRC are outputs. The frequency of BCLK in master mode are controlled with BCLKDIV. These

are divided down versions of master clock. This may result in short BCLK pulses at the end of a

LRC if there is a non-integer ratio of BCLKs to LRC clocks.

R4

Audio

Interface

Control

REGISTER

ADDRESS

0

1

2

4:3

6:5

7

8

BIT

MONO

ADCLRSWAP

DACLRSWAP

FMT

WL

LRP

BCP

LABEL

0

0

0

10

10

DEFAULT

Selects between stereo and mono

device operation:

0=Stereo device operation

1=Mono device operation. Data appears

in ‘left’ phase of LRC

Controls whether ADC data appears in

‘right’ or ‘left’ phases of LRC clock:

0=ADC data appear in ‘left’ phase of

LRC

1=ADC data appears in ‘right’ phase of

LRC

Controls whether DAC data appears in

‘right’ or ‘left’ phases of LRC clock:

0=DAC data appear in ‘left’ phase of

LRC

1=DAC data appears in ‘right’ phase of

LRC

Audio interface Data Format Select:

00=Right Justified

01=Left Justified

10=I

11= DSP/PCM mode

Word length

00=16 bits

01=20 bits

10=24 bits

11=32 bits (see note)

LRC clock polarity

0=normal

1=inverted

BCLK polarity

0=normal

1=inverted

2

S format

PTD Rev 2.6 November 2005

DESCRIPTION

Preliminary Technical Data

68