AT94K05AL ATMEL Corporation, AT94K05AL Datasheet - Page 31

AT94K05AL

Manufacturer Part Number

AT94K05AL

Description

Fpslic Devices Combine 5K Gates of Atmel's Patented AT40K Fpga Architecture, a 20 Mips Avr 8-bit Risc Microprocessor Core, Numerous Fixed Microcontroller Peripheries And up to 36K Bytes of Program And Data SRAM.

Manufacturer

ATMEL Corporation

Datasheet

1.AT94K05AL.pdf

(192 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Rev. 1138F–FPSLI–06/02

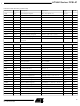

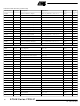

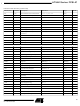

Table 10. FPSLIC System Control Register

Bit

SCR6

SCR7 - SCR12

SCR13

SCR14 - SCR15

SCR16 - SCR23

SCR24 - SCR25

SCR26

SCR27

SCR28 - SCR29

SCR30

SCR31

Description

0 = OTS Disabled

1 = OTS Enabled

Setting SCR6 makes the OTS (output tri-state) pin an input which controls the

global tri-state control for all user I/O. This junction allows the user at any time to

tristate all user I/O and isolate the chip.

Reserved

0 = CCLK Normal Operation

1 = CCLK Continues After Configuration.

Setting bit SCR13 allows the CCLK pin to continue to run after configuration

download is completed. This bit is valid for Master mode, mode 0 only. The CCLK

is not available internally on the device. If it is required in the design, it must be

connected to another device I/O.

Reserved

0 = GCK 0:7 Always Enabled

1 = GCK 0:7 Disabled During Internal and External Configuration Download.

Setting SCR16:SCR23 allows the user to disable the input buffers driving the

global clocks. The clock buffers are enabled and disabled synchronously with the

rising edge of the respective GCK signal, and stop in a High “1” state. Setting one

of these bits disables the appropriate GCK input buffer only and has no effect on

the connection from the input buffer to the FPGA array.

0 = FCK 0:1 Always Enabled

1 = FCK 0:1 Disabled During Internal and External Configuration Download.

Setting SCR24:SCR25 allows the user to disable the input buffers driving the fast

clocks. The clock buffers are enabled and disabled synchronously with the rising

edge of the respective FCK signal, and stop in a High “1” state. Setting one of

these bits disables the appropriate FCK input buffer only and has no effect on the

connection from the input buffer to the FPGA array.

0 = Disable On-chip Debugger

1 = Enable On-chip Debugger.

JTAG Enable, SCR27, must also be set (one) and the configuration memory

lockout, SCR4, must be clear (zero) for the user to have access to internal scan

chains.

0 = Disable TAP at user FPGA I/O Ports

1 = Enable TAP at user FPGA I/O Ports.

Device ID scan chain and AVR I/O boundary scan chain are available. The user

must set (one) the On-chip Debug Enable, SCR26, and must keep the

configuration memory lockout, SCR4, clear (zero) for the user to have access to

internal scan chains.

Reserved

0 = Global Set/Reset Normal

1 = Global Set/Reset Active (Low) During Internal and External Configuration

Download.

SCR30 allows the Global set/reset to hold the core DFFs in reset during any

configuration download. The Global set/reset net is released at the end of

configuration download on the rising edge of CON, if set.

0 = Disable I/O Tri-state

1 = I/O Tri-state During (Internal and External) Configuration Download.

SCR31 forces all user defined I/O pins to go tri-state during configuration

download. Tri-state is released at the end of configuration download on the rising

edge of CON, if set.

AT94K Series FPSLIC

31