ISL6532A Intersil Corporation, ISL6532A Datasheet

ISL6532A

Available stocks

Related parts for ISL6532A

ISL6532A Summary of contents

Page 1

... Data Sheet ACPI Regulator/Controller for Dual Channel DDR Memory Systems The ISL6532A provides a complete ACPI compliant power solution for DIMM dual channel DDR/DDR2 Memory systems. Included are both a synchronous buck controller and integrated LDO to supply V with high current during DDQ S0/S1 states and standby current during S3 state ...

Page 2

Block Diagram P5VSBY VDDQ S3 REGULATOR + - VDDQ(3) VTTSNS VTT REG - VTT(2) + GNDQ DISABLE { R U VREF_IN { GNDA + - UV/OV2 VREF_OUT S3# S5# 5VSBY VOLTAGE REFERENCE 0.800V 0.680V (-15%) 5V ...

Page 3

... SLEEP STATE LOGIC PWM CONTROLLER STANDBY LDO LINEAR CONTROLLER VTT REGULATOR 5VSBY +12V C BP S3# NCH S5# VREF_OUT OCSET VREF_IN UGATE + PHASE VTT ISL6532A LGATE VTT VDDQ VDDQ VDDQ GNDQ VTTSNS GNDQ DRIVE2 FB COMP FB2 GNDP GNDA 5V NCH Q1 V DDQ + Q2 V REF + ...

Page 4

... SLP_S5 V REF VTT_OUT V DDQ Q3 V AGP 1. OUT2 4 ISL6532A 5VSBY +12V C BP S3# NCH S5# VREF_OUT OCSET VREF_IN UGATE PHASE VTT ISL6532A LGATE VTT VDDQ VDDQ VDDQ GNDQ VTTSNS GNDQ DRIVE2 FB COMP FB2 GNDP GNDA 5V Dual + OCSET Q1 V DDQ L 2.5V OUT + Q2 C VDDQ_OUT ...

Page 5

... DC Gain Gain-Bandwidth Product Slew Rate STATE LOGIC S3# Transition Level S5# Transition Level 5 ISL6532A Thermal Information Thermal Resistance (Typical, Notes 1, 2) QFN Package . . . . . . . . . . . . . . . . . . . Maximum Junction Temperature (Plastic Package 150 Maximum Storage Temperature Range . . . . . . . . . -65 Maximum Lead Temperature (Soldering 10s 300 (SOIC - Lead Tips Only) ...

Page 6

... TEST CONDITIONS I GATE I GATE I NCH = 0.8V NCH V NCH P5VSBY = 5.0V P5VSBY = 3. VREF_OUT I Periodic load applied with 30% duty cycle VTT_MAX and 10ms period using ISL6532AEVAL1 evaluation board (see Application Note AN1056) Guaranteed By Design GBWP VTTSNS/ VDDQ VTTSNS/ VDDQ I OCSET ...

Page 7

... Functional Pin Description 5VSBY (Pin 2) 5VSBY is the bias supply of the ISL6532A typically connected to the 5V standby rail of an ATX power supply. During S4/S5 sleep states the ISL6532A enters a reduced power mode and draws less than 1mA (I 5VSBY supply. The supply to 5VSBY should be locally bypassed using a 0.1µ ...

Page 8

... POR thresholds. ACPI State Transitions Cold Start (S4/ Transition) At the onset of a mechanical start, the ISL6532A receives it’s bias voltage from the 5V Standby bus (5VSBY). As soon as the SLP_S3 and SLP_S5 have transitioned HIGH, the ISL6532A starts an internal counter. Following a cold start or any subsequent S4/S5 state, state transitions are ignored until the system enters S0/S1 ...

Page 9

... ENABLED FIGURE 2. TYPICAL STATE TRANSITION is disabled, the TT Active to Shutdown ( Transition) When the system transitions from active, S0, state to shutdown, S4/S5, state, the ISL6532A IC disables all regulators and forces the PGOOD pin and the NCH pin LOW. V Over Current Protection (S0 State) DDQ ...

Page 10

... LOW and then back to HIGH. Thermal Protection (S0/S3 State) If the ISL6532A IC junction temperature reaches a nominal temperature of 140 ISL6532A will not re-enable the outputs until the junction temperature drops below 110 is toggled in order to initiate a POR or the SLP_S5 signal is forced LOW and then back to HIGH. ...

Page 11

... There are two sets of critical components in the ISL6532A switching converter. The switching components are the most critical because they switch large amounts of energy, and therefore tend to generate large amounts of noise. Next are the small signal components which connect to sensitive nodes or supply critical bypass current and signal coupling ...

Page 12

... ESR 2π The compensation network consists of the error amplifier (internal to the ISL6532A) and the impedance networks Z and Z . The goal of the compensation network is to provide FB a closed loop transfer function with the highest 0dB crossing frequency (f ) and adequate phase margin. Phase margin ...

Page 13

... If the output voltage desired is 0.8V, simply route V to the FB pin through R1, but do not populate R4. The output voltage for the internal V TT internal to the ISL6532A to track the V There is no need for external programming resistors. As with the V PWM regulator, the AGP linear regulator DDQ output voltage is set by means of an external resistor divider as shown in Figure 7 ...

Page 14

... Given a sufficiently fast control loop design, the ISL6532A will provide either 0% or 100% duty cycle in response to a load transient. The response time is the time required to slew the inductor current from an initial current value to the transient current level ...

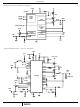

Page 15

... C 287Ω 24 220µF 1µF FIGURE 8. DDR SDRAM AND AGP VOLTAGE REGULATOR USING THE ISL6532A 15 ISL6532A ISL6532A Application Circuit Figure 8 shows an application circuit utilizing the ISL6532A. Detailed information on the circuit, including a complete Bill- of-Materials and circuit board description, can be found in Application Note AN1056 ...

Page 16

... However, no responsibility is assumed by Intersil or its subsidiaries for its use; nor for any infringements of patents or other rights of third parties which may result from its use. No license is granted by implication or otherwise under any patent or patent rights of Intersil or its subsidiaries. For information regarding Intersil Corporation and its products, see www.intersil.com 16 ISL6532A L28.6x6 28 LEAD QUAD FLAT NO-LEAD PLASTIC PACKAGE (COMPLIANT TO JEDEC MO-220VJJC ISSUE C) ...