MD1822DB3 Supertex, Inc., MD1822DB3 Datasheet - Page 8

MD1822DB3

Manufacturer Part Number

MD1822DB3

Description

Manufacturer

Supertex, Inc.

Datasheet

1.MD1822DB3.pdf

(8 pages)

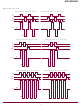

Test Waveforms

Fig 5:

JTAG or Boundary Scan mode is an industry standard (IEEE

1149.1, or 1532) serial programming mode. External logic

from a cable, microprocessor, or other device is used to

drive the JTAG specific pins, Test Data Out (TDO), Test Data

121010

JTAG or Boundary Scan Mode

©2010

Supertex inc.

an adequate “product liability indemnification insurance agreement.”

to the replacement of the devices determined defective due to workmanship. No responsibility is assumed for possible omissions and inaccuracies. Circuitry and

specifications are subject to change without notice. For the latest product specifications refer to the

JTAG Connector

Supertex inc.

Input to output delay and fall time of output at V

I

OUT

J8-1

J8-2

J8-3

J8-4

J8-5

J8-6

= 330pF(105V/10.5ns) = 3.2A.

does not recommend the use of its products in life support applications, and will not knowingly sell them for use in such applications unless it receives

All rights reserved. Unauthorized use or reproduction is prohibited.

TMS

TDI

TDO

TCK

GND

VCC

(cont.)

Pin Number

Description

Test Mode Select of CPLD.

Test Data In of CPLD.

Test Data Out of CPLD.

Test Clock of CPLD.

Logic Power Supply Ground 0V for programming and testing only.

Logic Power Supply +3.3V for CPLD programming or testing only.

Supertex inc.

DD

= 10V, V

8

In (TDI), Test Mode Select (TMS), and Test Clock (TCK).

This mode has gained popularity due to its standardization

and ability to program CPLD through the same four JTAG

pins. The data in this mode is loaded at one bit per TCK.

does not assume responsibility for use of devices described, and limits its liability

PP

/VNN = ±70V, Load = 330pF//2.5k,

Supertex inc.

(website: http//www.supertex.com)

1235 Bordeaux Drive, Sunnyvale, CA 94089

Supertex inc.

MD1822DB3

www.supertex.com

Tel: 408-222-8888