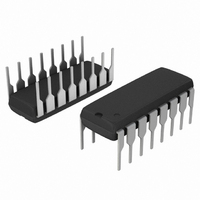

MC14076BCPG ON Semiconductor, MC14076BCPG Datasheet

MC14076BCPG

Specifications of MC14076BCPG

MC14076BCPGOS

Related parts for MC14076BCPG

MC14076BCPG Summary of contents

Page 1

... Unused inputs must always be tied to an appropriate logic voltage level (e.g., either Unused outputs must be left open *For additional information on our Pb−Free strategy and soldering details, please download the ON Semiconductor Soldering and Mounting Techniques Reference Manual, SOLDERRM/D. © Semiconductor Components Industries, LLC, 2009 September, 2009 − Rev Value Unit − ...

Page 2

PIN ASSIGNMENT { OUTPUT DISABLE ...

Page 3

... ORDERING INFORMATION Device MC14076BCPG MC14076BDG MC14076BDR2G †For information on tape and reel specifications, including part orientation and tape sizes, please refer to our Tape and Reel Packaging Specifications Brochure, BRD8011/D. Package PDIP−16 (Pb−Free) SOIC−16 (Pb−Free) SOIC−16 (Pb−Free) http://onsemi.com 3 † ...

Page 4

ELECTRICAL CHARACTERISTICS Î Î Î Î Î ...

Page 5

SWITCHING CHARACTERISTICS (Note 5) Î Î Î ...

Page 6

INPUT RISE AND FALL 20 ns 90% INPUT D 50% INFORMATION 10 50 PLH 90% Q OUTPUT 10% t TLH RESET = 0 DATA DISABLE A AND ...

Page 7

−T− 0.25 (0.010 PACKAGE DIMENSIONS PDIP−16 P SUFFIX CASE 648−08 ISSUE T L SEATING PLANE http://onsemi.com 7 NOTES: 1. ...

Page 8

... Opportunity/Affirmative Action Employer. This literature is subject to all applicable copyright laws and is not for resale in any manner. PUBLICATION ORDERING INFORMATION LITERATURE FULFILLMENT: Literature Distribution Center for ON Semiconductor P.O. Box 5163, Denver, Colorado 80217 USA Phone: 303−675−2175 or 800−344−3860 Toll Free USA/Canada Fax: 303− ...