SC1211 Semtech Corporation, SC1211 Datasheet

SC1211

Available stocks

Related parts for SC1211

SC1211 Summary of contents

Page 1

... Timed latches and improved robustness are built into the housekeeping functions such as the Under Voltage Lockout and adaptive Shoot-through protection circuitry to prevent false triggering and to assure safe operation. The SC1211 is offered in a Power SOIC-8L package. February 24, 2003 Synchronous MOSFET Driver Features ...

Page 2

... Typical Application Circuit + DRN VREG 3 6 BST VIN VPN 2 1 2003 Semtech Corp DRN VREG 3 6 BST VIN VPN 2 SC1211 + + + + DRN VREG 3 6 BST VIN VPN www.semtech.com ...

Page 3

... STG T LEAD = 8.5V Symbol Conditions Iq_op V REG_START Vhys UVLO 16V REG 8.8V DROP SC1211 Maximum < 100ns < 200ns - < 100ns 20 -0.3 to 8.5 =125°C 2. +125 -65 to +150 300 Min Typ Max ...

Page 4

... R_BG BST 3nF F_BG BST 8.5V PDH_BG BST DRN 8.5V PDL_BG BST DRN t PDH_UVLO t PDL_UVLO 4 Min Typ Max 2.0 155 10 1.5 1.0 = 8.5V 15 DRN = 8.5V 10 DRN 37 30 1.5 1.5 = 8.5V 10 DRN = 8.5V 10 DRN www.semtech.com SC1211 Units V 0.8 V °C °C 3.0 2 3.0 3 µs µs ...

Page 5

... POWER MANAGEMENT Timing Diagrams CO DRN PDL_BG Rising Edge Transition 2003 Semtech Corp PDH_TG R_TG 1.4V F_BG 5 SC1211 1. PDL_TG F_TG t t PDH_BG R_BG Falling Edge Transition www.semtech.com ...

Page 6

... Bootstrap pin. A capacitor is connected between BST and DRN pins to develop the floating 3 BST bootstrap voltage for the high-side MOSFET. The capacitor value is typically 1µF (ceramic). Logic level PWM input signal to the SC1211 supplied by external controller. An internal 50kohm 4 CO resistor is connected from this pin to PGND. ...

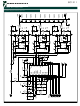

Page 7

... POWER MANAGEMENT Block Diagram VIN CO PGND 2003 Semtech Corp. UVLO LOGIC CONTROL & OVERLAP PROTECTION CIRCUIT 7 SC1211 LDO VREG VPN BST TG DRN BG www.semtech.com ...

Page 8

... Startup and UVLO To startup the driver, a supply voltage is applied to VIN pin of the SC1211. The top and bottom gates are held low until VIN exceeds UVLO threshold of the driver, typi- cally 4.0V. Then the top gate remains low and the bot- tom gate is pulled high to turn on the bottom FET. Once VIN exceeds UVLO threshold of the PWM controller, typi- cally 7 ...

Page 9

... Optimized Gate Drive Voltage With the supply voltage in between 9V to 16V, an inter- nal LDO is designed with the SC1211 to bring the volt- age to a lower level for gate drive. An external Ceramic capacitor(1uF to 4.7uF) connected in between Vreg to ground is needed to support the LDO. The LDO output is ...

Page 10

... SC1211 EVB Layout Guideline. For the SC1211 driver, the following guidelines are typi- cally recommended during PCB layout: 1. Place the SC1211 close to the FETs for shortest gate drive traces and ground return paths. 2. Connect bypass capacitors as close as possible to decoupling pins (VREG and VIN) and PGND. The trace length of the decoupling capacitor on VREG pin should be no more than 0.2” ...

Page 11

... POWER MANAGEMENT Outline Drawing - Power SOIC-8 Outline Drawing - Power SOIC-8L Land Pattern - Power SOIC-8 Contact Information 2003 Semtech Corp. Semtech Corporation Power Management Products Division 200 Flynn Rd., Camarillo, CA 93012 Phone: (805)498-2111 FAX (805)498-3804 11 SC1211 www.semtech.com ...