SC1218 Semtech, SC1218 Datasheet - Page 10

SC1218

Manufacturer Part Number

SC1218

Description

High Speed Synchronous MOSFET Driver

Manufacturer

Semtech

Datasheet

1.SC1218.pdf

(12 pages)

Typically, a 1uF/16V ceramic capacitor is used. In addi-

tion, a small resistor (one ohm) is recommended in be-

tween DRN pin of the SC1218 and the phase node. The

resistor is used to alleviate the stress of the SC1218, re-

sulting from the negative spike at the phase node, and

also to control the switching speed. A negative spike could

occur at the phase node during the top FET turn-off due to

parasitic inductance in the switching loop. The spike could

be minimized with a careful PCB layout. In the applica-

tions with TO-220 package FETs, it is suggested to use a

clamping diode on the DRN pin to mitigate the impact of

the excessive phase node negative spikes.

For VIN pin of the SC1218, it is recommended to use a

1uF/16V ceramic capacitor for decoupling.

Driv

Driv

Driv

Driv

Driver Dissipation and Junction T

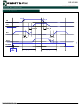

The driver power dissipation is a function of chip quies-

cent current I

age V

where Q

bottom-side FETs. The power dissipation vs total gate

charge at the given switching frequency is plotted in Fig.11.

The driver junction temperature can be calculated based

on the juntion to case thermal resistance and Printed Cir-

cuit Board (PCB) temperature.

LA

LA

LAY Y Y Y Y OUT GUIDELINES

LA

LA

The switching regulator is a high di/dt and dv/dt power

circuit. PCB layout is critical. A good layout can achieve

optimum circuit performance with minimized component

stress, resulting in better system reliability. For a multi-

phase voltage regulator, the SC1218 driver, FETs, induc-

tor, and supply decoupling capacitors in each phase have

to be considered as a unit. For the SC1218 driver, the

following guidelines are typically recommended during PCB

layout:

POWER MANAGEMENT

Applications Information (Cont.)

2005 Semtech Corp.

OUT GUIDELINES

OUT GUIDELINES

OUT GUIDELINES

OUT GUIDELINES

er Dissipation and Junction T

er Dissipation and Junction T

er Dissipation and Junction T

er Dissipation and Junction Tem

a) Place the SC1218 close to the FETs for shortest

gate drive traces and ground return paths;

b) Connect decoupling capacitor as close as possible

to the VIN pin and the PGND pin. The trace length of

the capacitor on the VIN pin should be no more than

0.2” (5mm); and

c) Locate the bootstrap capacitor close to the SC1218.

IN

. It is approximated as:

TOTAL

is the total gate charge of the top-side and

Q

, switching frequency F

P

D

=

(

I

Q

+

Q

TOTAL

⋅

F

SW

)

⋅

em

em

em

emperature

V

SW

IN

, and supply volt-

perature

perature

perature

perature

10

The typical layout examples of SC1218 based on above

guidelines are shown in Fig.12 and Fig.13.

1000

1000

Fig. 13. Component placement for MLPQ-8.

Fig. 12. Component placement for SOIC-8

600

600

400

400

200

200

800

800

R

R

C

C

0

0

PWM

PWM

PWM

PWM

VIN

VIN

VIN

VIN

40

40

R

R

VIN

VIN

VIN

VIN

Fig. 11. Power dissipation.

60

60

C

C

VIN

VIN

Fsw=200kHz

Fsw=200kHz

Fsw=200kHz

EN

EN

TOTAL GATE CHARGE (nC)

TOTAL GATE CHARGE (nC)

C

C

C

C

BST

BST

C

C

BST

BST

80

80

Fsw=400kHz

Fsw=400kHz

Fsw=400kHz

www.DataSheet4U.com

To Bottom FET

To Bottom FET

100

100

Fsw=600kHz

Fsw=600kHz

Fsw=600kHz

www.semtech.com

R

R

SC1218

DRN

DRN

To top FET

To top FET

To top FET

To top FET

R

R

To bottom FET

To bottom FET

To bottom FET

To bottom FET

To Top FET

To Top FET

To Phase Node

To Phase Node

DRN

DRN

To phase node

To phase node

120

120