max5259 Maxim Integrated Products, Inc., max5259 Datasheet - Page 15

max5259

Manufacturer Part Number

max5259

Description

+3v/+5v, Low-power, 8-bit Octal Dacs With Rail-to-rail Output Buffers

Manufacturer

Maxim Integrated Products, Inc.

Datasheet

1.MAX5259.pdf

(20 pages)

Available stocks

Company

Part Number

Manufacturer

Quantity

Price

Company:

Part Number:

max5259EEE

Manufacturer:

MAXIM

Quantity:

129

Part Number:

max5259EEE

Manufacturer:

MAXIM/美信

Quantity:

20 000

Company:

Part Number:

max5259EEE+

Manufacturer:

Maxim

Quantity:

4 967

Part Number:

max5259EEE+T

Manufacturer:

MAXIM/美信

Quantity:

20 000

LDAC is typically used in 4-wire interfaces (Figure 4).

This command is level sensitive, and it allows asyn-

chronous hardware control of the DAC outputs. With

LDAC low, all eight DAC registers are transparent, and

any time an input register is updated, the DAC output

immediately follows.

DOUT is the internal shift-register’s output. DOUT can

be programmed to clock out data on the falling edge of

SCLK (mode 0) or the rising edge (mode 1). In mode 0,

output data lags input data by 16.5 clock cycles, main-

taining compatibility with MICROWIRE and SPI. In

mode 1, output data lags input data by 16 clock cycles.

On power-up, DOUT defaults to mode 0 timing. DOUT

never three-states; it always actively drives either high

or low and remains unchanged when CS is high.

The MAX5258/MAX5259 are MICROWIRE (Figure 5)

and SPI/QSPI (Figure 6) compatible. For SPI and QSPI,

clear the CPOL and CPHA configuration bits (CPOL =

CPHA = 0). The SPI/QSPI CPOL = CPHA = 1 configura-

tion can also be used if the DOUT output is ignored.

The MAX5258/MAX5259 can interface with Intel’s

80C5X/80C3X family in mode 0 if the SCLK clock polar-

ity is inverted. Universally, if a serial port is not avail-

able, three lines from one of the parallel ports can be

used for bit manipulation.

Digital feedthrough at the voltage outputs is greatly

minimized by operating the serial clock only to update

the registers. See the Clock Feedthrough photo in the

Typical Operating Characteristics section. The clock

idle state is low.

Any number of MAX5258/MAX5259s can be daisy-

chained by connecting DOUT of one device to DIN of

the following device in the chain with all devices in

mode zero. The NOP instruction (Table 1) allows data

to be passed from DIN to DOUT without changing the

input or DAC registers of the passing device. A 3-wire

interface updates daisy-chained or individual

MAX5258/MAX5259s simultaneously by bringing CS

high (Figure 7).

The MAX5258/MAX5259 use a matrix decoding archi-

tecture for the DACs, which saves power in the overall

system. The external reference voltage is divided down

by a resistor string placed in a matrix fashion. Row and

______________________________________________________________________________________

Interfacing to the Microprocessor

LDAC Operation (Hardware)

+3V/+5V, Low-Power, 8-Bit Octal DAC

Daisy-Chaining Devices

Serial Data Output

Analog Section

DAC Operation

with Rail-to-Rail Output Buffers

column decoders select the appropriate tab from the

resistor string to provide the needed analog voltages.

The resistor string presents a code-independent input

impedance to the reference and guarantees a monoto-

nic output. Figure 8 shows a simplified diagram of one

of the eight DACs.

The voltage at REF sets the full-scale output voltage for

all eight DACs. The 230kΩ typical input impedance at

REF is code independent. The output voltage for any

DAC can be represented by a digitally programmable

voltage source as follows:

where NB is the numerical value of the DAC’s binary

input code.

All MAX5258/MAX5259 voltage outputs are internally

buffered by precision unity-gain followers that slew at

about 0.55V/µs. The outputs can swing from GND to

V

the amplifier outputs will typically settle to 1/2LSB in

10µs when loaded with 10kΩ in parallel with 100pF.

The buffer amplifiers are stable with any combination of

resistive (≥10kΩ) or capacitive (≤100pF) loads.

The output buffer can have a negative input offset volt-

age that would normally drive the output negative, but

since there is no negative supply, the output remains at

GND (Figure 9). When linearity is determined using the

endpoint method, it is measured between code 10 (0A

hex) and full-scale code (FF hex) after offset and gain

error are calibrated out. With a single-supply, negative

offset causes the output not to change with an input

code transition near zero (Figure 9). Thus, the lowest

code that produces a positive output is the lower end-

point.

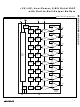

Figure 3. Serial Input Format

DD

. With a 0 to V

DOUT

THIS IS THE FIRST BIT SHIFTED IN

DAC Linearity and Voltage Offset

X X A2 A1 A0 C2 C1 C0 D7 D6 . . . D1 D0

V

OUT

Applications Information

CONTROL AND

ADDRESS BITS

REF

= (NB

(or V

✕

REF

V

Output Buffer Amplifiers

MSB

REF

8-BIT DAC DATA

to 0) output transition,

) / 256,

Reference Input

LSB

DIN

15