uda1380 NXP Semiconductors, uda1380 Datasheet

uda1380

Available stocks

Related parts for uda1380

uda1380 Summary of contents

Page 1

... DATA SHEET UDA1380 Stereo audio coder-decoder for MD, CD and MP3 Product specification Supersedes data of 2003 Apr 04 INTEGRATED CIRCUITS 2004 Apr 22 ...

Page 2

... TIMING 19 APPLICATION INFORMATION 20 PACKAGE OUTLINES 21 SOLDERING 21.1 Introduction to soldering surface mount packages 21.2 Reflow soldering 21.3 Wave soldering 21.4 Manual soldering 21.5 Suitability of surface mount IC packages for wave and reflow soldering methods 22 DATA SHEET STATUS 23 DEFINITIONS 24 DISCLAIMERS 25 PURCHASE OF PHILIPS I 2 Product specification UDA1380 2 C COMPONENTS ...

Page 3

... LNA with 29 dB fixed gain for mono microphone input, including VGA with gain from steps Digital left and right independent volume control and mute from + steps of 0.5 dB. load. The 2 C-bus interface 3 Product specification UDA1380 ...

Page 4

... The term ‘UDA1380’ in this document refers to both UDA1380TT and UDA1380HN, unless particularly specified. The front-end of the UDA1380 is equipped with a stereo line input, which has a PGA control, and a mono microphone input with an LNA and a VGA. The digital decimation filter is equipped with an AGC which can be used in case of voice-recording ...

Page 5

... FSDAC, AVC (with headphone); no signal kHz s Power-down mode kHz s 5 Product specification UDA1380 MIN. TYP. MAX. 2.4 3.0 3.6 2.4 3.0 3.6 2.4 3.0 3.6 2.4 3.0 3.6 4.5 7.0 3.3 1.0 3.4 0.1 ...

Page 6

... A-weighted dB; A-weighted = 48 kHz s 6 Product specification MIN. TYP. = 1 100 0 100 150 80 28 UDA1380 MAX. UNIT 0.5 dBFS ...

Page 7

... Product specification MIN. TYP note REF(HP UDA1380 MAX. UNIT VERSION SOT487-1 SOT617-1 ...

Page 8

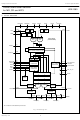

... SYSCLK 9 (5) DATAO 7 (3) BCKO 8 (4) WSO 10 (6) BCKI 11 (7) WSI 12 (8) DATAI WSPLL 27 (23) VOUTL Pin numbers for UDA1380HN in parentheses. 2004 Apr 22 V SSA(AD) V ADCP V ADCN V REF 30 (26) 4 (32) 2 (30) SDC PGA SDC PGA SDC n.c. ADC ADC DECIMATION FILTER ...

Page 9

... Product specification UDA1380 DESCRIPTION ADC input right, also connected to the mixer input of the FSDAC ADC reference voltage microphone input ADC reference voltage pin RESET with pull-down, for making Power-On Reset (POR) ...

Page 10

... ADC analog supply voltage terminal 1 index area 1 RESET V 2 DDD BCKO 3 4 WSO UDA1380HN DATAO 5 BCKI 6 7 WSI DATAI 8 Transparent top view Fig.3 Pin configuration UDA1380HN. Product specification UDA1380 24 V SSA(DA) 23 VOUTL 22 V DDA(DA) 21 VOUTR 20 V DDA(HP) 19 VOUTLHP 18 V REF(HP) 17 ...

Page 11

... REQUIREMENTS and 128f signals for the FSDAC and s s C-bus. 2 C-bus register. WSI DIV1 128f s (digital parts) 256f s (ADC and FSDAC) Fig.4 WSPLL set-up. VCO FREQUENCY DIV1 1536 1536 1536 768 Product specification UDA1380 VCO PRE1 MGU527 (MHz 153 ...

Page 12

... For power saving reasons each clock signal inside the system must be controlled and enabled via a separate bit in the 2 L3-bus and I C-bus registers (ADC_CLK). The DAC part of the UDA1380 can operate from 8 to 100 kHz sampling frequency (f the ADC part can run from kHz. handbook, full pagewidth SYSCLK WSI Fig ...

Page 13

... Stereo audio coder-decoder for MD, CD and MP3 8.2 ADC analog front-end The analog front-end of the UDA1380 consists of one stereo ADC with a selector in front of it (see Fig.6). Using this selector one can either select the microphone input with the microphone amplifier (LNA) with a fixed 29 dB ...

Page 14

... Dynamic range Digital output level 8.3.1 The UDA1380 is equipped with an overload detector which can be read out from the L3-bus practice the output is used to indicate whenever the output data, in either the output of the left or right channel, exceeds 1 dB (the actual figure is 1.16 dB) of the maximum possible digital swing ...

Page 15

... This is for preventing out-of-band noise from the noise shaper to move into the audio band 5th-order noise shaper is normally used at higher sampling frequencies, normally from 32 to 100 kHz. Product specification UDA1380 = 3 kHz, assuming c = 300 Hz, assuming c 2 ...

Page 16

... In schematic form this is given in Fig.9. This mixer input can be used for instance for mixing-in a GSM signal signal directly to the line output. In the UDA1380, the mixer input is connected from the ADC line input via an AVC unit. Remark: Before the AVC unit can be used stand-alone, ...

Page 17

... I S-BUS OUTPUT BLOCK Fig.10 Digital mixer (DAC). PON_AVC RESISTOR NETWORK 2 AVC[5: C-bus control bits Fig.11 Analog mixer configuration. 17 Product specification UDA1380 mixing after sound features master 2f s VOLUME INTERPOLATION AND FILTER MUTE to FSDAC mixer input enable mixer (EN_AVC) ...

Page 18

... L3DATA/SDA L3DATA 2 Remark: In the I C-bus mode there is a bit A1 which sets the LSB bit of the address of the UDA1380. In L3-bus mode this bit is not available, meaning the device has only one L3-bus device address. 8.10 Power-on reset The UDA1380 has a dedicated reset pin, which has a pull-down resistor ...

Page 19

... VINL (27) 3 VINM (31) Pin numbers for UDA1380HN in parentheses. 8.11.2 FSDAC POWER CONTROL The FSDAC block has power-on pins: one of which shuts down the DAC itself, but leaves the output still at V voltage (which is half the power supply). This function is set by the bit PON_DAC in the L3-bus or I ...

Page 20

... In slave mode the signals on pins BCKO, WSO and SYSCLK must be applied from the application (signals must be in frequency lock) and the UDA1380 returns the DATAO signal from the decimator. The applied signal from pin BCKO can be for instance: 32f ...

Page 21

Acrobat reader. white to force landscape pages to be ... LEFT BCK DATA MSB B2 MSB 2 ...

Page 22

... Bits called Data Operation Mode, or DOM bits, represent the type of data transfer according to Table 6. 9.3 Slave address The UDA1380 acts as a slave receiver or a slave transmitter. Therefore the signals L3CLOCK and L3MODE are only input signals. The data signal L3DATA is a bidirectional line. The UDA1380 slave address is shown in Table 7 ...

Page 23

... The ‘11’ indicates that the device must write data to the microcontroller, then the microcontroller frees the L3DATA-bus so the UDA1380 can send the register address byte and its two-byte contents The device now writes the requested register address ...

Page 24

... Data transfer 1; register address note 3 Data transfer 2; MS data byte note 3 Data transfer 3; LS data byte note 3 Notes 1. First bit in time. 2. Last bit in time. 3. Data transfer from the UDA1380 to the microcontroller. 2004 Apr 22 ( ...

Page 25

Acrobat reader. white to force landscape pages to be ... L3CLOCK L3MODE device address L3DATA 0 1 DOM bits L3CLOCK L3MODE device address register ...

Page 26

... A0] 00110(A1)0, with bit A1 as the address selection bit (two addresses possible). 2004 Apr 22 10.1.1 The UDA1380 acts as either a slave receiver or a slave transmitter. Therefore the clock signal SCL is only an input signal. The data signal SDA is a bidirectional line. Table 11 shows the device address of the UDA1380. ...

Page 27

... The microcontroller sends two bytes of data with the Most Significant (MS) byte first, followed by the Least Significant (LS) byte; after each byte the UDA1380 asserts an acknowledge (A). 7. After each pair of bytes transmitted, the register address is auto-incremented; after each byte the UDA1380 asserts an acknowledge (A ...

Page 28

... The microcontroller generates the device address ‘00110A 8. The UDA1380 asserts an acknowledge (A). 9. The UDA1380 sends two bytes of data with the Most Significant (MS) byte first, followed by the Least Significant (LS) byte; after each byte the microcontroller asserts an acknowledge (A). 10. After each pair of bytes transmitted, the register address is auto-incremented; after each byte the microcontroller asserts an acknowledge (A). ...

Page 29

... AGC settings Software reset 7FH restore L3-default values Table 16 Register map of status bits (read-out) REGISTER ADDRESS Headphone driver and interpolation filter 18H interpolation filter status Decimator 28H decimator status 2004 Apr 22 FUNCTION 2 C-bus clock itself) interpolator clock) s FUNCTION 29 Product specification UDA1380 ...

Page 30

... Evaluation bits. Bits EV2, EV1 and EV0 are special control bits for manufacturer’s evaluation and must always be kept at their default values for normal operation of UDA1380; default value 000. default value 0 ADC clock enable. A 1-bit value to enable the system clock (from SYSCLK input) to the analog part of the ADC ...

Page 31

... These set the proper divider setting for the WSPLL. The input is the WSI signal, the output inside the 128f value 10, see Table 20. INPUT CLOCK ON PIN SYSCLK 256f INPUT FREQUENCY RANGE (kHz) ON PIN WSI (default) 31 Product specification UDA1380 clock will be generated s clock is needed for clocking the s and a 256f clock. Default s s ...

Page 32

... BCKO is 64f s s SERIAL_FORMAT_DAI 2 I S-bus (default) LSB-justified, 16 bits LSB-justified, 18 bits LSB-justified, 20 bits MSB-justified 2 not used: mapped to I S-bus Product specification UDA1380 9 8 SFORI0 SFORO0 48f , mode is selected s ...

Page 33

... S-bus (default) LSB-justified, 16 bits LSB-justified, 18 bits LSB-justified, 20 bits LSB-justified, 24 bits MSB-justified 2 S-bus 11 10 PON_DAC PON_ PON_ PON_ PGAL ADCL PGAR 0 0 DESCRIPTION (half the power supply REF UDA1380 9 8 PON_ BIAS PON_ ADCR 0 0 ...

Page 34

... When this bit is logic 0: right PGA is powered-off; when this bit is logic 1: right PGA is powered-on. Default value 0. Power-on ADCR. A 1-bit value to have power-on control for the ADC right. When this bit is logic 0: right ADC is powered-off; when this bit is logic 1: right ADC is powered-on. Default value 0. 34 Product specification UDA1380 ...

Page 35

... FM tuner (RMS) needed to drive the headphone driver full-swing. Default value 111111, see Table 29. 35 Product specification AVCL3 AVCL2 AVCL1 AVCR3 AVCR2 AVCR1 DESCRIPTION dB in steps of 1.5 dB. The dB in steps of 1.5 dB. The UDA1380 8 AVCL0 1 0 AVCR0 1 ...

Page 36

... Bits RSV12, RSV11, RSV10, RSV02, RSV01, and RSV00 are special control bits for manufacturer’s evaluation and must always be kept at their default values for normal operation of UDA1380. Table 30 Register address 04H ...

Page 37

... MVCL_1 DESCRIPTION dB in steps steps of MVCR_1 MVCR_0 VOLUME (dB) MVCL_1 MVCL_0 UDA1380 8 MVCR_0 0 0 MVCL_0 0 0 (default) 0.25 0.50 0. 51.25 51.50 51. ...

Page 38

... VC2_2 VC2_1 VC2_0 VC1_2 VC1_1 VC1_0 UDA1380 8 VC2_0 1 0 VC1_0 0 VOLUME (dB) 0 0.25 0.50 0. 45.25 45.50 45. ...

Page 39

... TRR1 TRR0 VC2_2 VC2_1 VC2_0 VC1_2 VC1_1 VC1_0 BBL3 BBL2 BBL1 BBR3 BBR2 BBR1 0 0 DESCRIPTION Mode flat (default) minimum minimum maximum Product specification UDA1380 VOLUME (dB BBL0 BBR0 0 0 ...

Page 40

... Product specification UDA1380 MINIMUM SET MAXIMUM (dB) (dB) SET (dB) 0 (default) 0 (default MINIMUM SET MAXIMUM (dB) (dB) SET (dB) 0 (default) 0 (default ...

Page 41

... Channel 1 mute. A 1-bit value to enable the digital mute for channel 1. When this bit is logic 0: no soft mute of channel 1. When this bit is logic 1: soft mute of channel 1. Default value 0. De-emphasis. A 3-bit value to enable the digital de-emphasis filter for channel 1. Default value 000, see Table 45. 41 Product specification UDA1380 MT2 DE2_2 DE2_1 ...

Page 42

... Default value 00, see Table 49. default value 00 Oversampling input settings. A 2-bit value to select the oversampling input mode. Default value 00, see Table 50. 42 Product specification MIX DESCRIPTION UDA1380 OS1 OS0 0 0 ...

Page 43

... The ranges are +24 to 63.5 dB and steps of 0.5 dB. The default setting (value 00000000), see Table 53. 43 Product specification FUNCTION FUNCTION FUNCTION ML_DEC3 ML_DEC2 ML_DEC1 DESCRIPTION UDA1380 dB 8 ML_DEC0 steps dB in ...

Page 44

... PGA_GAIN PGA_GAIN CTRLR2 CTRLR1 PGA_GAIN PGA_GAIN CTRLL2 CTRLL1 0 0 DESCRIPTION UDA1380 GAIN (dB 0.5 0 (default) 0 62.5 63 63.5 8 PGA_GAIN CTRLR0 0 0 PGA_GAIN CTRLL0 0 ...

Page 45

... The range steps of 2 dB. Default value 0000, see Table 59. 45 Product specification DESCRIPTION PGA_GAINCTRLR0 PGA_GAIN (dB) PGA_GAINCTRLL0 VGA_CTRL1 SEL_MIC SKIP_DCFIL 0 1 DESCRIPTION UDA1380 0 (default VGA_CTRL0 0 0 EN_DCFIL 0 ...

Page 46

... VGA_CTRL1 Product specification DESCRIPTION VGA_CTRL0 LNA GAIN (dB UDA1380 0 (default ...

Page 47

... AGC_TIME2 AGC_TIME1 AGC_LEVEL0 0 0 DESCRIPTION AGC SETTING 8 kHz SAMPLING DECAY TIME ATTACK TIME (ms) (ms) 100 61 100 88.2 200 61 200 88.2 200 116 400 61 400 88.2 400 116 UDA1380 8 AGC_TIME0 0 0 AGC_EN 0 DECAY TIME (ms) 551 (default) 551 1102 1102 1102 2205 2205 2205 ...

Page 48

... When this bit is logic 1: interpolator on channel 2 left input has detected silence. 48 AGC TARGET LEVEL VALUE (dBFS) 5.5 (default HP_STCTV HP_STCTL MUTE_ MUTE_ STATE_M STATE_CH2 DESCRIPTION Product specification UDA1380 HP_STCTR 0 MUTE_ STATE_CH1 ...

Page 49

... Digital output overflow detection. A 1-bit value which signals whether the digital output amplitude exceeds 1. not. When this bit is logic 0: no overflow detected (read-out). When this bit is logic 1: overflow detected (read-out). 49 Product specification UDA1380 DESCRIPTION MT_ADC_STAT ...

Page 50

... T = 125 3.6 V amb note 4 amb DD output short-circuited to V SSA(DA) output short-circuited to V DDA(DA) CONDITIONS in free air 50 Product specification UDA1380 MIN. MAX. UNIT 4 V 150 C 65 +125 C 40 +85 C 2000 +2000 V 200 +200 V 100 ...

Page 51

... FSDAC, AVC (with headphone); no signal kHz s Power-down mode kHz s 51 Product specification UDA1380 MIN. TYP. MAX. 2.4 3.0 3.6 2.4 3.0 3.6 2.4 3.0 3.6 2.4 3.0 3.6 4.5 7.0 3.3 1.0 3.4 0.1 0.9 ...

Page 52

... Power-down mode resistor must be connected in series with the DAC output in 52 Product specification UDA1380 MIN. TYP. MAX. 2.0 5.5 0.5 +0 0.85V DDD 0 ...

Page 53

... A-weighted kHz; ripple (p-p) ripple 53 Product specification UDA1380 = all voltages measured with L MIN. TYP. MAX. = 1 708 mV 1 501 mV 1 354 mV 1 252 mV 1 ...

Page 54

... REF(HP decoupling capacitors; note single-ended L application with DC decoupling capacitors (100 F typical single-ended L application with DC decoupling capacitors (100 F typical) code = 0; A-weighted 54 Product specification UDA1380 MIN. TYP. MAX. UNIT 0.9 V <0 ...

Page 55

... DAC and the headphone output to less than -2 dB, otherwise clipping may occur. 3. Channel separation performance is measured at the IC pin. 2004 Apr 22 CONDITIONS dB; A-weighted A-weighted i 55 Product specification UDA1380 MIN. TYP. MAX. UNIT 150 ...

Page 56

... MHz sys f 19.2 MHz sys f < 19.2 MHz sys f 19.2 MHz sys note 3 note 3 note 4 note 4 note 4 56 Product specification UDA1380 MIN. TYP. MAX 250 23 54 170 17 41 130 0.3T 0.7T sys sys 0.4T 0.6T sys sys 0.3T 0.7T sys sys ...

Page 57

... To be suppressed by the input filter. 2004 Apr 22 CONDITIONS MIN. 190 190 1.3 0.6 note 0.1C b note 0.1C b note 6 0.6 0.6 0.6 1.3 100 0 note Product specification UDA1380 TYP. MAX. UNIT 400 kHz s s 300 ns 300 400 pF 1 cycle ...

Page 58

... WS t BCKH t r BCK T cy(BCK) DATAO DATAI 2004 Apr 22 t CWL T sys Fig.16 Timing of system clock. t h(WS su(WS) t BCKL t d(DATAO-WS) Fig.17 Serial interface input data timing. 58 Product specification UDA1380 MGR984 t d(DATAO-BCK) t h(DATAO) t su(DATAI) t h(DATAI) MGS756 ...

Page 59

... Fig.19 Timing of data transfer mode for write and read. 2004 Apr 22 t CLK(L3)L t CLK(L3)H t su(L3)A t su(L3)DA t h(L3)DA BIT 0 Fig.18 Timing of address mode. t CLK(L3)L t CLK(L3)H t su(L3)DA t h(L3)DA BIT 0 59 Product specification t su(L3)A t h(L3)A T cy(CLK)(L3) BIT 7 t stp(L3) t h(L3)D T cy(CLK)L3 BIT 7 t dis(L3)R t d(L3)R MGU015 UDA1380 MGL723 ...

Page 60

Acrobat reader. white to force landscape pages to be ... SDA t BUF t LOW t r SCL t HD;STA t HD;DAT P S ...

Page 61

... micro- phone input (16 V) L3DATA/SDA L3CLOCK/SCL L3MODE SEL_L3_IIC SYSCLK system clock 47 DATAI RTCB Pin numbers for UDA1380HN in parentheses. 2004 Apr 22 V DDA V DDA V DDA V DDD 100 100 F (16 V) 100 F 100 nF (63 V) (16 V) 100 nF 100 F ( ADCN ...

Page 62

... Apr 2.5 scale (1) ( 0.30 0.20 11.1 6.2 8.3 0.65 0.19 0.09 10.9 6.0 7.9 REFERENCES JEDEC JEITA MO-153 62 Product specification detail 0.75 0.78 1 0.2 0.1 0.1 0.50 0.48 EUROPEAN PROJECTION UDA1380 SOT487 ISSUE DATE 99-12-27 03-02-18 ...

Page 63

... 1 2.5 scale (1) ( 5.1 3.25 5.1 3.25 3.5 0.5 4.9 2.95 4.9 2.95 REFERENCES JEDEC JEITA MO-220 - - - detail 0.5 3.5 0.05 0.1 0.1 0.05 0.3 EUROPEAN PROJECTION Product specification UDA1380 SOT617 ISSUE DATE 01-08-08 02-10-18 ...

Page 64

... Use a low voltage ( less) soldering iron applied to the flat part of the lead. Contact time must be limited to 10 seconds 300 C. When using a dedicated tool, all other leads can be soldered in one operation within seconds between 270 and 320 C. 64 Product specification UDA1380 ...

Page 65

... However, the image sensor package can be mounted by the client on a flex foil by using a hot bar soldering process. The appropriate soldering profile can be provided on request. 9. Hot bar or manual soldering is suitable for PMFP packages. 2004 Apr 22 (1) (3) , TFBGA, (8) 65 Product specification UDA1380 SOLDERING METHOD WAVE REFLOW not suitable suitable (4) not suitable suitable suitable ...

Page 66

... Product specification UDA1380 DEFINITION These products are not Philips Semiconductors ...

Page 67

... Philips. This specification can be ordered using the code 9398 393 40011. 2004 Apr 22 C COMPONENTS 2 C components conveys a license under the Philips’ system provided the system conforms to the I 67 Product specification UDA1380 2 C patent to use the 2 C specification defined by ...

Page 68

Philips Semiconductors – a worldwide company Contact information For additional information please visit http://www.semiconductors.philips.com. For sales offices addresses send e-mail to: sales.addresses@www.semiconductors.philips.com. © Koninklijke Philips Electronics N.V. 2004 All rights are reserved. Reproduction in whole or in part is prohibited ...