at83c24nds-tisum ATMEL Corporation, at83c24nds-tisum Datasheet

at83c24nds-tisum

Related parts for at83c24nds-tisum

at83c24nds-tisum Summary of contents

Page 1

... A sophisticated protection system guar- antees timely and controlled shutdown upon error conditions. The AT83C24NDS is a dedicated version approved by NDS for use with NDS Video- Guard conditional access software in set-top boxes. All AT83C24 datasheet is applicable to AT83C24NDS. The main differences between AT83C24 and AT83C24NDS are listed below: 1/ CLASS A card supplied with CVCC = 4 ...

Page 2

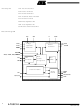

Acronyms TWI: Two-wire Interface POR: Power On Reset PFD: Power Fail Detect ART: Automatic Reset Transition ATR: Answer To Reset MSB: Most Significant Bit LSB: Least Significant bit SCIB: Smart Card Interface Bus Block Diagram DVCC EVCC RESET PRES/ INT ...

Page 3

... QFN28 pinout CMDVCC VSS QFN 28 CVSS 4 TOP VIEW / CVCC CVCCin AT83C24 and for AT83C24NDS AT83C24 23 22 EVCC / /RST 18 / SCL 16 SDA ...

Page 4

Table 1. Ports Description (Continued) Pad Name Pad Internal Power Supply SDA VCC SCL VCC I/O EVCC C4 EVCC C8 EVCC CLK EVCC CIO CVCC CC4 CVCC CC8 CVCC CPRES VCC CCLK CVCC CRST CVCC CMDVCC EVCC VCC LI AT83C24 ...

Page 5

Table 1. Ports Description (Continued) Pad Name Pad Internal Power Supply CVCC CVCCin DVCC EVCC CVSS VSS Note: 4234F–SCR–10/05 ESD Pad Limits Type Description Card Supply Voltage 8 kV+ PWR CVCC is the programmable voltage output for the Card interface. ...

Page 6

Operational Modes TWI Bus Control The Atmel Two-wire Interface (TWI) interconnects components on a unique two-wire bus, made up of one clock line and one data line with speeds 400 Kbits per second, based on a byte-oriented ...

Page 7

Address Byte The first byte to send to the device is the address byte. The device controls if the hardware address (A2/CK, A1/RST, A0/3V pins on reset) corresponds to the address given in the address byte (A2, A1, A0 bits). ...

Page 8

Write Commands The write commands are: 1. Reset: Initializes all the logic and the TWI interface as after a power-up or power-fail reset smart card is active when RESET falls, a deactivation sequence is performed. This is a ...

Page 9

Read Command After the slave address has been configured, the read command allows to read one or several bytes in the following order: • STATUS, CONFIG0, CONFIG1, CONFIG2, CONFIG3, INTERFACE, TIMER1, TIMER0, CAPTURE1, CAPTURE0 • FFh is completing the transfer ...

Page 10

Card Presence Detection The card presence is provided by the CPRES pin. The polarity of card presence contact is selected with the CARDDET bit (see CONFIG1 register). A programmable filtering is controlled with the CDS[2-0] bits (see CONFIG1 ...

Page 11

CIO, CC4, CC8 Controller The CIO, CC4, CC8 output pins are driven respectively by CARDIO, CARDC4, CARDC8 bits values or by I/O, C4, C8 signal pins. This selection depends of the IODIS bit value. If IODIS is reset, data are ...

Page 12

Figure 6. Clock Block Diagram with Software Activation (see page 14) Figure 7. Clock Block Diagram with Hardware Activation (see page 14) CMDVCC CRST Controller The CRST output pin is driven by the A1/RST pin signal pin or by the ...

Page 13

Figure 8. CRST Block Diagram with soft activation Figure 9. CRST Block Diagram with Hardware Activation (CMDVCC pin used) CMDVCC 4234F–SCR–10/05 CARDRST bit tb delay see Fig 12 CARDRST bit A1/RST CRST_SEL bit = 1 CMDVCC ART ...

Page 14

Activation Sequence Hardware Activation (DC/DC started with CMDVCC) Initial conditions: CARDDET bit must be configured in accordance to the smart card connector polarity. IT_SEL bit, CRST_SEL bit (see CONFIG4 register) must be set and CARDRST bit (see INTER- FACE register) ...

Page 15

Software Activation (DC/DC Started With Writing in VCARD[1:0] bits) and ART bit = 1 Initial conditions: CARDRST bit = 0, CKSTOP bit =1, IODIS bit = 1. The following sequence can be applied: 1. Card Voltage is set by software ...

Page 16

ISO 7816 constraints 200 card clock cycles Note: Software Activation (DC/DC Started by Writing in VCARD[1:0] bits) and ART bit = 0 The activation sequence is controlled by software using TWI commands, depending on the cards to support. ...

Page 17

VCARDERR bit is set by hardware (or by software) • INSERT is set and CARDIN is cleared (card extraction) • SHUTDOWN is set by software • CMDVCC goes from Low to High • Power fail on VCC (see POWERMON ...

Page 18

Figure 14. Transparent Mode Description Microcontroller Power Modes Two power-down modes are available to reduce the AT83C24 power consumption (see STUT- DOWN bit in CONFIG1 register and LP bits in CONFIG3 register). To enter in the mode number 4 (see ...

Page 19

Power Monitoring The AT83C24 needs only one power supply to run: VCC. If the microcontroller outputs signals with a different electrical level, the host positive supply is connected to EVCC. EVCC and VCC pins can be connected together if they ...

Page 20

Registers Table 6. CONFIG0 (Config Byte 0) Number AT83C24 ATRERR Bit Bit Mnemonic Description 7-6 1-0 These bits cannot be programmed and are read as 1-0. Answer to Reset Interrupt This bit is set ...

Page 21

Table 7. CONFIG 1 (Config Byte 1) 4234F–SCR–10/ ART SHUTDOWN Bit Bit Number Mnemonic Description 7 X This bit should not be set. Automatic Reset Transition Set this bit to have the CRST pin changed according ...

Page 22

Table 8. CONFIG2 (Config Byte 2) Number Notes: AT83C24 DCK2 DCK1 Bit Bit Mnemonic Description 7 X This bit should not be set. DC/DC Clock prescaler factor DCCLK is the DC/DC clock the ...

Page 23

Table 9. CONFIG3 (Config Byte 3) 4234F–SCR–10/ EAUTO VEXT1 VEXT0 Bit Bit Number Mnemonic Description EVCC voltage configuration: EAUTO VEXT1 VEXT0 EAUTO 0 1 7-5 VEXT1 1 X VEXT0 if EVCC ...

Page 24

Table 10. CONFIG4 (Config Byte Bit Number Bit Mnemonic Description 7-5 X-X-X These bits should not be set. Step Regulator mode Clear this bit to enable the automatic step-up converter (CVCC is stable even if ...

Page 25

Table 11. INTERFACE (Interface Byte IODIS Bit Number Bit Mnemonic Description 7 0 This bit should not be set. Card I/O isolation Set this bit to drive the CIO, CC4, CC8 pins according to CARDIO, CARDC4, CARDC8 ...

Page 26

Table 12. STATUS (Status Byte) Bit Number Table 13. TIMER 1 (Timer MSB) Number Reset value = 0x00000001 AT83C24 CC8 CC4 CARDIN Bit Mnemonic Description Card CC8 7 CC8 This bit provides the actual level on ...

Page 27

Table 14. TIMER 0 (Timer LSB) Reset value = 0x10010000 Table 15. CAPTURE 1 (Capture MSB) Reset value = 0x00000000 Table 16. CAPTURE 0 (Capture LSB) Reset value = 0x00000000 4234F–SCR–10/ Bit 7 Bit 6 Bit 5 ...

Page 28

... EVCC connected to host power supply: from 1.6V to 5.5V -40°C to +85° CLASS A card supplied with CVCC = 4.75 to 5.25V for AT83C24NDS CLASS A card supplied with CVCC = 4.6 to 5.25V for AT83C24 CLASS B card supplied with CVCC = 2.8V to 3.2V CLASS C card supplied with CVCC = 1.68V to 1.92V Table 17. Core (VCC) ...

Page 29

... PRES/INT weak pull-up output current PRES/INT EVCC EVCC pin not connected to a power supply EVCC EVCC pin connected to a power supply CLK Clock signal for AT83C24 CLK Clock signal for AT83C24NDS Table 19. Host Interface (SCL, SDA, RESET) Symbol Parameter V Input Low-voltage IL V Input High Voltage ...

Page 30

... Unit Test Conditions 0 < Icard < 60mA C =10µF L for AT83C24 mV 0 < Icard < 65mA C = 3.3µF L for AT83C24NDS Max. charge 40 nA.s V Max. duration 400 ns Max. Icard variation 200 mA V AT83C24 V AT83C24NDS > V Icard = 0, VCC PFDP μ 3.3 F Icard = 0 μs L μ ...

Page 31

Table 21. Smart Card Class B Symbol Parameter T CVCC 0 to Valid VLH Notes: 1. Capacitor: X7R type or X5R type, max ESR value is 30mΩ (100kHz-100MHz), Replacing 3.3µF by 2.2µF in parrallel with 1µF is better for ESR ...

Page 32

Table 23. Smart Card Clock (CCLK pin) (Continued) Symbol Parameter Rise and Fall Slew rate Low level voltage stability (taking into account PCB design) High level voltage stability (taking into account PCB design) CCLK Smart card clock frequency Table 24. ...

Page 33

Table 25. Smart Card RST (CRST pin) Symbol Parameter V Output Low-voltage OL V Output High Voltage OH I Output High Current Rise and Fall time R F Low level voltage stability (taking into account PCB design) ...

Page 34

Typical Application Figure 1. Typical Standard Mode Application Diagram for 3 AT83C24 ( AT83C24 if needed) EVCC Host MICROCONTROLLER XTAL1 XTAL2 MHz VSS VSS Note: 1. The external resistor on I/O can be removed if ...

Page 35

...

Page 36

... Typical NDS Application Figure 2. Typical NDS Standard Mode Application Diagram for 1 AT83C24NDS. EVCC Host MICROCONTROLLER XTAL1 XTAL2 18.432 or 27MHz VSS VSS Note: AT83C24 36 See note VCC See note1 for I/O pull up SDA, Reset SCL pullup pullups TWI RST INT0 Px.y Px.y Px.y Px.y 1. The external resistor on I/O can be removed if the host pin has an internal resistor. ...

Page 37

... AT83C24B-TISIL AT83C24B-TIRIL AT83C24B-TISIM AT83C24B-TIRIM AT83C24NDS-PRTIL AT83C24NDS-PRRIL AT83C24NDS-PRTIM AT83C24NDS-PRRIM AT83C24NDS-TISIL AT83C24NDS-TIRIL AT83C24NDS-TISIM AT83C24NDS-TIRIM AT83C24B-PRTUL AT83C24B-PRRUL AT83C24B-PRTUM AT83C24B-PRRUM AT83C24B-TISUL AT83C24B-TIRUL AT83C24B-TISUM AT83C24B-TIRUM AT83C24NDS-PRTUL AT83C24NDS-PRRUL AT83C24NDS-PRTUM AT83C24NDS-PRRUM 4234F–SCR–10/05 Supply Voltage Temperature Range ( 5.5V Industrial ( 5.5V Industrial (2) 4.00V to 5.5V Industrial (2) 4.00V to 5.5V Industrial 3V to 5.5V Industrial ...

Page 38

... Part Number AT83C24NDS-TISUL AT83C24NDS-TIRUL AT83C24NDS-TISUM AT83C24NDS-TIRUM Note: 1. Enhanced AC/DC parameters, see first page for differences between AT83C24 and AT83C24NDS. 2. Refer to index mark for proper placement. AT83C24 38 Supply Voltage Temperature Range ( 5.5V Industrial & Green ( 5.5V Industrial & Green (1) 4.00V to 5.5V Industrial & Green (1) 4 ...

Page 39

Package Drawings QFN28 4234F–SCR–10/05 AT83C24 39 ...

Page 40

SO28 ...

Page 41

... New conditions for hardware activation (see IT_SEL). 5. SO28 drawing package (error with SO32). 6. Adjusted electrical parameters for NDS compliance, pages 28, 29, 30. Changes from 1. QFN28 new package drawing. 4234D-04/ Clock input parameters for AT83C24 and AT83C24NDS. 4234E - 09/04 Changes from 1. Updated green product ordering information. 4234E - 09/04 to 4234F - 10/05 4234F– ...

Page 42

... Unless specifically provided otherwise, Atmel products are not suitable for, and shall not be used in, automotive applications. Atmel’s products are not intended, authorized, or warranted for useas components in applications intended to support or sustainlife. © Atmel Corporation 2005. All rights reserved. Atmel are the trademarks of Atmel Corporation or its subsidiaries. Other terms and product names may be trademarks of others. Atmel Operations Memory ...